Изобретение относится к области автоматики н вычислительной техники и может быть использовано для проверки преобразователей угол - код.

Известны устройства для автоматического определения ошибки преобразователя угол - код, содержащие последовательно соединенные генератор cтaбИv ьнoй частоты, счетчик импульсов, первый клапан, сумматор, второй клапан, схему памяти ошибки, первый дешифратор, схему индикацнн н последовательно соединенные привод постоянной скорости, преобразователь, схему преобразования кода преобразователя в натуральный двоичный параллельный код, второй дешифратор, триггер.

Недостатком известных устройств являются малые пределы определения ошибки преобразователя.

С целью расширения пределов определения ошибки преобразователя, в нем установлены схема «ИЛИ, первая схема задержки, третий клапан, вторая схема задержки, схема памяти эталонного кода, третья схема задержки, причем вход схемы «ИЛИ подключен к выходу схемы преобразования кода преобразователя в натуральный двоичный параллельный код, а выход соединен со вторым входом триггера, со входами первой и второй схем задержки, выход первой схемы задержки соединен с nepiBbiiM входом Т1ретьего

клапана, второй вход которого подключен к выходу схемы паадягги эталонного кода, а выход соединен со вторьим входом сумматора, пе рвый выход второй схемы задержки подключен

ко второму входу второго клапана, а второй соединен со входом третьей схемы задержки, выход которой подключен к перво му входу триггера.

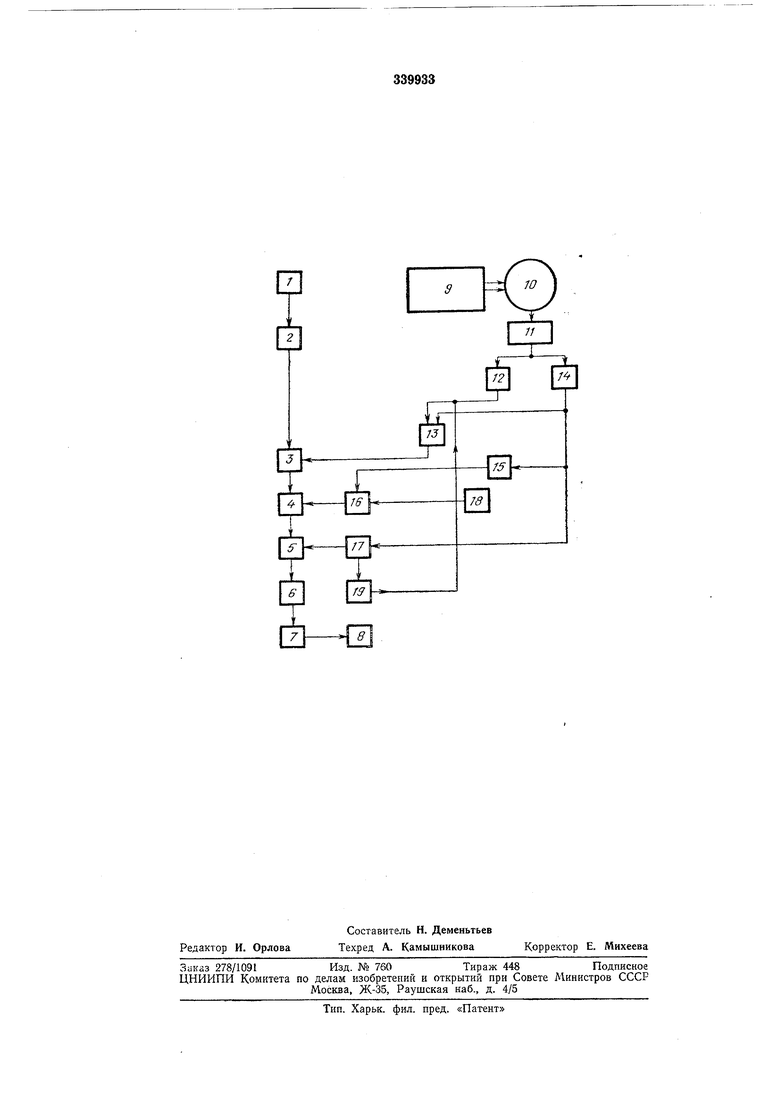

На чертеже приведена функциональная

схема устройства.

Предлагаемое устройство содержит генератор / стабильной частоты, счетчик 2 импульсов, первый клапан 3, сумматор 4, второй клапан 5, схему 6 памяти ошибки, первый дешифратор 7, схему 8 индикации, привод 9 постоянной скорости, преобразователь W, схему 11 преобразования кода преобразователя в натуральный двоичный потепциальный параллельный код, второй дешифратор 12, триггер

}3, схему «ИЛИ 14, первую схему задержки 15, третий клапан 16, вторую схему задержки 17, схему 18 памяти эталонного кода, третью схему задержки 19.

Процесс измерения начинается с моментя

срабатывания дешифратора 12 при появлении в выходном коде «1 п младшем разряде и нулей во всех остальных разрядах. При этом триггер 13 перебрасывается в такое положение, при котором открывается клапан 3, и импульсы с необходимой частотой, определяемой

генератором 1 и счетчиком 2, заполняют сумматор 4 до тех пор, пока не закроется клапан 3 в момент первой смены кода преобразователя 10, когда по сигналу схемы «ИЛИ 14 трпггер 13 возвращается в исходное положеппе. При этом с некоторой задержкой, определяемой схемой 15, открывается клапан 16 на время, достаточное для параллельного ввода в сумматор 4 эталонного кода из схемы 18. Эталонный код соответствует в выбранном масштабе расчетному времени схемы кода преобразователя и постоянно хранится в схеме 18.

В сумматоре 4 формируется результирующий код, показывающий величину ощибки в первой измеряемой точке схемы кода преобразователя 10. По окончании переходных процессов в сумматоре 4 сигналом со схемы 14 с фиксированной задержкой открывается клапан 5, и код сумматора 4 вводится в cxewv памяти 6. Далее код ощибки посредством дошифратора 7 выводится ла схему индикации 8.

При срабатывании схемы задержки 17 г некоторой задержкой, определяемой схемой 19, триггер 13 изменяет свое состояние и вновь открывает клапан 3. С этого момента начинается измерение ощибки воспроизведения преобразователем следующего угла квантования. Аналогично производятся измерения во всех точках смены кода преобразователя..

Сумматор 4 работает таким образом, что в нем в течение всех периодов измерений постоянно хранится суммарная ошибка воспроизведения углов квантования для всех предыдущих точек измерения. Кроме того, для учета знака измеряемой ошибки в начале измерений в сумматор 4 вводится код, соответствующий максимально возможной углово ошибке, который является постоянной составляющей в коде сумматора. Код ощибки в каждой измеряемой точке смены кода преобразсвателя либо меньше, либо больше этого кода в зависимости от знака ошибки.

Эталонный код, который постоянно хранится в схеме 18 и периодически вводится в сумматор 4, выбирается с недостатком, соответствующим суммарному времени задержек, обеспечиваемых схемами 15 и 17.

Предмет изобретения

Устройство для автоматического определения ощибки преобразователя угол - код, содержащее последовательно соединенные генератор стабильной частоты, счетчик импульсов, первый клапан, сумматор, второй клапан, схему памяти ошибки, первый дешифратор, схему индикации и последовательно соединенные привод постоянной скорости, преобразователь,

схему преобразования кода в двоичный код, второй дешифратор, триггер, выход которого соединен со вторым входом первого клапана, отличающееся тем. что с целью, расширепия пределов определения ошибки преобразователя, в нем установлены схема «ИЛИ, первач схема задержки, третий клапан, вторая схема задержки, схема памяти эталонного кода, тре тья схема, задержки, причем вход схемы «ИЛИ подключен к выходу смехы преобразования кода в двоичный код, а выход соединен со вторым входом триггера, со входами первой и второй схем задержки, выход первой схемы задержки соединен с первым входом третьего клапана, второй вход которого подключей к выходу схемы памяти эталонного кода, а выход соединен со вторым входом сумматора, первый выход второй схемы задержки подключен ко второму входу второго клапана, а второй вход соединен со входом

третьей схемы задержки, выход которой подключен к первому входу триггера.

Даты

1972-01-01—Публикация