элемента ИЛИ, первые входы всех регистров объединены и подключены к первому входу блока оперативной памяти, вторые входы попарно объединенных регистров подключены к соответствующим первым управляющим входам блока оперативной памяти, третьи входы регистров подключены к соответствующим вторым управляющим входам блока оперативной памяти, выход первого элемента ИЛИ, выход второго элемента ИЛИ и вторые выходы первого и последнего регистра, третьи выходы осталь- , ных регистров подключены соответствен но к первому, второму и третьим выхо-, дам блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1984 |

|

SU1231529A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

| Калибратор периодических сигналов | 1989 |

|

SU1709262A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

1. УСТРОЙСТВО ДЛЯ ПЕРЕДАШ ТЕЛЕМЕТРИЧЕСКОП ИНФОРМАЦИИ, содержащее коммутатор, первые входы которого подключены к информационным входам устройства, выход коммутатора через преобразователь аналог-код подключен к первому входу регистра, синхронизатор, выход которого подключен через элемент задержки к входу, первого счетчика, второму входу коммутатора и второму входу регистра, первый выход первого счетчика подключен через второй счетчик к первому выходу устройства, отличающееся тем, что, с целью повьшения точности передачи информации, в него введены блок постоянной памяти, блок оперативной памяти,.вычитатели, делитель, умножитель, сумматор, дешифраторы, выход регистра подключен к объединенным первым входам первого дешифратора, блока оперативной памяти первого вычитателя, выход первого дешифратора через второй дешифратор подключен к первым управляющим входам блока оперативной памяти и блока постоянной памяти, первый и второй выходы блока оперативной памяти подключены соответственно к первому входу второго вычитателя и объединенным вторым входам второго и первого вычитателя, третьи выходы блока оперативной памяти подключены к соответствующим вторым входам первого дешифратора, выход второго вычитателя подключен к первому входу делителя, выход которого подключен к первому входу сумматора, выход которого подключен к второму выходу устройства, выход первого вычитателя подключен к пер- , вому входу умножителя, выход которого подключен к второму входу делителя, первый и второй выходы блока -постоян-г ной памяти подключены соответственнр к первому входу третьего вычитателя и объединенным вторым входам второго вычитателя и сумматора, выход третьего вычитателя подключен к второму входу умножителя, третий вход сумматора объединен с первым входом третьего дешифратора и подклюОд чен к выходу синхронизатора, выход первого счетчика подключен к второму входу третьего дешифратора, выходы которого подключены к вторым управляющим входам блока оперативной памяти. 2. Устройство по п. 1, о т л и«чающееся тем, что блок оперативной памяти содержит регистры и элементы ИЛИ, первый выход каждого регистра, кроме последнего, подключен к соответствующему входу первого элемента ИЛИ, второй выход каж;того регистра, кроме первого, подключен к соответствующему входу второго

«

Изобретение относится к технике передачи на расстояние измерительной информации и может быть использовано в устройствах передачи телеметрической информации.

Известен аналого-цифровой преобразователь с автоматической коррекцией, содержащий блок аналог-код, блок код-аналог, счетчик, коммутатор вычислительный блок 1 3Устрой ство повьшает точность преобразования путем коррекции, однако его недостатком является большое время коррекции, в три раза превьппающее время одного преобразования, из-за чего устройство не позволяет проводить коррекцию в реальном масштабе времени.

Кроме того, точность коррекции определяется точностью блока коданалог и Точностью выбора образцовых сигналов, которые выбираются по значениям разрядов преобразованного сигнала, считая, что передаточная характеристика блока код-аналог идеальная, однако она отлична от идеальной. Тем caffi iM берется не ближайшее значение образцового сигнала, что уменьшает точность коррекции.

Наиболее близким по технической сущности к изобретению является устройство для передачи телеметрической информации, содержащее коммутатор, п входов которого - входы эталонных сигналов, выходы коммутатора подключены к входам устройства, блок тактовой синхронизации, элемент задержки, счетчик слов, счетчик кадров, блок аналог-код, выходной регистр, причем выход блока тактовой синхронизации подключен к входу элемента задержки, выход которого подключен

к входу счетчика слов, к управляющему входу коммутатора и управляющему вхо-ду выходного регистра, выход коммутатора подключен к входу блока аналогкод, выход которого соединен с информационным входом выходного регистра, выход счетчика слов подключен к входу счетчика кадров, выход которого подключен к управляющему выходу устройства, к информационному выходу устройства подключен выход выходного регистра 2.

Сущность изобретения заключается в передаче в каждом кадре телеметрической информации, кроме измерительной информации, передача также измеренных значений п образцовых сигналов, которые в приемном устройстве используются для коррекции погрешностей аналого-цифрового преобразователя.

При передаче сигналов на приемную станцию возникает погрешность передачи (ее несколько уменьшают помехоустойчивым кодированием), которая накладывается как на измеренные значения сигналов датчиков, так и на измеренные значения образцовых сигналов , используемые для коррекции систематической погрешности измерений. т.е. в результате коррекции получением значения, погрешность которых равна ожидаемой погрешности плюс двойная погрешность передачи.

При коррекции измеренных значений на борту летательного аппарата в приемном устройстве получаем значения, у которых погрешность равна ожидаемой погрешности плюс одинарная

погрешность передачи.

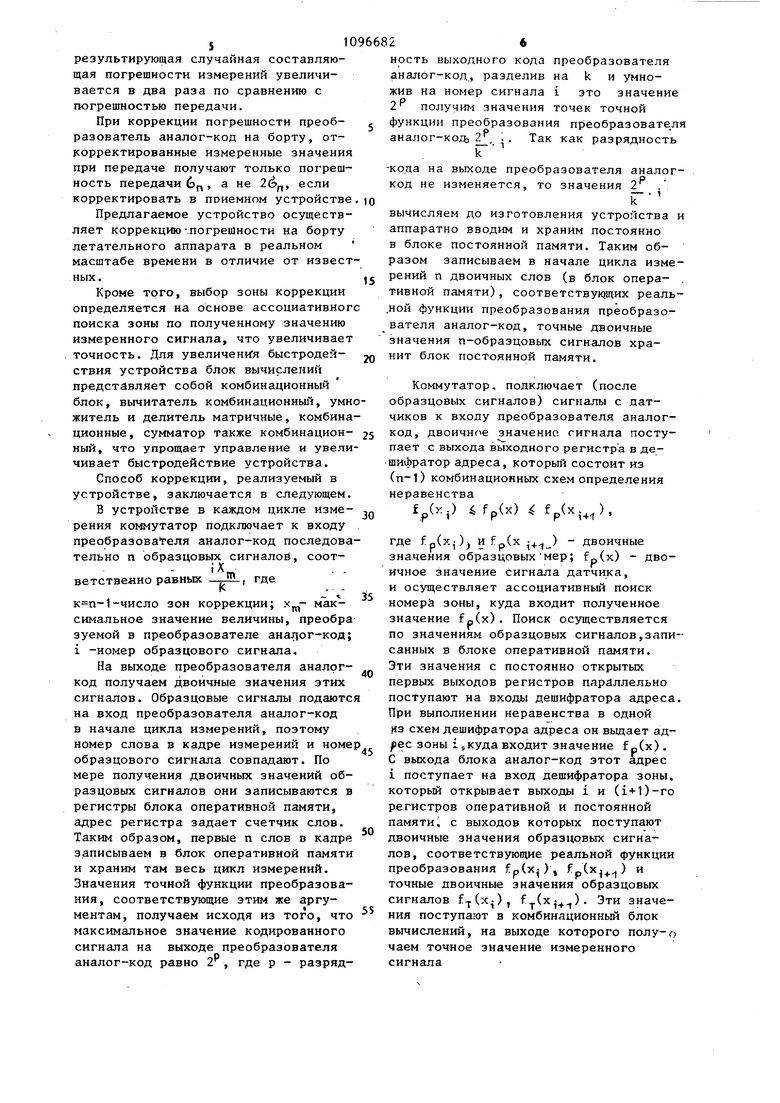

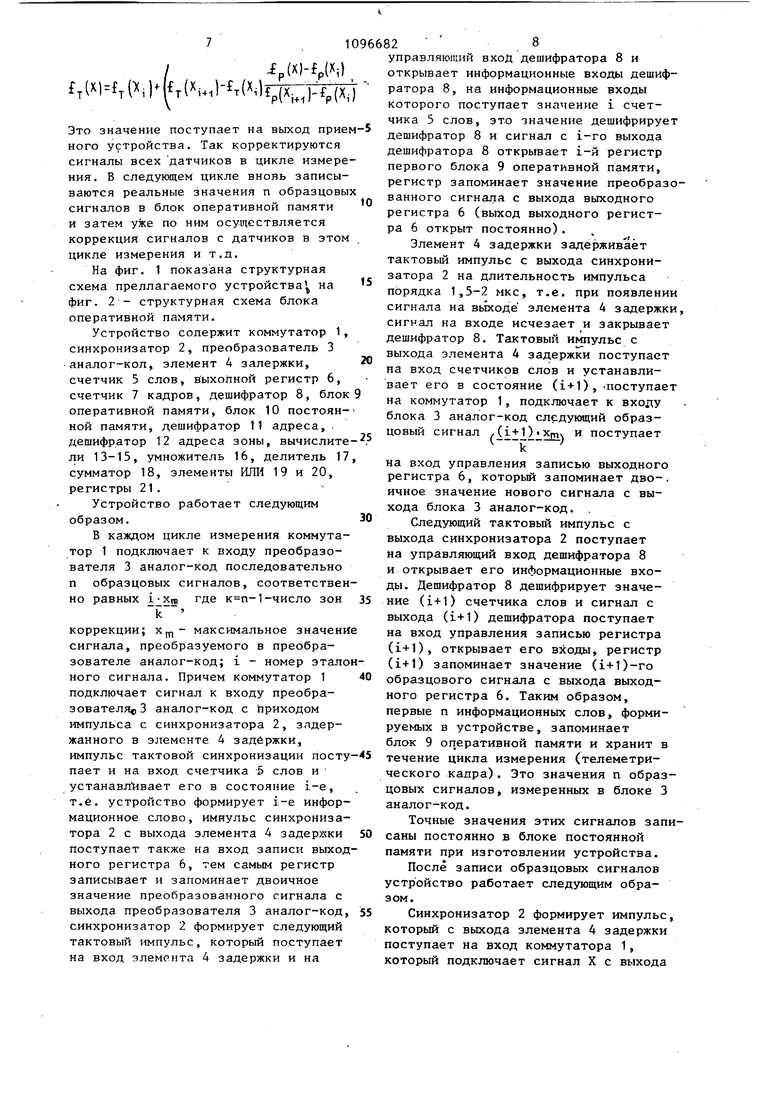

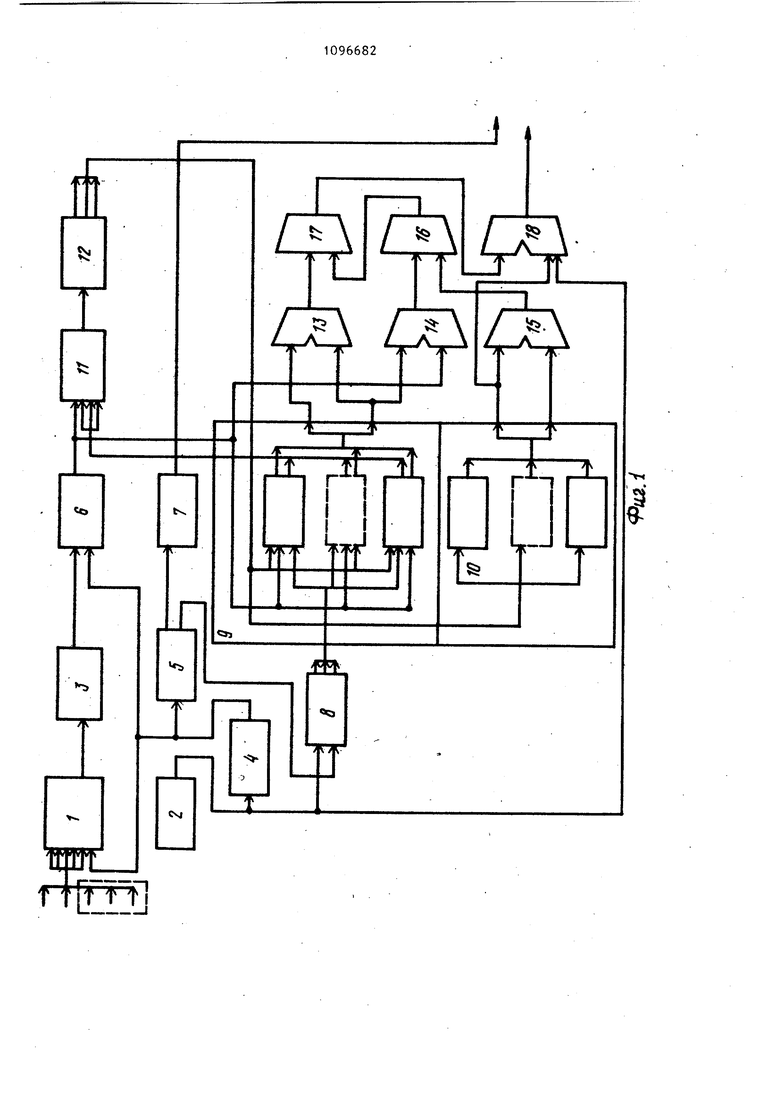

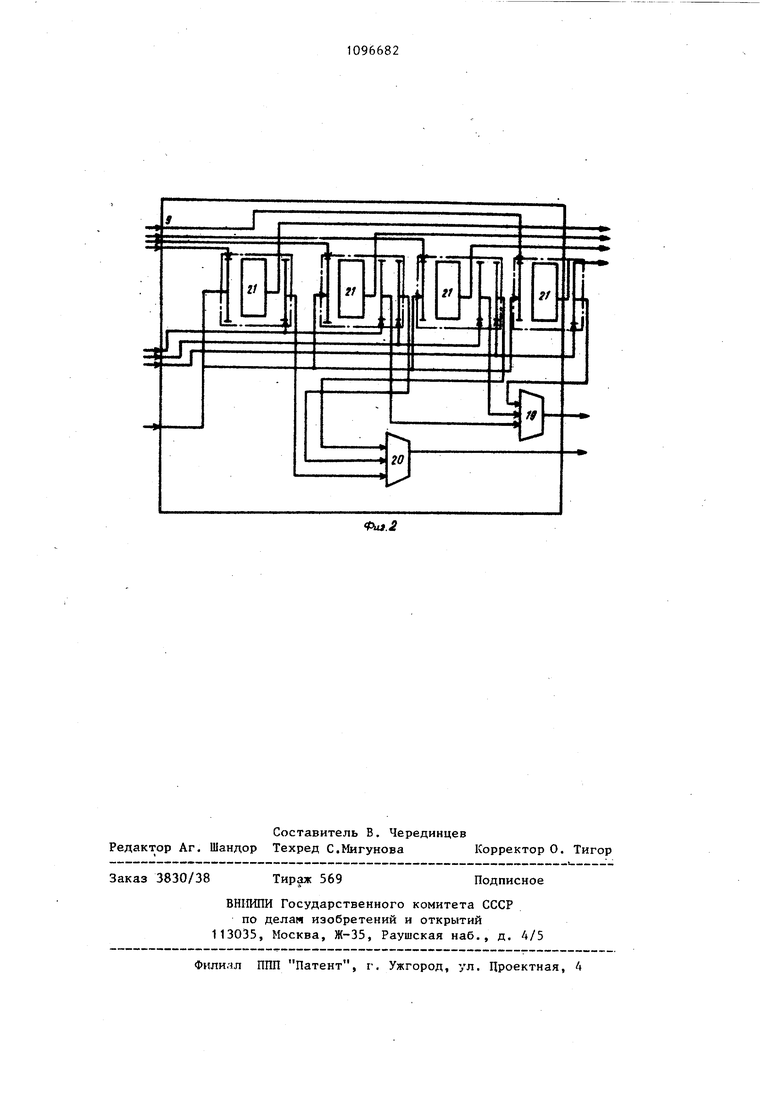

Целью изобретения является повы- Q шение точности передачи измерительной информации. Поставленная цель достигается тем, что в устройство для передачи телеметрической информации, содержащее коммутатор, первые входы которог подключены к информационным входам устройства, выход коммутатора через преобразователь аналог-код подключен к первому входу регистра, синхронизатор, выход которого подключен чере элемент задержки к входу первого счетчика, второму входу коммутатора и второму входу регистра, первый выход первого счетчика подключен через второй счетчик к первому выходу устройства, введены блок постоянной памяти, блок оперативной памяти, вычитатели, делитель, умножитель, сумматор, дешифраторы, выход регистра подключен к объединенным первым входам первого дешифратора, блоки опера тивной памяти и.первого вычитателя, выход первого дешифратора через второй дешифратор подключен к первым управляющим входам блока оперативной памяти и блока постоянной памяти, первый и второй выходы блока операти ной памяти подключены соответственно к первому входу второго вычитателя и объединенным вторым входам второго и первого вычитателя, третьи вьосоды блока оперативной памяти подключены соответствующим вторым входам первог .дешифратора, выход второго вычитател подкдвочен к первому входу делителя, выход которого подключен к первому входу сумматора, выход которого подключен к второму выходу устройства, выход первого вычитателя подключен к первому входу умножителя, выход которого подключен к второму входу делителя, первьй и второй выходы бло ка постоянной памяти подключены соот ветствен«о к первому входу третьего вычитателя и объединенным вторым входам второго вычитателя и сумматора,, выход третьего вычитателя. подклю чей к второму входу умножителя, третий вход сумматора объединен с первым входом третьего дешифратора и подключен к выходу синхронизатора, выход первого счетчика подключен к второму входу третьего дешифратора, выход которого подключен к вторым управляющим входам блока оперативной памяти. Кроме того, блок оперативной памяти содержит регистры и элементы ИЛИ, первый выход каждого регистра, кроме последнего, подключен к соответствующему вхЪду первого элемента ИЛИ, второй выход каждого регистра, кроме первого, подключен к соответствующему входу второго элемента 1ШИ, первые входы всех регистров объединены и подключены к первому Bxojgy блока оперативной памяти, вторые входы попарно объединенных регистров подключены к соответствующим первым управ- ляющим входам блока оперативной памяти, третьи входы регистров подключены к соответствующ}м вторым управляющим входам блока оперативной памяти, выход первого элемента ИЛИ, выход второго элемента ИЛИ и вторые выходы первого и последнего регистра, третьи выходы остальных регистров подключены соответственно к первому, второму и третьим выходам блока оперативной памяти. Устройство передачи осуществляет коррекцгао систематической погрешности преобразователя аналог-код на борту летательного аппарата, а уже откорректированные значения передает ил приемную станцию, которая принимает значения измерения в два раза меньшей случайной составляющей погрешности канала передачи. Необходимость коррекции погр шности преобразователя аналог-код на борту связана с тем, что при передаче значений измерений в них канал передачи вносит погрешность, которая сравнима с систематической составляющей погрешности преобразователя аналог-код. Эту погрешность получают как измеренные значения, так и значения, используемые при коррекции погрешности, а так как в формулу коррекции погрешности (,,-M )-«(о где f(lU. « ( измеренные значения датчика и двух образцовых мер, и выполняемую вычислительным блоком случайная погрешность передачи входит четыре раза, то результирующая случайная погрешность будет определяться учетверенной дисперсией где - результирующая случайная погрешность, 6п - погрешность передачи, т.е. п результирующая случайная составляющая погрешности измерений увеличивается в два раза по сравнению с погрешностью передачи. При коррекции погрешности преобразователь аналог-код на борту, откорректированные измеренные значения при передаче получают только погрешность передачи 6 а ,, если корректировать в поиемном устройстве Предлагаемое устройство осуществляет коррекцию-.погрешности на борту летательного аппарата в реальном масштабе времени в отличие от извест ных . Кроме того, выбор зоны коррекции определяется на основе ассоциативног поиска зоны по полученному значению измеренного сигнала, что увеличивает точность. Для увеличения быстродействия устройства блок вычислени представляет собой комбинационный блок, вычитатель комбинационньй, умн житель и делитель матричные, комбина ционные, сумматор также комбинационHbrii, что упрощает управление и увели чивает быстродействие устройства. Способ коррекции, реализуемый в устройстве, заключается в следующем. В устройстве в каждом цикле измерения коммутатор подключает к входу преобразовагеля аналог-код последова тельно п образцовьрс сигналов, соотI л. . ветственно равных -j-Si-, где к п-1-число зон коррекции; максимальное значение величины, преобра зуемой в преобразователе анал ог-код; i -номер образцового сигнала. На выходе преобразователя аналогкод получаем двоичные значения этих сигналов. Образцовые сигналы подаютс на вход преобразователя аналог-код в начале цикла измерений, поэтому номер слова в кадре измерений и номе образцового сигнала совпадают. По мере получения двоичных значений образцовых сигналов они записываются в регистры блока оперативной памяти, адрес регистра задает счетчик слов. Таким образом, первые п слов в кадре записываем в блок оперативной памяти и храним там весь цикл измерений. Значения точной функции преобразования, соответствующие этим же аргументам, получаем исходя из того, что максимальное значение кодированного сигнала на выходе преобразователя аналог-код равно 2 , где р - разряднрсть выходного кода преобразователя аналог-код, разделив на k и умножив на номер сигнала i это значение 2 получим значения точек точной функции преобразования преобразовате,ля аналог-код, 2, i . Так как разрядность -кода на выходе преобразователя аналогкод не изменяется, то значения 2 . вычисляем до изготовления устройства и аппаратно вводим и храним постоянно в блоке постоянной памяти. Таким образом записываем в начале цикла измерений п двоичных слов (в блок оперативной памяти), соответствующих реальной функции преобразования прёобразователя аналог-код, точные двоичные значения п-образцовых сигналов хранит блок постоянной памяти. Коммутатор, подключает (после образцовых сигналов) сигналы с датчиков к входу преобразователя аналогкод, двоичное значение гигнала поступает с выхода выходного регистра в дешифратор адреса, который состоит из (п-1) комбинационных схем определения неравенства fp.-,. fpCx.) fp(x) где fp(xj) и f р(х i-(--)) двоичные значения образцовыхмер; fp(x) - двоичное значение сигнала датчика, и осуществляет ассоциативньп поиск номера зоны, куда входит полученное значение f„(х). Поиск осуществляется по значениям образцовых сигналов,записанных в блоке оперативной памяти. Эти значения с постоянно открытых первых выходов регистров параллельно поступают на входы дешифратора адреса. При выполнении неравенства в одной КЗ схем дешифратора адреса он вьщает адipec зоны i 8 куда входит значение f р(х) . С выхода блока аналог-код этот адрес i поступает на вход дешифратора зоны, который открывает выходы i и (i+1)-ro регистров оперативной и постоянной памятиi с выходов которых поступают двоичные значения образцовых сигналов, соответствующие реальной функции преобразования fр{х|), fр(х) и точные двоичные значения образцовых сигналов f(x.), ..,). Эти значения поступают в комбинационный блок вычислений, на выходе которого полу-о чаем точное значение измеренного сигнала / -fp(x)-M) ,(Х1,(.).|,(Х,,Л(Х,) Это значение поступает на выход прие ного устройства. Так корректируются сигналы всех датчиков в цикле измере ния . В следующем цикле вновь записываются реальные значения п образцовы сигналов в блок оперативной памяти и затем уже по ним осуществляется коррекция сигналов с датчиков в этом цикле измерения и т.д. На фиг. 1 показана структурная схема предлагаемого устройства на фиг. 2 - структурная схема блока оперативной памяти. Устройство содержит коммутатор 1, синхронизатор 2, преобразователь 3 аналог-кол, элемент 4 задержки, счетчик 5 слов, выходной регистр 6, счетчик 7 кадров, дешифратор 8, блок оперативной памяти, блок 10 постоявной памяти, дешифратор 11 адреса, дешифратор 12 адреса зоны, вычислите ли 13-15, умножитель 16, делитель 17 сумматор 18, элементы ИЛИ 19 и 20, регистры 21. Устройство работает следующим образом. В каждом цикле измерения коммутатор 1 подключает к входу преобразователя 3 аналог-код последовательно п образцовых сигналов, соответствен но равных iX™ где к п-1-число зон коррекции; х,- максимальное значени сигнала, преобразуемого в преобразователе аналог-код; i - номер этало ного сигнала. Причем коммутатор 1 подключает сигнал к входу преобразователяв 3 аналог-код с приходом импульса с синхронизатора 2, задержанного в элементе 4 задержки, импульс тактовой синхронизации посту пает и на вход счетчика -5 слов и устанавливает его в состояние i-e, т.е. устройство формирует i-e информационное слово, имнульс синхронизатора 2 с выхода элемента 4 задержки поступает также на вход записи выход ного регистра 6, тем самьм регистр записывает и запоминает двоичное значение преобразованного сигнала с выхода преобразователя 3 аналог-код синхронизатор 2 формирует следующий тактовый импульс, который поступает на вход элемента 4 задержки и на управляющий вход дешифратора В и открывает информационные входы дешифратора 8, на информационные входы которого поступает значение i счетчика 5 слов, это значение дешифрирует дешифратор 8 и сигнал с i-ro выхода дешифратора 8 открьгаает i-й регистр первого блока 9 оперативной памяти, регистр запоминает значение преобразованного сигнала с выхода выходного регистра 6 (выход выходного регистра 6 открыт постоянно). Элемент 4 задержки задерживает тактовый импульс с выхода синхронизатора 2 на длительность импульса порядка 1,5-2 мкс, т.е. при появлении сигнала на вьЬсоде элемента 4 задержки, сигнал на входе исчезает и закрывает дешифратор 8. Тактовый импульс с выхода элемента 4 задержки поступает па вход счетчиков слов и устанавливает его в состояние (i+1), Поступает на коммутатор 1, подключает к входу блока 3 анало -код следующий образцовый сигнал ,(i+1)«x. и поступает ( ) на вход управления записью выходного регистра 6, который запоминает дво-, ичное значение нового сигнала с выхода блока 3 аналог-код. Следующий тактовый импульс с выхода синхронизатора 2 поступает на управляющий вход дешифратора 8 и открывает его информационные входы. Дешифратор 8 дешифрирует значение (i+1) счетчика слов и сигнал с выхода (i+1) дешифратора поступает на вход управления записью регистра (i+1), открывает его входы, регистр (i+1) запоминает значение (i+1)-ro образцового сигнала с выхода выходного регистра 6. Таким образом, первые п информационньпс слов, формируемых в устройстве, запоминает блок 9 оперативной памяти и хранит в течение цикла измерения (телеметрического кадра). Это значения п образцовых сигналов, измеренных в блоке 3 аналог-код. Точные значения этих сигналов записаны постоянно в блоке постоянной памяти при изготовлении устройства. После записи образцовых сигналов устройство работает следующим образом. Синхронизатор 2 формирует импульс, который с выхода элемента 4 задержки поступает на вход коммутатора 1, который подключает сигнал X с выхода 1 датчика на вход блока 3 аналог-код, импульс с выхода элемента 4 задержки также поступает на на управляющий вход выходного регистра 6 и открывае его информационные входы, регистр 6 запоминает значение f(х) с выхода блока 3 аналог-код. Это значение fp(x) с постоянно открытых выходов выходного регистра 6 поступает на вход дешифратора 11 адреса, на п остальных входов которого поступают измеренные значения п образцовых сигналов с постоянно открытых первых выходов п регистров блока 9 памяти. Дешифратор адреса по значению преобразованного сигнала определяет зону коррекции по признаку fp(x/) fp(x) : fp(x.). Значение зоны i поступает на вход дешифратора 12 адреса зоны, сигнал с i-ro выхода которого открывает выходы регистров (i) и (i+1) первого 9 и второго 10 блоков памяти. Значени fp(x) и fp(x ) с вторых выходов регистров 21 блока 9 оперативной памяти поступают через схемы 19 и 20 сборки (элементы ИЛИ) на два выхода блока 9 оперативной памяти. Значения fp(x,-) и fp(x) с выходов регистров блока 10 постоянной памяти также поступают на первый и второй выхода блока 10 постоянной памяти. Значения с выходов блоков 9 и 10 памяти и с выхода выходного регистра 6 поступают параллельно на входы вычитателей. Значение fp(x ) с первого выхода блока 9 памяти поступает на Первый вход вычитателя 13, на-второй вход которого поступает значение fp(x) с второго выхода блока 9 памяти. Это значение поступает также на вход вычитателя 14, на второй вход которого поступает значение fp(x) с выхода выходного регистра 6. На входы третьего вычитателя 15 поступают значения с выходов второго блока памяти f(xj-4.i) и f(x), причем значение f(xj) с второго выхода блока 10 памяти поступает также на вход сумматора 18. Первый вычитатель 13 выдает сигнал, равный (fp(x.,)-fp(xj) , второй вычитатель 14 выдает сигнал (f (x)-fp(xp, третий вычитатель 15 вьщает сигнал, равный (f( )-f(x|) ). Значения с выходов вычитателей 14 и 15 поступают в матричный комбинационный умножитель 16, который умножает сигналы с выходо 210, вычитателей. Произведение с выхода умножителя 16 поступает на вход делимого матричного, комбинационного делителя 17, на вход делителя которого поступает значение с выхода первого вычитатоля 13, результат деления с выхода делителя 17 поступает на второй вход сумматора 18, который суммирует зто частное с точным значением i-ro образцового сигнала f(Xj). На выходе сумматор 18 формирует точное значение преобразованного сигнала с выхода датчика: MKH;w.(f,(x,.,M,(x,,jg. сдедующий сигнал с выхода синхронизатора 2 поступает на управляющий вход суютатора 18 и открывает его информационный выход, точное значение поступает на выход устройства, С момента появления сигн.ала на выходе выходного регистра 6 до момента появления результирующего сигнала ца выходе сумматора 18 проходит время, меньшее времени задержки в элементе 4 задержки. Преимуществом предлагаемого устройства является повышение точности передачи в 2 раза по сравнению с известным, имеющим результирукицую погрешность, равную погрешности коррекции, плюс погрешность передачи, которая равна 0.1%. В предлагаемом устройстве результирующая погрешность равна погрешности коррекции плюс погрешность передачи (0,05%). Предлагаемое устройство уменьшает погрешность, обусловленную погрешностью передачи в 2 раза. Кроме того, преимуществом предлагаемого устройства является простота управления и большое быстродействие. При реализации устройства на элементах серии ЭСЛ500 время коррекции составляет Т 500 н с. Самый быстродействуклций аналогоцифровой преобразователь АЦП (/ 1/4.имеет время преобразования, равное , Т 2500 н с., т.е. , тем самым устройство осуществляет коррекцию погрешности в реальном масштабе времени, что является необходимым условием фop mpoвaния телеметрического кадра.

(

г/

LL

t « fV

iMT

//

.J

10 Y

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алиев Т.Н., Сейдель Л.Р | |||

| Автоматическая коррекция погрешностей и цифровых измерительных приборов | |||

| М., Энергия, 1975, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Основы радиотелеметрии | |||

| М., Воениздат, 1971, с | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1984-06-07—Публикация

1983-03-21—Подача