1

Предложенное устройство относится к области автоматики и вычислительной техники и предназначено для определения закона распределения ошибок ;преобразователей уголкод.

Известно устройство, позволяющее автоматически определить распределение ошибок преобразователей угла в код. Его недостаток весьма сложная функциональная схема, содержащая кроме узлов, применяемых при автоматическом определении ошибок преобразователей, сумматор, несколько двоичных счетчиков, регистр и т. д.

Целью изобретения является повышение надежности работы устройства.

Предложенное устройство отличается от известного существенно более простой логической схемой, а, следовательно, более надежно.

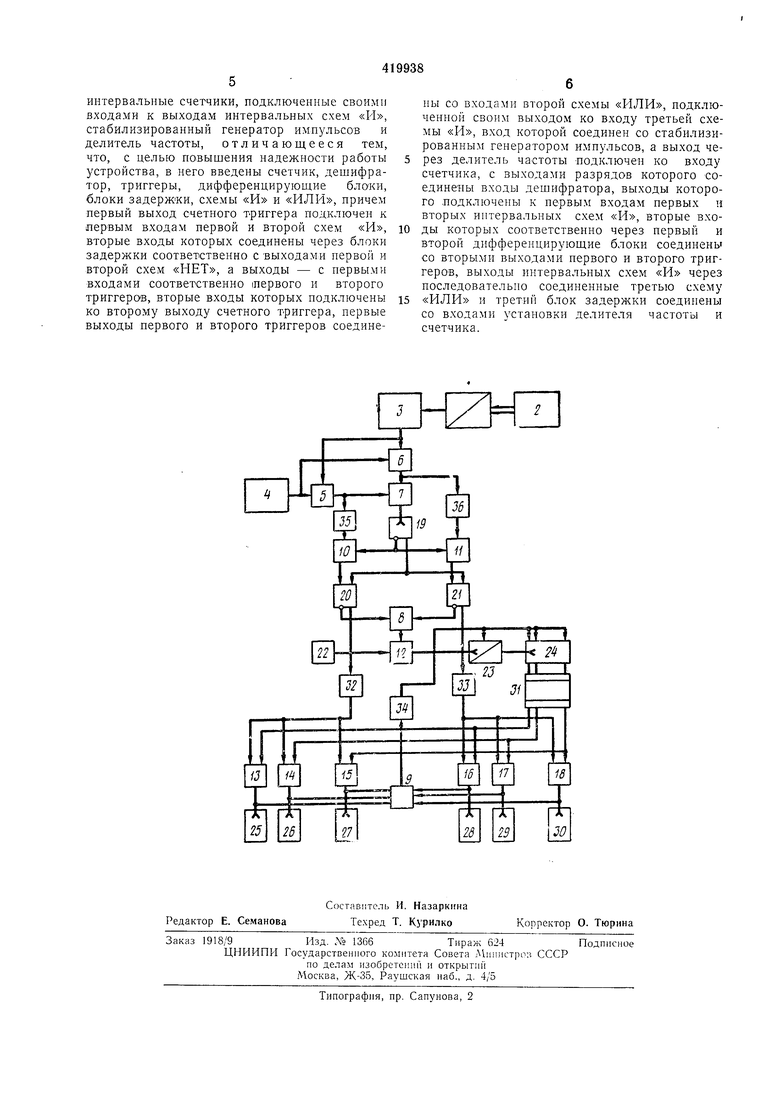

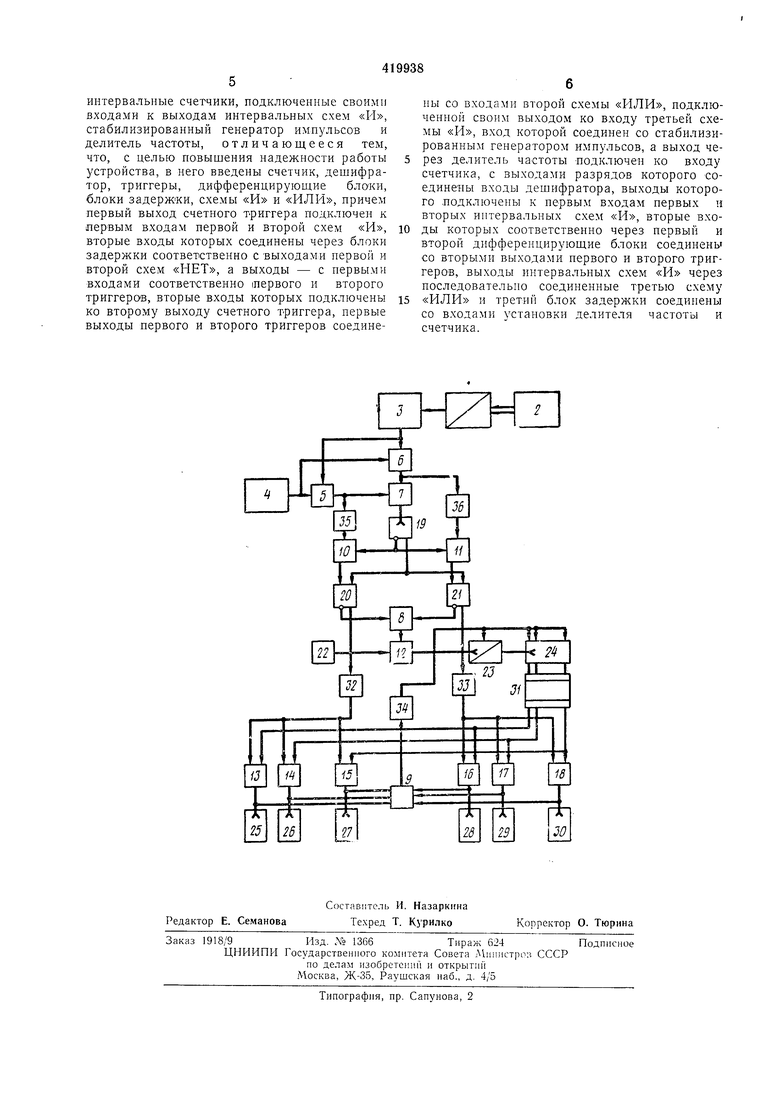

На чертеже нриведена функциональная схема предложенного устройства.

Она содержит испытуемый преобразователь 1 угол-код, привод 2 равномерной скорости, блок 3 реальных сигналов, блок 4 эталонных сигналов, схемы «НЕТ 5 и 6, схемы «ИЛИ 7-9, схемы «И 10-12, интервальные схемы «И 13-18, счетный триггер 19, триггеры 20 и 21, стабилизированный генератор импульсов 22, делитель частоты 23, счетчик 24, интервальные счетчики 25-30, дешифратор 31, дифференцирующие блоки 32 и 33 и блоки задержки 34-36.

Испытуемый преобразователь 1 жестко связан с приводом 2 равномерной скорости. С выходами преобразователя 1 соединен блок 3 реальных сигналов, назначение которого вырабатывать импульс в момент смены кода в преобразователе 1. Задачи блока 4 эталонных сигналов - формировать импульсы в расчетные моменты смены кода преобразователя. Выходы блоков 3 и 4 через схемы «НЕТ 5 и 6 подключены ко входам схемы «ИЛИ 7, выход которой соединен со счетным входо.м триггера 19. Первый вы.ход триггера 19 подключей ко входам схем «И 10 и 11, вторые входы которых соединены через блоки задержки 35 и 36 с выходами схем «НЕТ 5 и 6, соответственно. Выходы схем «Н 10 и 11 соединены с нервыми входами триггеров 20 н 21, вторые

входы которых подключены ко второму выходу триггера 19.

Первые выходы триггеров 20 и 21 соединены со входами схемы «ИЛИ 8, выход которой подключен ко входу схемы «И 12, соединенной вторым входом со стабилизированным генератором имп льсов 22, а выходы - через делитель частоты 23 со счетным входом счетчика 24. Выходы разрядов счетчика 24 соединены со входамн дешифратора 31, выходы

которого пронорционально весу числа соединеиы с первыми входами интервальных схем «И 13-15 и , соогветственно. Вторые входы схем «И 13-15 подключеиы через диффере1шируюш,ий блок 32 ко второму выходу триггера 20. Аналогично вторые входы схем «И 16-18 через дифференцирующий блок 33 соединены со вторым выходом триггера 21.

Выходы схем «Pi 13-18 -подключены каждый к соответствующему интервальному счетчику 25-30, а также все вместе - ко входа.м схемы «ИЛИ 9, выход которой через блок задержки 34 подключен ко входам установки делителя частоты 23 и счетчика 24.

Устройство работает следующим Образом.

Испытуемьи преобразователь 1 приводится с помощью привода 2 в равномерное вращение. При этом на выходе блока 3 реальных слггналов формируются сигналы в моменты чл.сны кода испытуемого преобразователя. Ълок 4 эталонных сигнало1В, сипхронизированпый с блоком 3, формирует импульсы в расчетные моменты смены кода преобразователя. Разница во времени между имлульсами с выходов блоков 3 и 4 характеризует величину и знак ошибки воспроизведения каждого кванта.

Временные интервалы, соответствующие ошибкам разного знака, фиксируются с помощью триггеров 20 и 21. Формирование этих интервалов осуществляется с помощью счетиого триггера 19, восприпил:ающего сигналы с выхода схемы «ИЛИ 7, на входы которой через схемы «НЕТ 5 и 6 подаются импульсы с выходов блоков 3 и 4. Схемы «НЕТ 5 и 6 служат для того, чтобы при совпадении этих и.мпульсов во времени на выходе схемы «ИЛИ 7 не возникало сигнала, так как в противном случае на вход триггера 19 вместо двух поочереди следующих сигналов будет поступать лишь один, что парущит правильное функционирование устройства.

Если первым пришел сигнал с блока 4 и триггер 19 изменил свое исходное состояние, то срабатывает схема «И 10, в результате чего переключается в новое состояние триггер 20. С приходом следующего сигнала с выхода блока 3 триггер 20 возвращается в исходное состояние. Таки.м образом, схема «И 12 оказывается открытой па время, равное отрезку времени между импульсами, поступающими с блоков 3 и 4.

Если первым ирищел сигнал с блока 3, то аналогично описанному работает схема «И 11 и триггер 21, который воздействует на схемы «ИЛИ 8 и «И 12. В предыдущем и в этом случаях время открытого состояния схемы «И 12 определяет величипу ощибки в каждом кванте без учета ее знака. Блоки задержки 35 и 36 необходимы для того, чтобы григгер 19 успел занять новое положение, прежде чем сигнал с выхода схемы «НЕТ 5 или «НЕТ 6 попадет на вход схемы «И 10 или «И 11.

В момент открывания схемы «И 12 импульсы стабилизированного генератора импульсов 22 через делитель частоты 23 начинают подсчитываться в счетчике 24. Время между соседними импульсами на выходе делителя частоты 23 определяет стенень квантования ощибки испытуе.мого нреобразователя в каждой границе смены его кода. Зная величину максимальной ощибки преобразователя и соответствующее ей число в счетчике 24, нетрудно определить в момент закрывания схемы «И 12 (с точностью до погрешности квантования) измеряемую ошибку в каждом кванте преобразователя.

Ра.спределепие измеренных ошибок по образованным, таким образом, интервалам осуществляется с помощью дешифратора 31, выходы которого подключены к двум группа.м интервальных схем «И 13-15 и «И 16-18. Каждая группа соответствует определенному знаку измеряемой ошибки, а каждая схема «И в группе - определепному временному интервалу, с которых сравнивается временной интервал каждой измеряемой ошибки. Так, схема «И 13 (16) соответствует интервалу, условно равному одной единице, схема «И 14 (17)- двум единицам и т. д. Момент определения величины и знака измеряемой ошибки соответствует возвращению триггеров 20 и 21 в исходное положение, что вызывает появление сигналов на выходе дифференцирующих блоков 32 и 33. В зависимости от возникшего сочетания сра батывает одна из схем «И 13-18, что определяет прохождепие :: соответствующий интервальный счетчик 25- 30 сигнала о величине и знаке ошибки воспроизведения данного кванта испытуемого преобразователя.

Таким образом, для каждого кванта преобразователя формируется импульс, подсчитываемый каким-либо из интервальных счетчиков 25-30 в зависимости от припадлежности измеряемой ошибки к одному из интервалов. Число, записанное в счетчиках, соответствует распределению измеряемой ощибки иопытуе.мого преобразователя.

После окончания измерения ошибки очередного кванта преобразователя срабатывает схема «ИЛИ 9, в результате чего сбрасываются в нулевое положение делитель частоты 23 и счетчик 24, подготавливая схему к из.epeнию ошибки следующего кванта. Блок задержки 34 необходим для устойчивой работы устройства.

П р е .п м е т изобретения

Устройство для определения закона распределения ошибок преобразователей уголкод, содержащее привод равиомерной скорости, жестко связанный с валом испытуемого преобразователя, подключенный к преобразователю блок реальных сигналов, выход которого через первую схему «НЕТ соединен с первым входом первой схемы «ИЛИ, блок эталонных сигналов, подключенный через вторую схему «НЕТ ко второму входу первой схемы «ИЛИ, выход которой соединен со входом счетного триггера.

интервальные счетчики, подключенные своими входами к выходам интервальных схем «PI, стабилизированный генератор импульсов и делитель частоты, отличающееся тем, что, с целью новышения надежности работы устройства, в него введены счетчик, дешифратор, триггеры, дифференцирующие блоки, блоки задержки, схемы «И и «ИЛИ, цричем первый выход счетного триггера подключен к первым входам первой и второй схем «И, вторые входы которых соединены через блоки задержки соответственно с выходами первой и второй схем «НЕТ, а выходы - с первыми входами соответственно первого и второго триггеров, вторые входы которых подключены ко второму выходу счетного триггера, первые выходы первого и второго триггеров соединены со входами второй схемы «ИЛИ, подключенной своим выходом ко входу третьей схемы «И, вход которой соединен со стабилизированным генератором импульсов, а выход через делитель частоты подключен ко входу счетчика, с выходами разрядов которого соединены входы дешифратора, выходы которого .подключены к первым входам первых и вторых интервальных схем «И, вторые входы которых соответственно через первый и второй дифференцирующие блоки соединены со вторыми выходами нервого и второго триггеров, выходы интервальных схем «И через последовательно соединенные третью схему «ИЛИ и третий блок задержки соединены со входами установки делителя частоты и счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРЕОБРАЗОВАТЕЛЯ УГОЛ-КОД12 | 1973 |

|

SU432577A1 |

| Устройство для контроля преобразователя угол-код | 1974 |

|

SU477445A1 |

| Устройство для определения ошибок преобразователя угол-код | 1973 |

|

SU440689A1 |

| Устройство для измерения погрешности преобразователя угла поворота вала в код | 1985 |

|

SU1295516A1 |

| Устройство для измерения погрешности преобразователей угол-код | 1978 |

|

SU746679A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОШИБОК ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ-КОД | 1971 |

|

SU427363A1 |

| КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВОВСЕСОЮЗНАЯ^^тт-шштиВИалИОТЕКА | 1972 |

|

SU323670A1 |

| Устройство для определения распределения погрешности преобразователя угол-код | 1974 |

|

SU497622A1 |

| Устройство для стохастических исследований объекта | 1976 |

|

SU670939A1 |

| Устройство для моделирования систем связи | 1989 |

|

SU1665384A1 |

Даты

1974-03-15—Публикация

1972-06-23—Подача