Изобретение относится к цифровой вычислительной технике.

Известен четырехфазный распределитель импульсов в виде двухразрядногО счетчика с дешифратором.

Большое число элементов устройства (два счетных триггера и четыре схемы дешифрации) вызывает значительные трудности при интегральном исследоваиии.

Цель изобретения - создание схемы на МОП-транзисторах со взаимно дополняюшей симметрией, содержашей значительно меньшее число алементов и обеспечиваюший получение четырехфазной серии импульсов без применения схем дешифрации. Это достигается благодаря использованию грех тиновых ячеек и двух дополнительных транзисторов и-типа.

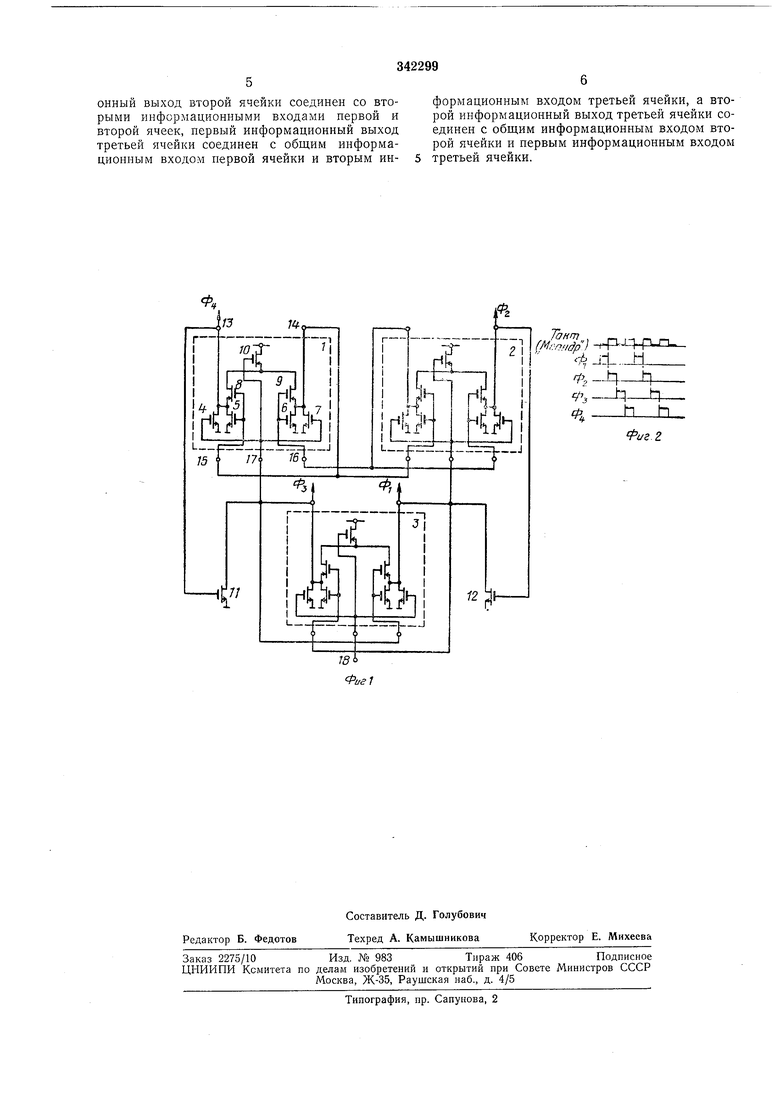

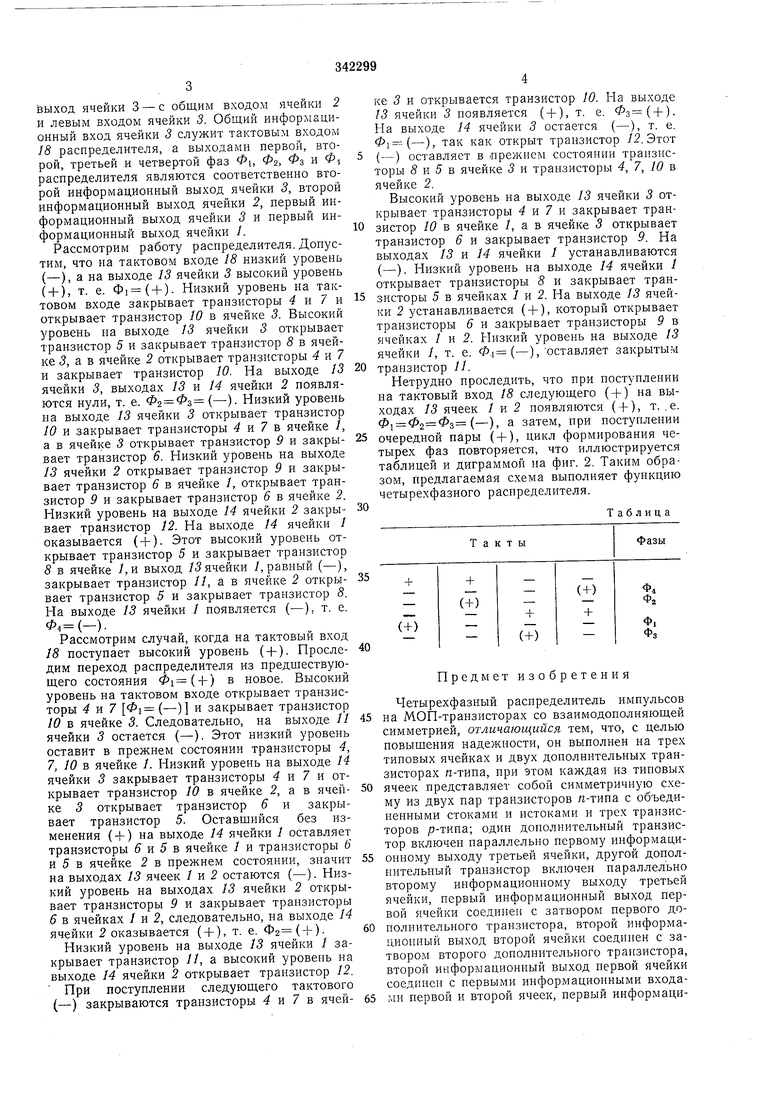

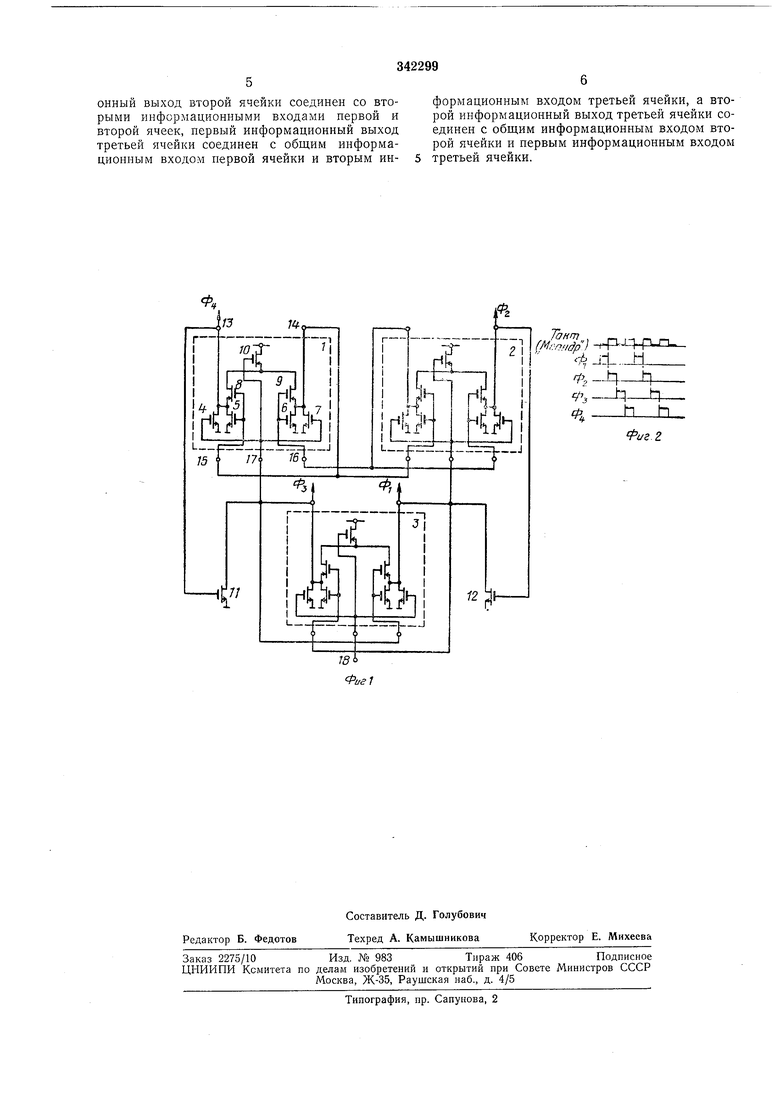

На фиг. 1 показана принциниальпая схема устройства; па фиг. 2-диаграмма, поясняюшая цикл формирования фаз импульсов.

Распределитель содержит типовые ячейки /-3, транзисторы п-типа 4-7, транзисторы р-типа 8-10, дополнительные транзисторы // и 12. Каждая ячейка имеет первый и второй информационные выходы /5 и 14, первый и второй информационные входы 15 и 16, обший информационный вход 17 и 18-тактовый вход распределителя.

симметричную схему из двух пар транзисторов п-типа с объединенными стойками и истоками (4, 5 и 6, 7) и трех транзисторов р-тина, из которых два (5, 9) имеют общий сток, связанный с истоком третьего транзистора 10, сток которого подключен к шине питания. Исток транзистора 8 связан с общим стоком транзисторов 4 и 5, образуя первый информационный выход 13 ячейки, исток транзистора 9 связан с общим стоком транзисторов 6 и 7, образуя второй информационный выход 14 ячейки. Затворы транзисторов 5 и 5 связаны с затворами транзисторов соответственно 5 н 6, образуя первый 15 и второй 16 информационные входы ячейки, а затвор транзистора 10 связан с затворами транзисторов 4 и 7, образуя общий информационный вход 17 ячейки. Дополнительные транзисторы 11 и 12 включены соответственно параллельно выходам 13 и 14 ячейки 3, причем выход 13 первой ячейки соединен с затвором транзистора //, а выход 14 второй ячейки - с затвором транзистора/5. Второй информационный выход ячейки / соединен с нервыми информационными входами своей ячейки и ячейки 2, первый ипфор.мационный выход ячейки 2 соединен со вторыми информационными входами ячеек / и 2. Первый информационный выход ячейки 3 соединен с общим входом ячейки / и вторым входом ячейки 3, а второй информационный Выход ячейки 3 -с общим входом ячейки 2 и левым входом ячейки 5. Общий инфорЛ1ационный вход ячейки 3 служит тактовым входом 18 распределителя, а выходами первой, второй, третьей и четвертой фаз Фь 02, Фз и распределителя являются соответствеиио второй информациоииый выход ячейки 3, второй информационный выход ячейки 2, первый информациопный выход ячейки 3 и первый информациопный выход ячейки /.Ю Рассмотрим работу распределителя. ДопусТИМ, что на тактовом входе 18 низкий уровень (-), а на выходе 13 ячейки 5 высокий уровень ( + ), т. е. Ф1 (-|-). Низкий уровень на тактовом входе закрывает транзисторы 4 и 7 и15 открывает транзистор 10 в ячейке 3. Высокий уровень на выходе 13 ячейки 3 открывает транзистор 5 и закрывает транзистор 8 в ячейке 5, а в ячейке 2 открывает транзисторы 4 и 7 и закрывает транзистор 10. На выходе 1320 ячейки 3, выходах 13 и 14 ячейки 2 появляются нули, т. е. Ф2 ). Низкий уровень на выходе 13 ячейки 3 открывает транзистор 10 и закрывает транзисторы 4 и 7 в ячейке /, а в ячейке 3 открывает транзистор 9 и закры-25 вает транзистор 6. Низкий уровень на выходе 13 ячейки 2 открывает транзистор 9 и закрывает транзистор 6 в ячейке /, открывает транзистор 9 и закрывает транзистор 6 в ячейке 2. Низкий уровень на выходе 14 ячейки 2 закры-30 вает транзистор 12. На выходе 14 ячейки / оказывается { + ) Этот высокий уровень открывает транзистор 5 и закрывает транзистор 8 в ячейке /,и выход /3 ячейки , равный (-), закрывает транзистор //, а в ячейке 2 откры-35 вает транзистор 5 и закрывает транзистор S. На выходе 13 ячейки / появляется {-). т. е. Ф4(-). Рассмотрим случай, когда на тактовый вход 18 поступает высокий уровень ( + ). Просле- 40 ДИМ переход распределителя из предшествующего состояния Ф1(-Ь) в новое. Высокий уровень на тактовом входе открывает транзисторы 4 и 7 Ф1(-) и закрывает транзистор 10 в ячейке 3. Следовательно, на выходе 11 45 ячейки 3 остается (-). Этот низкий уровень оставит в прежнем состоянии транзисторы 4, 7, 10 в ячейке /. Низкий уровень на выходе 14 ячейки 3 закрывает транзисторы - и 7 и открывает транзистор 10 в ячейке 2, а в ячей- 50 ке 3 открывает транзистор 6 и закрывает транзистор 5. Оставшийся без изменения (-Ь) на выходе 14 ячейки 1 оставляет транзисторы 5 и 5 в ячейке 1 и транзисторы 6 и 5 в ячейке 2 в прежнем состоянии, значит 55 на выходах 3 ячеек / и 2 остаются (-).Низкий уровень на выходах 13 ячейки 2 открывает транзисторы 9 и закрывает транзисторы 6 в ячейках / и 2, следовательно, на выходе 14 ячейки 2 оказывается ( + ), т. е. Ф2( + ). Низкий уровень на выходе 13 ячейки / закрывает транзистор 11, SL высокий уровень на выходе 14 ячейки 2 открывает транзистор 12. 60 ке 3 и открывается транзистор 10. На выходе /5 ячейки 3 появляется ( + ), т. е. Фз( + ). На выходе 14 ячейки 3 остается (-), т. е. i(-), так как открыт транзистор /2. Этот {-) оставляет в прежисм состоянии траизисторы 5 и 5 в ячейке 3 и транзисторы 4, 7, 10 в ячейке 2. Высокий уровень па выходе 13 ячейки 5 открывает транзисторы 4 и 7 и закрывает транзистор 10 в ячейке Дав ячейке 3 открывает транзистор 6 и закрывает транзистор 9. На выходах 13 и 14 ячейки / устанавливаются (-). Низкий уровень на выходе 14 ячейки / открывает транзисторы 5 и закрывает транзисторы 5 в ячейках / и 2. На выходе 13 ячейки 2 устанавливается (-f), который открывает транзисторы 6 и закрывает транзисторы 9 в ячейках / и 2. Низкий уровень на выходе /3 ячейки /, т. е. Ф.1 (-), оставляет закрытым транзистор 11. Нетрудно проследить, что при поступлении на тактовый вход 18 следующего ( + ) на выходах 13 ячеек / и 2 появляются ( + ), т. ,е. Ф1 (-), а затем, при поступлении очередной пары ( + ), цикл формирования четырех фаз повторяется, что иллюстрируется таблицей и диграммой на фиг. 2. Таким образом, предлагаемая схема выполняет функцию четырехфазного распределителя. Таблица Нредмет изобретения Четырехфазиый распределитель импульсов на МОП-трапзисторах со взаимодополняющей симметрией, отличающийся тем, что, с целью повышения надежности, он выполнен на трех типовых ячейках и двух дополнительных транзисторах п-типа, при этом каждая из типовых ячеек представляет собой симметричную схему из двух пар транзисторов /г-типа с объединенными стоками и истоками и трех транзисторов р-типа; один дополнительный транзистор включен параллельно первому ииформационному выходу третьей ячейки, другой дополнительный транзистор включен параллельно второму информационному выходу третьей ячейки, первый информационный выход первой ячейки соединен с затвором первого дополнительного транзистора, второй информационный выход второй ячейки соединен с затвором второго дополнительного транзистора, второй информационный выход первой ячейки соединен с первыми информационными входаонный выход второй ячейки соединен со вторыми информационными входами первой и второй ячеек, первый информационный выход третьей ячейки соединен с общим информационным входом первой ячейки и вторым информационным входом третьей ячейки, а второй информационный выход третьей ячейки соединен с общим информационным входом второй ячейки и первым информационным входом третьей ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 1993 |

|

RU2054753C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| Триггер | 1990 |

|

SU1783579A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220123A1 |

,Sj-v

Авторы

Даты

1972-01-01—Публикация