i

Изобретение относится к электронной коммутационной технике и может быть использовано для первичной обработки аналоговых сигналов в мно™ гоканальных системах сбора и распре- деления данных, в частности для управления матричными твердотельными фотоприемниками.

Цель изобретения - расширение функциональных возможностей коммута- тора за счет осуществления опроса заданных каналов с одновременным отключением, а также отключением и шунтированием требуемого количества неопрапшваемых каналов путем введе- ния дополнительного сдвигового регистра и реализации блока выбора каналов в виде устройства, позволяющего осуществлять комбинированное управление ключами каналов коммута- тора.

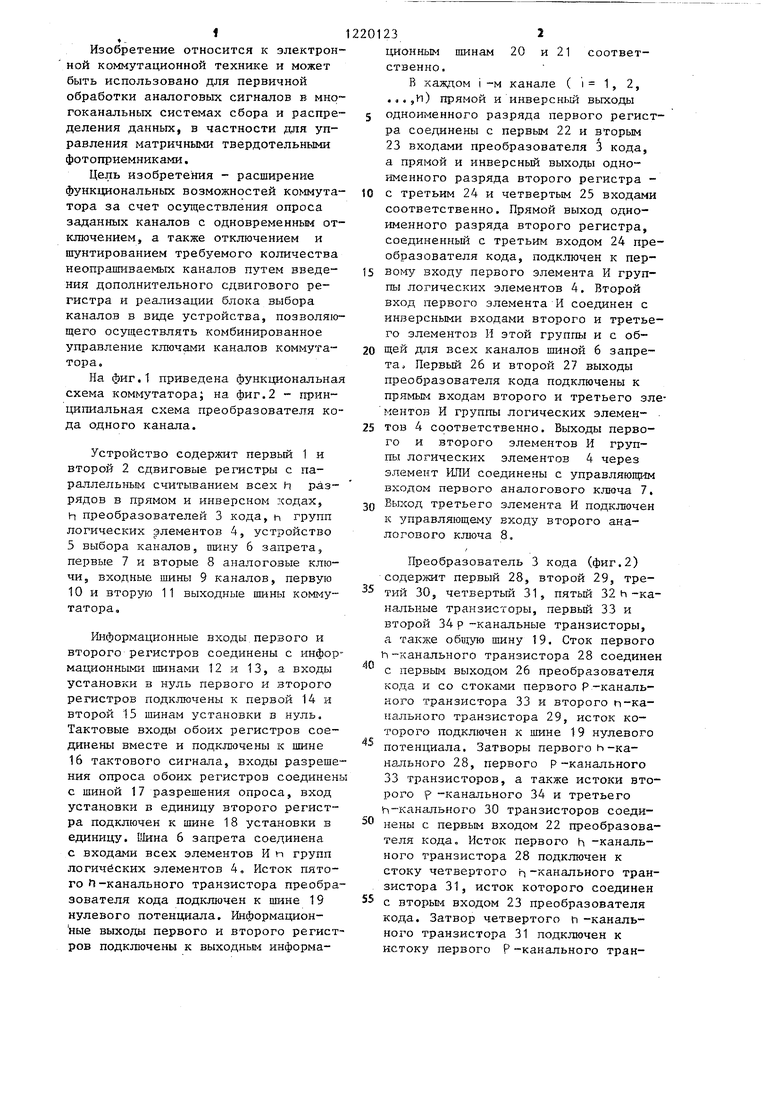

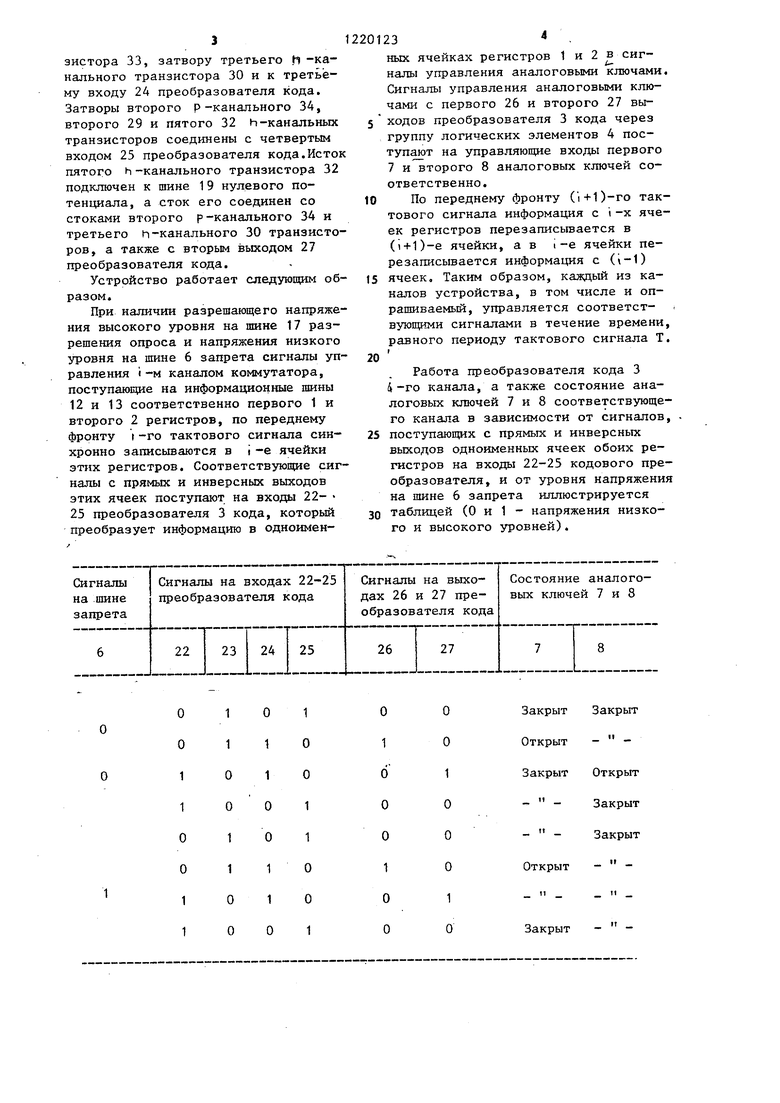

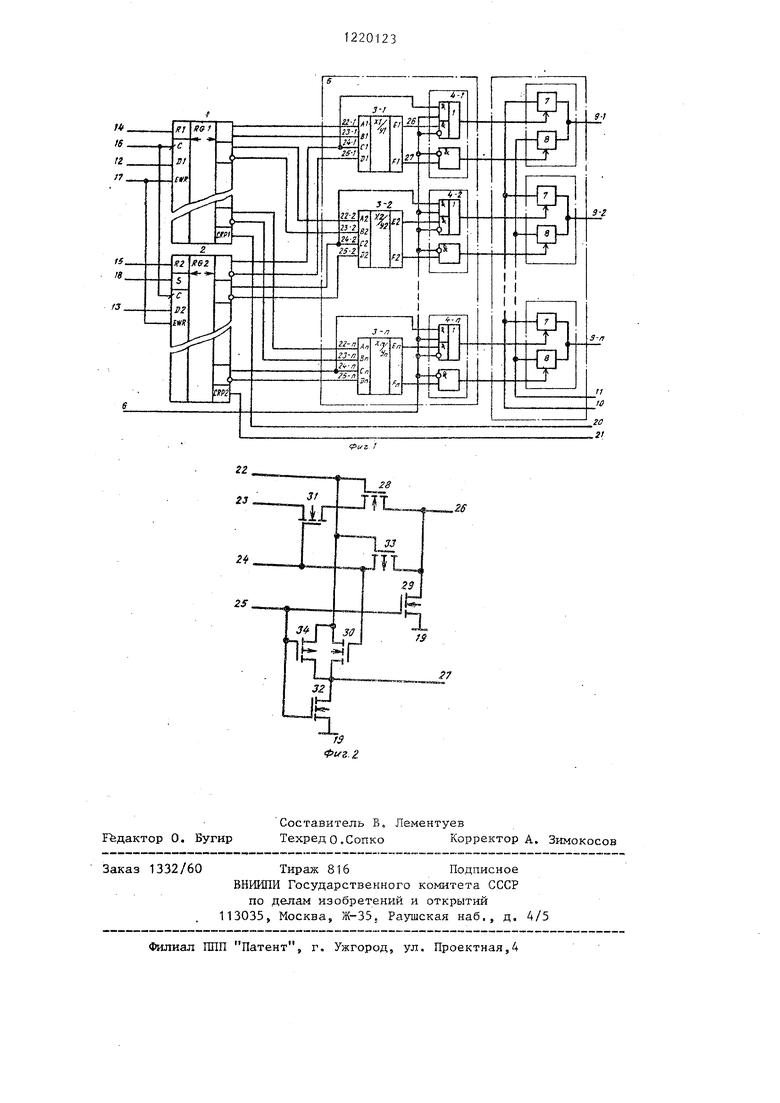

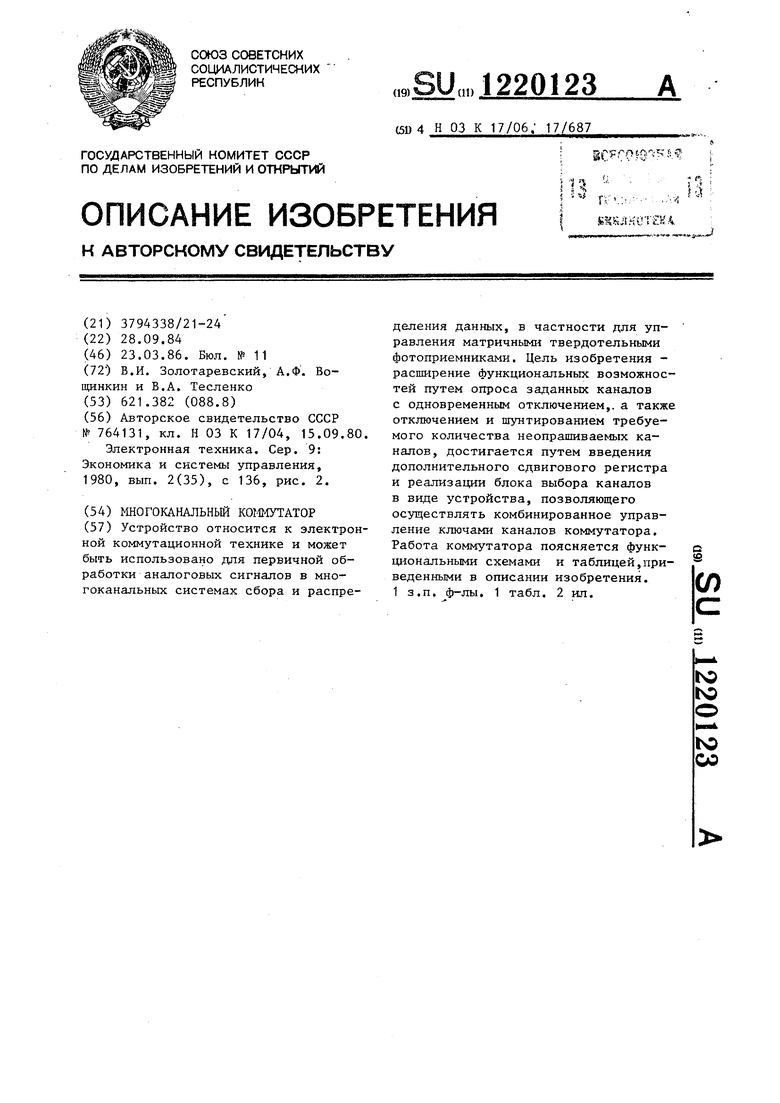

На фиг.1 приведена функциональная схема коммутатора; на фиг.2 - принципиальная схема преобразователя кода одного канала.

Устройство содержит первый 1 и второй 2 сдвиговые регистры с па- раллельньм считыванием всех h разрядов в прямом и инверсном зсодах, h преобразователей 3 кода, п групп логических элементов 4, устройство 5 выбора каналов, шину 6 запрета, первые 7 и вторые 8 аналоговые ключи, входные шины 9 каналов, первую 10 и вторую 11 выходные шины коммутатора.

Информационные входы,первого и второго регистров соединены с информационными шинами 12 я 13, а входы установки в нуль первого и второго регистров подключены к первой 14 и второй 15 шинам установки в нуль,

Тактовые входы обоих регистров соединены вместе и подключены к шине 16 тактового сигнала, входы разрешения опроса обоих регистров соединены с шиной 17 разрешения опроса, вход установки в единицу второго регистра подключен к Епине 18 установки в единицу. Шина 6 запрета соединена с входами всех элементов И м групп логических элементов 4. Исток пятого 1 -канального транзистора преобразователя кода подключен к шине 19 нулевого потенциала. Информацион- ные выходы первого и второго регистров подключены к выходньм информа

5 0

5

0

5

5 5055

232

ционным шинам 20 и 21 соответственно.

В каждом i -м канале ( i 1, 2, .,.,и) прямой и инверсный выходы одноименного разряда первого регистра соединены с первым 22 и вторым 23 входами преобразователя 3 кода, а прямой и инверсный выходы одноименного разряда второго регистра - с третьим 24 и четвертым 25 входами соответственно. Прямой выход одноименного разряда второго регистра, соединенный с третьим входом 24 преобразователя кода, подключен к первому входу первого элемента И группы логических элементов 4. Второй вход первого элемента И соединен с инверсными входами второго и третьего элементов И этой группы и с общей для всех каналов шиной 6 запрета. Первый 26 и второй 27 выходы преобразователя кода подключены к прямым входам второго и третьего элементов И группы логических элемен- тов 4 соответственно. Выходы первого и второго элементов И группы логических элементов 4 через элемент ИЛИ соединены с управляющим входом первого аналогового ключа 7. Выход третьего элемента И подключен к управляющему входу второго аналогового ключа 8.

Преобразователь 3 кода (фиг.2) содер кит первый 28, второй 29, третий 30, четвертый 31, пятый 32 h-канальные транзисторы, первьй 33 и второй 34 р -канальные транзисторы, а также общую шину 19. Сток первого h-канального транзистора 28 соединен с первым выходом 26 преобразователя кода и со стоками первого Р-канального транзистора 33 и второго п-канального транзистора 29, исток которого подключен к шине 19 нулевого потенциала. Затворы первого ь-канального 28, первого Р-канального 33 транзисторов, а также истоки второго р -канального 34 и третьего П-кангшьного 30 транзисторов соединены с первым входом 22 преобразователя кода. Исток первого h -канального транзистора 28 подключен к стоку четвертого п-канального транзистора 31, исток которого соединен с вторым входом 23 преобразователя кода. Затвор четвертого h -канального транзистора 31 подключен к истоку первого Р-канального транэистора 33, затвору третьего h -канального транзистора 30 и к треть(В- му входу 24 преобразователя кода. Затворы второго Р-канального 34, второго 29 и пятого 32 h-канальных транзисторов соединены с четвертым входом 25 преобразователя кода.Исток пятого h-канального транзистора 32 подключен к шине 19 нулевого потенциала, а сток его соединен со стоками второго р-канального 34 и третьего h-канального 30 транзисторов, а также с вторым выходом 27 преобразователя кода.

Устройство работает следующим образом.

При наличии разрешающего напряжения высокого уровня на шине t7 разрешения опроса и напряжения низкого уровня на шине 6 запрета сигналы управления i-м каналом коммутатора, поступающие на информационные шины 12 и 13 соответственно первого 1 и второго 2 регистров, по переднему фронту (-го тактового сигнала синхронно записываются в i-е ячейки этих регистров. Соответствующие сигналы с прямых и инверсных выходов этих ячеек поступают на входы 22- 25 преобразователя 3 кода, который преобразует информацию в одноименных ячейках регистров 1 и 2 в сигналы управления аналоговыми ключами. Сигналы управления аналоговыми ключами с первого 26 и второго 27 выходов преобразователя 3 кода через группу логических элементов 4 пос- TynaiipT на управляюш 1е входы первого 7 и второго 8 аналоговых ключей соответственно.

По переднему фронту (i+1)-ro тактового сигнала информация с i-х ячеек регистров перезаписывается в (|+1)-е ячейки, а в i-е ячейки перезаписывается информация с (-1)

ячеек. Таким образом, каждый из каналов устройства, в том числе и опрашиваемый, управляется соответствующими сигналами в течение времени, равного периоду тактового сигнала Т.

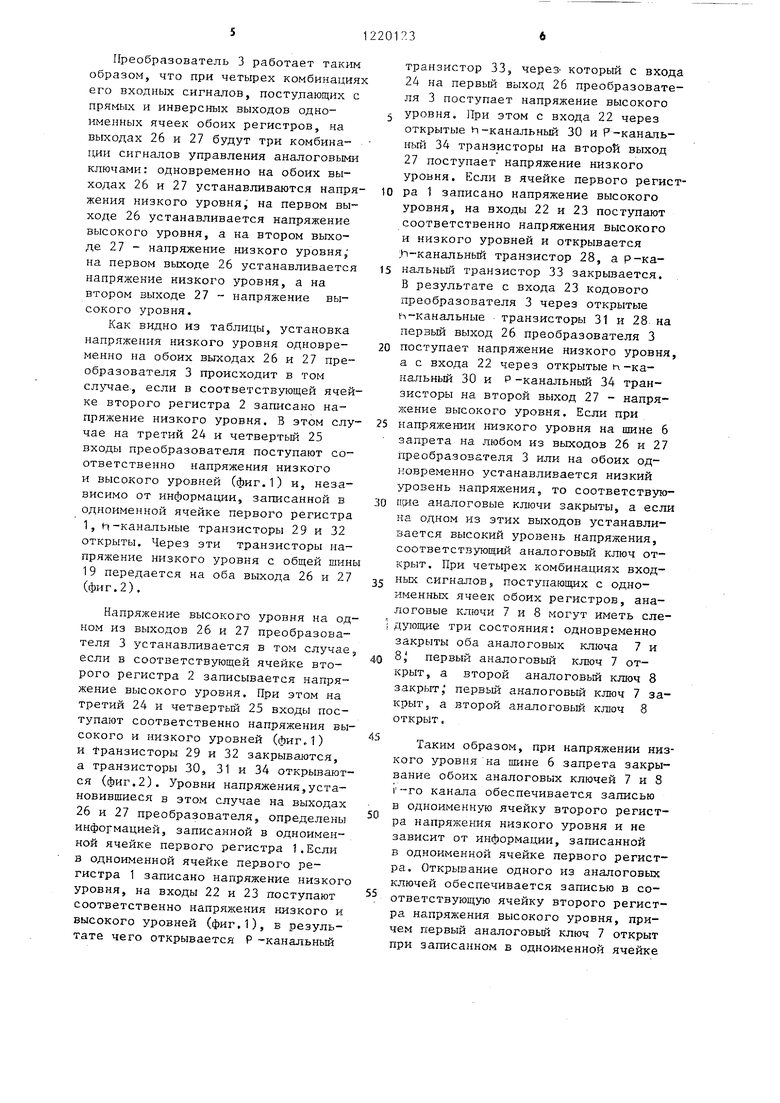

Работа преобразователя кода 3 4-го канала, а также состояние аналоговых ключей 7 и 8 соответствующего канала в зависимости от сигналов,

поступающих с прямых и инверсных выходов одноименных ячеек обоих регистров на входы 22-25 кодового преобразователя, и от уровня напряжения на шине 6 запрета иллюстрируется

таблицей (О и 1 - напряжения низкого и высокого уровней).

Закрыт

Преобразователь 3 работает таким образом, что при четырех комбинациях его входных сигналов, постудающих с прямых и инверсных выходов одноименных ячеек обоих регистров, на выходах 26 и 27 будут три комбинации сигналов управления аналоговыми ключами: одновременно на обоих выходах 26 и 27 устанавливаются напряжения низкого уровня, на первом выходе 26 устанавливается напряжение высокого уровня, а на втором выходе 27 - напряжение низкого уровня, на первом выходе 26 устанавливается напряжение низкого уровня, а на втором выходе 27 - напряжение высокого уровня.

Как видно из таблицы, установка напряжения низкого уровня одновременно на обоих выходах 26 и 27 преобразователя 3 происходит в том случае, если в соответствующей ячейке второго регистра 2 записано напряжение низкого уровня. В этом случае на третий 24 и четвертый 25 входы преобразователя поступают соответственно напряжения низко го и высокого уровней (фиг.1) и, независимо от информации, записанной в одноименной ячейке первого регистра 1, h-канальные транзисторы 29 и 32 открыты. Через эти транзисторы напряжение низкого уровня с общей шин 19 передается на оба выхода 26 и 27 (фиг.2).

Напряжение высокого уровня на одном из выходов 26 и 27 преобразователя 3 устанавливается в том случае если в соответствующей ячейке второго регистра 2 записывается напряжение высокого уровня. При этом на третий 24 и четвертый 25 входы поступают соответственно напряжения высокого и низкого уровней (фиг,1) и транзисторы 29 и 32 закрывалзтся, а транзисторы 30, 31 и 34 открываются (фиг.2). Уровни напряжения,установившиеся в этом случае на выходах 26 и 27 преобразователя, определены информацией, записанной в одноименной ячейке первого регистра 1.Если в одноименной ячейке первого регистра 1 записано напряжение низког уровня, на входы 22 и 23 поступают соответственно напряжения низкого и высокого уровней (фиг.О, в результате чего открывается Р -канальный

0

5

0

. ;

0

5

транзистор 33, через- который с входа 24 на первый выход 26 преобразователя 3 поступает напряжение высокого уровня. При этом с входа 22 через открытые h-канальный 30 и Р-канальный 34 транзисторы на второй выход 27 поступает напряжение низкого уровня. Если в ячейке первого регистра 1 записано напряжение высокого уровня, на входы 22 и 23 поступают соответственно напряжения высокого и низкого уровней и открывается ;и канальный транзистор 28, а р-ка- нальньш транзистор 33 закрьюается. . В результате с входа 23 кодового преобразователя 3 через открытые h-канальные транзисторы 31 и 28 на первый выход 26 преобразователя 3 поступает напряжение низкого уровня, а с входа 22 через открытые и-канальный 30 и Р-канальньй 34 транзисторы на второй выход 27 - напря- лшние высокого уровня. Если при напряжении низкого уровня на оине 6 запрета на любом из выходов 26 и 27 Преобразователя 3 или на обоих одновременно устанавливается низкий уровень напряжения, то соответствую- n.riie аналоговые ключи закрыты, а если на одном из этих выходов устанавливается высокий уровень напряжения, соответствующий аналоговый ключ открыт. При четырех комбинациях входных сигналов, поступающих с одноименных ячеек обоих регистров, аналоговые ключи 7 и 8 могут иметь сле- 1 д аощие три состояния: одновременно закрыты оба аналоговых ключа 7 и 8 первый аналоговый ключ 7 открыт, а второй аналоговый ключ 8 закрыт, первый аналоговый ключ 7 закрыт, а второй аналоговый ключ 8 открыт.

Таким образом, при напряжении низкого уровня на шине 6 запрета закрывание обоих аналоговых ключей 7 и 8 I -го канала обеспечивается записью в одноименную ячейку второго регистра напряже шя низкого уровня и не зависит от информации, записанной в одноименной ячейке первого регистра. Открывание одного из аналоговых ключей обеспечивается записью в соответствующую ячейку второго регистра напряжения высокого уровня, причем первый аналоговый ключ 7 открыт при записанном в одноименной ячейке

первого регистра напряжении низк-ого уровня, а второй аналоговый ключ 8 - при записанном в этой ячейке напряжении высокого уровня.

При напряжении высокого уровня на шине 6 запрета независимо от информации, записанной в i-и ячейке первого регистра, возможны следующие состояния ключей 7 и 8: оба аналоговых ключа 7 и 8 закрыты, если в одноименной ячейке второго регистра записано напряжение низкого уровня; первый аналоговый ключ 7 открыт, а второй аналоговый ключ 8 закрыт,если в одноименной ячейке второго регистра записано напряжение высокого уровня.

Отключение второго аналогового ключа 8 и включение первого аналогового ключа 7, т.е. отключение канала по второму выходу 11 и шунтирование его по первому выходу 10 при напряжении высокого уровня на шине

6запрета, в отличие от такого же состояния этих ключей при низком напряжении на шине 6 запрета, происходит при сохранении в ячейках обоих регистров 1 и 2 информации, соответствующей адресу канала, опрашиваемого по второму выходу 11.

Структурная организация предлагаемого устройства обеспечивает его работу в режиме последовательного опроса каналов, режиме параллельного опроса нескольких каналов при управлении последовательным кодом (режим преобразователя последовательного кода в параллельный),режиме Iпогруппового опроса каналов.Б режиме последовательного опроса каналов устройство может работать:

а)С отключением неопрашиваемых каналов по первому выходу 10. Данный режим обеспечивается подачей на информационную шину 12 первого регистра постоянного напряжения низкого уровня. Опрос каналов осуществляется сигналами высокого уровня, подаваемыми на информационную шину 13 второго регистра. При этом в последовательно опрашиваемых каналах открыты первые аналоговые ключи 7 (опрос каналов по первому аналоговому выходу 10), а во всех неопрашиваемых каналах оба аналоговых ключа

7и 8 закрыты.

б)С отключением неопрашиваемых каналов по второму выходу 11. Этот

режим обеспечивается подачей на информационную шину 12 первого регистра постоянного напряжения высо- с кого уровня. Опрос каналов, как и в предыдущем случае, осуществляется сигналами высокого уровня, подаваемыми на информационную шину 13 второго регистра. В последовательно оп- O рашиваемых каналах при этом открыты вторые аналоговые ключи 8, а во всех неопрашиваемьгх каналах оба аналоговых ключа 7 и 8 закрыты.

в)С отключением и шунтировани- 5 ем неопрашиваемьгх каналов. Данный

режим может быть реализован при опросе каналов как по первому 10, так и по второму 11 выходам. Режим обеспечивается подачей на информацион0 ную шину 13 второго регистра постоянного напряжения высокого уровня. Опрос каналов по первому аналоговому выходу 10 осуществляется сигналами низкого уровня, а опрос каналов по

5 второму аналоговому выходу 11 осуществляется сигналами высокого уровня.

При опросе каналов по первому выходу 10 в последовательно опрашиваемых каналах открыты первые ана-

0 логовые ключи 7, во всех неопрашиваемых каналах - вторые аналоговые ключи 8, а при опросе каналов по второму выходу 11 в последовательно опрашиваемых каналах открыты вторые

5 аналоговые ключи 8, а во всех неопрашиваемых каналах - первые аналоговые ключи 7.

г)С одновременным отключением, а также с отключением и шунтирова0 нием неопрашиваемых каналов (комбинированное управление аналоговыми ключами). Этот режим (аналогично предыдущему) может быть реализован при ohpoce каналов коммутатора как

5 по первому 10, так и по второму 11 1 выходам.

Режим обеспечивается подачей на информационную шину 13 второго регистра управляющего сигнала высокого уровня, по длительности перекрывающего на п -е количество тактовых сигналов управляющий сигнал, поступающий на информационную шину 12 первого регистра. В случае опроса каналов по первому выходу 10 на информационную шину 12 первого регистра подается управляющий сигнал низкого уровня, а при опросе каналов по вто0

рому выходу 1 1 - управляющий сигнал высокого уровня, Кп.тт чество опрашиваемых каналов по одному из аналоговых выходов 10 и 11 определяется числом и длительностью соответствующих управляющих сигналов; поступающих на информационную шину 12 первого регистра и совпадающих по времени с управляющим сигналом высокого уровня на информационной шине 13 второго регистра Количество каналов, находящихся в состоянии отключения и шунтирования определяется общим количеством тактовых сигналов, перекрь - ваемых управляющш- сигналом высокого уровня, поступающим на информационную шину 13 второго регистра до и после опрашиваемого канала. Остсшь™ ные каналы отключены по обоим выходам ,

Меняя за/цержки переднего и заднего фронтов управляющего сигналаg поступающего на информационный вход 13 второго регистра, можно регулировать число каналов, находящихся в состоянии отключения и шунтирования а также в состоянии отключения по обоим выходам как до, так и после опрашиваемого канала.

В режиме последовательного огфо- са при подаче напряжения низкого уровня на шину 17 разрешения опроса информация во всех разрядах обоих регистров, а следовательно, и состояние ключей всех кана,пов сохраняются как при поступлении тактовых сигналов на шину 16 тактового сигнала., так и при подаче на нее напряжения низкого уровня.

В режиме параллельного опроса нескольких каналов по одному из выходов 10 и 11 при управлении последовательным кодом и временном разделении записи информации и опроса каналов устройство работает ciHano- гично преобразователю последовательного кода в параллельный При этом записываемая информация гфедстав-- лена в виде соответстБ; тощих сигналов, подаваемых последовательно на инфор мационную шину 12 первого ре™ г-истра при одновременной подаче на информационную шину 13 второго ре ; гистра напряжения низкого уровня. После окончания записи информации в первый регистр на шину 18 установки в единицу второго регистра подается сигнал высокого уровня и информаидия

0

n

5

5

соответствующая адресам параллельно опрашиваемых каналов, через преобразователи 3 кода и группы логических элеь ентов поступает на управляю - вдие входы аналоговых ключей.

В режиме погруппового опроса m кан.алов по одному из выходов 10 и 11 на информационную шину 13 второго регистра необходимо подать сигнал высокого уровня, перекрывающий гп тактовых импульсов, а на информационную тику 12 первого регистра - сигнал такой же длите тькости, но низкого уровня, если опрос осуществляется по периом:-/ выход3- 10, иля сигнал высокого уровня, если опрос осуществляется по второму выходу 11

Такш образом 5 введение в многоканальный коммутатор дополнительных элементов позволяет посредством выбора соответств;.1ощих последователь- ньк комбинаций управляющих сигналов, синхронно поступающих в оба регистра по 11езавис1-1мья.1 информационньк шинам,, осуществлять одновременный оп- :;юс- каналов J откл очение5 а также тк.шочение и шунтирование неопраши- заемых каналюв,; т„е. реализовать ;чог-5 бинкрованное управление аналого- ::;ьп-:к ключами что особенно необходи- lio ДЛЯ первичной обработрси аналого- сиг налрв при опросе матричных твердотельньях фотоприемньк устройств, так как позволяет посредством отклю- чапия н гцунтирования каналов, близле- г/шгцкх к опрагпиваемому, значительно уг. вньшить величину помех наводок, зюзникающих на высокоомных датчиках фотоприемных устройс;тп, а пос- ); адствсм отключения по обоим выхо- /там остальных каналов - leньDшть ТОКЕ утечки блоков первичной обработки аналоговых сигналов. Этот суммарный эффект приводит к повышенр:ю эффективной пороговой чувствитель- посты и улучюенг-ш) разрешающей спо- еобности матричных твердотельных фо- топркзмников,, а значит, и повышению точности многоканальных систем сбо- Г- а и распределения данных в целом.

Ф о р к у л а

изобретения

1 .Многоканальпьй коммутатор,содер- кашд-гй коммутирующее устройство, состо- ящее из первых и вторых аналоговых ключей соответственно в каяодомканале,первый --разрядный сдвиговый регистр с параллельным считыванием всех разрядов и устройство выборки каналов с шиной запрета, сигнальные входы обоих аналоговых ключей каждого канала объединены и подключены к входной шине того же канала, объединенные выходы всех первых аналоговых ключей подключены к первой выходной шине, а объединенные выходы всех вторых аналоговых ключей - к второй выходной шине коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен второй сдвиговый регистр, а устройство выборки каналов содержит и преобразователей кода и h групп логических элементов, прямой и инверсный выходы первого сдвигового регистра в каждом разряде соединены соответственно с первым и вторым входами одноименного преобразователя кода, а прямой и инверсный выходы того же разряда второго сдвигового регистра соединены соответственно с третьим и четвертьм входами того же преобразователя кода, прямой выход одноименного разряда второго сдвигового регистра подключен к первому входу первого элемента И соответствующего канала, второй вход которого соединен с ин- версньми входами второго и третьего элементов И всех каналов и подключен к шине запрета, первый и второй выходы преобразователя кода в ка;к- дом канапе подключены соответственно к прямым входам второго и третьего элементов И того же канала, выходы первого и второго элементов И через элемент ИЛИ подключены к управляющему входу первого аналогового

ключа соответствующего канала, а управляющий вход второго аналогового ключа подключен к выходу третьего элемента И соответствующего канала.

2, Коммутатор по п.1, отличающийся тем, что каждый из и преобразователей кода содержит

пять h -канальных и два Р -каналь- ных МДП-транзисторов, сток первого h-канального МДП-транзистора объединен со стоками второго п -канального и первого Р -канального МДПтранзисторов и подключен к первому

выходу преобразователя кода, затво- ры первых h- и Р -канальных МДП-тран- зисторов объединены с истоками второго Р-канального и третьего

п-канального МДП-транзисторов и подключены к первому входу преобразователя кода, исток первого и -канального МДП-транзистора подключен к стоку четвертого h-канального

МДП-транзистора, исток которого соединен с вторым входом преобразователя кода, затворы третьего и четвертого h-канальных ВДП-транзисторов объединены с истоком первого р -канального МДП-транзистора и подключены к третьему входу преобразователя кода, затворы второго р-канального и второго и пятого -канальных МДП-транзисторов объединены

и подключены к четвертому входу

преобразователя кода, стоки третьего и пятого h-канальных и второго р-канапьного МДП-транзисторов соединены с вторым входом преобразователя кода, истоки второго и пятого h-канальных МДП-транзисторов соединены с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый ключ | 1980 |

|

SU928645A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ (ВАРИАНТЫ) | 2011 |

|

RU2465684C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СЧИТЫВАНИЯ ДЛЯ ФОТОПРИЕМНИКОВ | 2007 |

|

RU2357323C1 |

| Регистр сдвига | 1976 |

|

SU587507A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

| Триггер на взаимодополняющих мдп-транзисторах | 1980 |

|

SU875596A1 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| Устройство для извлечения многозначного ответа из ассоциативного накопителя | 1981 |

|

SU970470A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

Устройство относится к электронной коммутационной технике и может быть использовано для первичной обработки аналоговых сигналов в многоканальных системах сбора и распределения данных, в частности для управления матричными твердотельными фотоприемниками. Цель изобретения - расширение функциональньк возможностей путем опроса защанньк каналов с одновременным отключением,, а также отключением и шунтированием требуемого количества неопрашиваемых каналов, достигается путем введения дополнительного сдвигового регистра и реализации блока выбора каналов в виде устройства, позволяющего осуществлять комбинированное управление ключами каналов коммутатора. Работа коммутатора поясняется функциональными схемами и таблицей,приведенными в описании изобретения, 1 3.п. ф-лы, 1 табл. 2 Ш1, i (Л h ю k ND СО

Редактор О. Бугир

Составитель Б. Лементуев Техред 0.Сопке Корректор А. Зимокосов

1332/60

Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35.. Раушская наб., д, 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная,4

| Многоканальный коммутатор с переменным циклом опроса | 1978 |

|

SU764131A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электронная техника | |||

| Сер, 9: Экономика и системы управления, 1980, вып, 2(35), с 136, рис, 2, | |||

Авторы

Даты

1986-03-23—Публикация

1984-09-28—Подача