Извест-ны логические элементы «И-ИЛР1НЕ/И-ИЛИ, со де|ржа1цие (входные мяогоэмиттерные Т1ра1нз1И.стОры, коллекторы кот10;рых соединены с базами транзисторов-расширителей, а также прямой и ииверСный выходные каока1ды.

Цель изобретения - увеличение коэффициента раз-ветвления то каждому выходу, уменьшение задержки и мплльсав и мощности рассенваиия.

Это до.отитается тем, что устройство содержит парафаз-ный усилитель на транзисторах с объединенными база.ми, коллекторы которых через змйттерные повторители подключены к базам нагрузочных транзисторов выходных каскадов, вы,пол«е«ных по 1каскадн1ой схеме, эмиттер первого тра1НЗ(И:стара парафазного усилителя через лоследовательно включенный транзистор связи подключен к базе инве|ртируюш,его транзистора прямого выходного «аскада, эмиттер второго тра.нзистора ларафазного усилителя соединен с базой транзистора связи; с коллекторами транзисторов-расш.ирителей, эмиттеры .которых .подключены к базе инвертируюш.его транзистора инвероио-го выходного каскада.

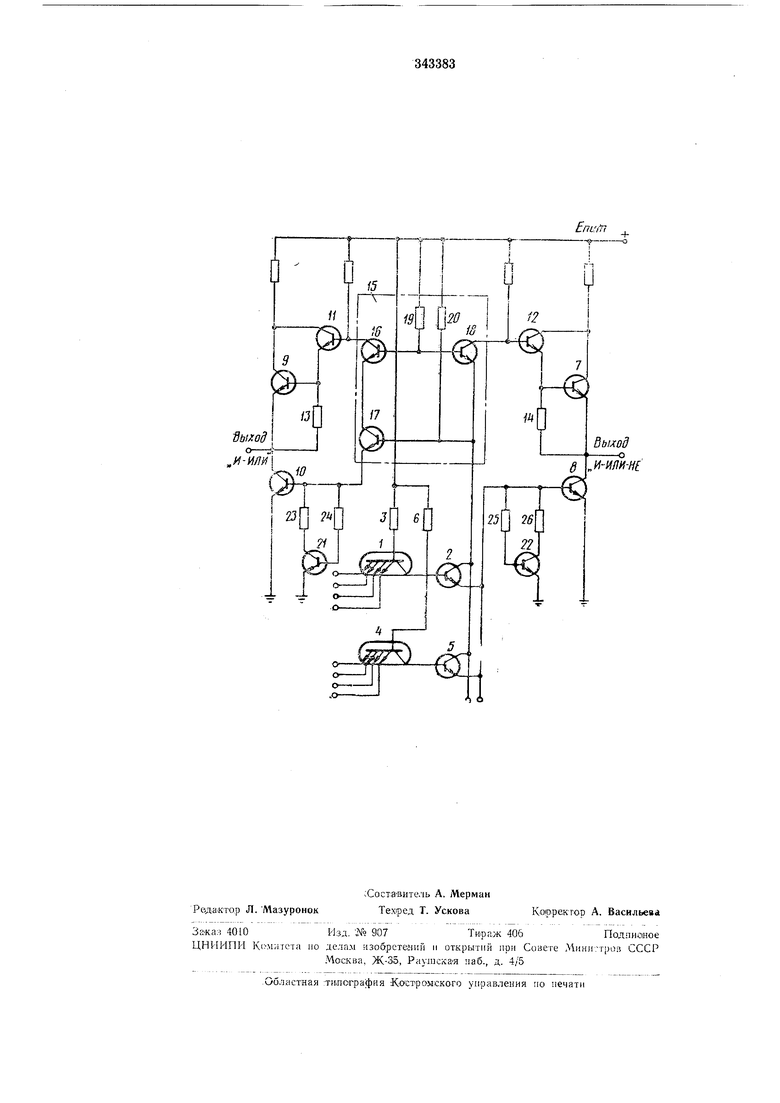

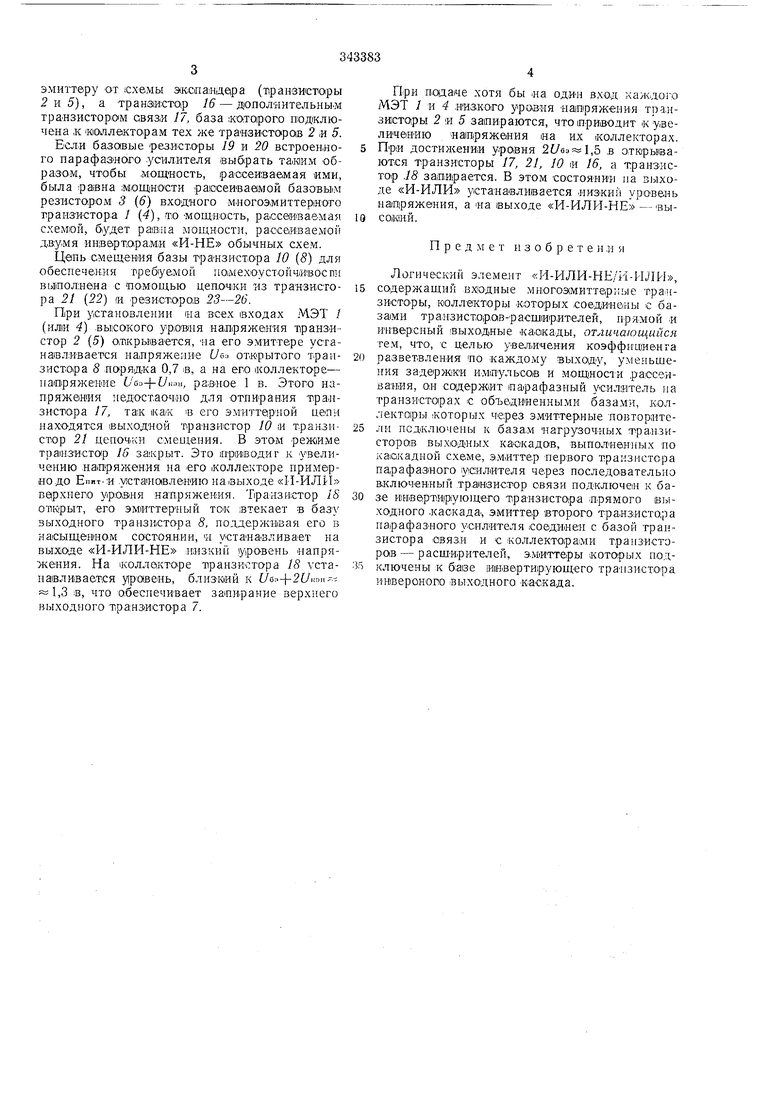

На чертеже приведена припцио-иальная схема чстройства.

)

выполненный .на многоэмиттерных транзисторах (МЭТ) / п 2, а также резисторе 3, либо на транзисторах 4 и 5, а также резпстаре 6.

Схема содержит два выхо.да: прЯМой «И-ИЛИ и инверсный «И-ИЛИ-НЕ. Инверсный выход осуществляется с транзисторов 7 и 8, а прямой - с тр.анзисторОВ 9 и 10. включенных по «каскадной схеме. Управление верхН их транзисторов 9 и 7 осун1ествлястся с эмнттерных повторителей П и 12, эмиттерныс резисторы которых 13 и 14 в целях экономии мопхмостп .включены на выхо.ды схемы.

В стройстве имеется «схема связки 15, состояп ая из транзисторов /6, 17 п 18. а также резисторов 19 ,и 20, представляюнии собой по функш онально1му назначению парафазный фазорасп1еп}1тельный каскад. ооес почивающий:

-свя31 вх.одных экспандерон с прямым п инверсны м 1БЫходами;

- одновременное управление прямым и инверсным выходами схемы;

-резкое снижение перепада в точке подключетшя расширителей по «ИЛИ, что существенно уменьшает заэисимость задержки по любому из (ВЫХОДОВ от числа входоВ «ИЛИ.

Встроенный в схему парафазный усилитель выполнен на транзисторах 16 и 18 со связанными базами, что обеспечивает .их быстрое переключение. Транзистор 18 управляется по

эмиттеру от схемь экспакл&ра (транзисторы 2 и 5), а транз1№ст0|р 16 - дюполяительньш транзистором связи 17, база которого подключена ,к «юллекто-рам тех же траизисторав 2 ,и 5.

БсЛИ базовые резисторы 19 и 20 встроенного парафаз«01го усилителя выбрать таиим образОМ, чтобы мощность, рассеиваемая ими, была paiBHa мощности рассеиваемой базовы1М резистором 3 (6) входного многоамиттеряото гранзистора J (4), то мощность, рассеиваемая схемой, будет pa®iia мощности, рассеиваемой дву.мя инверторами «И-НЕ обычных схем.

Цепь смещения базы транзистора 10 (8) для обеспечения требуемой по мехоустойчивослн выполнена с помощью цепочки Из транзистора 21 (22 (И резисторов 23-26.

При установлении иа всех входах МЭТ / (или 4 высокого напряжения пранзистор 2 (5) открывается, на его эмиттере усганавл.ивается напряжение Уоа открытого транзистора 8 паряд.ка 0,7 в, а на его 1коллекторе- наоряжевие ббз+б/саы, ра;в«ое 1 в. Этого напряжения недостаОЧ|НО для отнирания транзистора 17, так как в его эмитте рной цепи находятся выходной пранзистор 10 м транзистор 21 цепоч-ки смещения. В этом реж1Нме транзистор 16 . Это ориводиг к увеличению напряжения на его коллекторе примерно до ЕПНТ.;И .у1ста1но1влен1ию на выходе «И-ИЛИ oeipxHero уровня напряжения. Транзистор iS открыт, его эмиттерный ток втекает в выходного транзистора 8, поддерживая его в насыщенном состоянии, и устанавливает на вьмоде «И-ИЛР1-НЕ низкий уровень напряжения. На коллекторе транзистора /(9 устана вли1вается у|ро(вень, близкий к L)5- -{-2lJ ™i 1,3 в, что 0;беснечивает затирание верхнего выходного транзистора 7.

При ноцаие хотя бы «а одИН вход каждого МЭТ 1 VI 4 .низкого уровня натряж-епия тра.нзи1сто:ры 2 и 5 затираются, что приводит «увеличению напряжения на их коллекторах. При достижении уровня 2 /вэ«;1,5 .в открываются транзисторы 17, 21, 10 и 16, а транзистор ./5 запирается. В этом состоянии на si ixoде «И-ИЛИ устанавливается низкий уровень надряжения, а «а выходе «И-ИЛИ-НЕ - высомий.

Предмет изобретен и я

Логический элемент «И-ИЛИ-НЕ/1i - ИЛИ,

содержащий входные многозмиттерные транзисторы, коллекторы которых соединены с базами транзисторов-расширителей, прямой и инверсный выходные 1ка1скады, отличающийся те.м, что, с целью увеличения коэффищиенга

разветвления но каждому выходу, уменьшения задержки импульсов и моЩ1НОС1И рассеивания, он содержит парафазный усилитель на транзисто рах с объединенными базами, коллекторы которых через эмиттерные повторители подключены к база.м нагрузочт1ых транзисторав выходных каскадов, выполненных по каскадной схеме, эмиттер первого транзистора парафазного усилителя через носледовательно включенный .транзистор связи подключея к базе И1нвертир|ующего транзистора прямого выходного .каскада , эмиттер второго транзистора парафазного усилителя соединен с базой транзистора связи и с .коллекторами транзнстэрОБ - расширителей, э.миттеры которых подключены к баве инвертирующего транзистора иввероного выходного каскада.

Ъыход .и-илм

Enufn

И-ИЛИ-flf

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Устройство для перемножения напряжений | 1977 |

|

SU667972A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Интегральный динамический элемент | 1971 |

|

SU559381A1 |

| Двухтактный усилитель мощности | 1988 |

|

SU1649640A1 |

| Дифференциальный усилитель | 1972 |

|

SU437193A1 |

| Компаратор | 1979 |

|

SU813753A1 |

| Универсальный логический элемент | 1973 |

|

SU446950A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

Даты

1972-01-01—Публикация