1

Изобретение относится к области вычислительной техники и Iможет применяться в цифровых вычислительных машинах и устройствах

В современных цифровых вычислительных машинах наря|ду с потенциальными системами элементов широко используются динамические или ; импульсные системы элементов.

Основными отличительными признаками динамических систем элементов являются; использование импульсного питания схем и наличие цепей для кратковременного хранения И1в{)ормации.

Существуют динамические системы элементов, использующие различные способы временного хранения ин|)ормации. Наиболее технологичными являются динамические элементы СЗапоминаЮ111йМ конденсатором и на основе регенеративного расширения 1 . Указанные схемы могут бмть выполнены в интегральном исполнении, -. что является желательнымусловием для каждой системы элементов.

Однако известные схемы имеют большое число подводимых шин тактирования, сложны: тактирующие импульсы, как праЬило, двуполярные, что затрудняет создание генераторов тактирующих импульсов в интегральном исполнении.

Для кратковременного хранения информации используется, например, триггер с непосредственными связями на многоэмиттерных транзисторах . Однако он не позволяет выполнять логические функции, кроме того, требует двуполярных входных импульсов.

Цель изобретения - обеспечить выполнение логических функций, И, ИЛИ с кратковременным хранением информации.

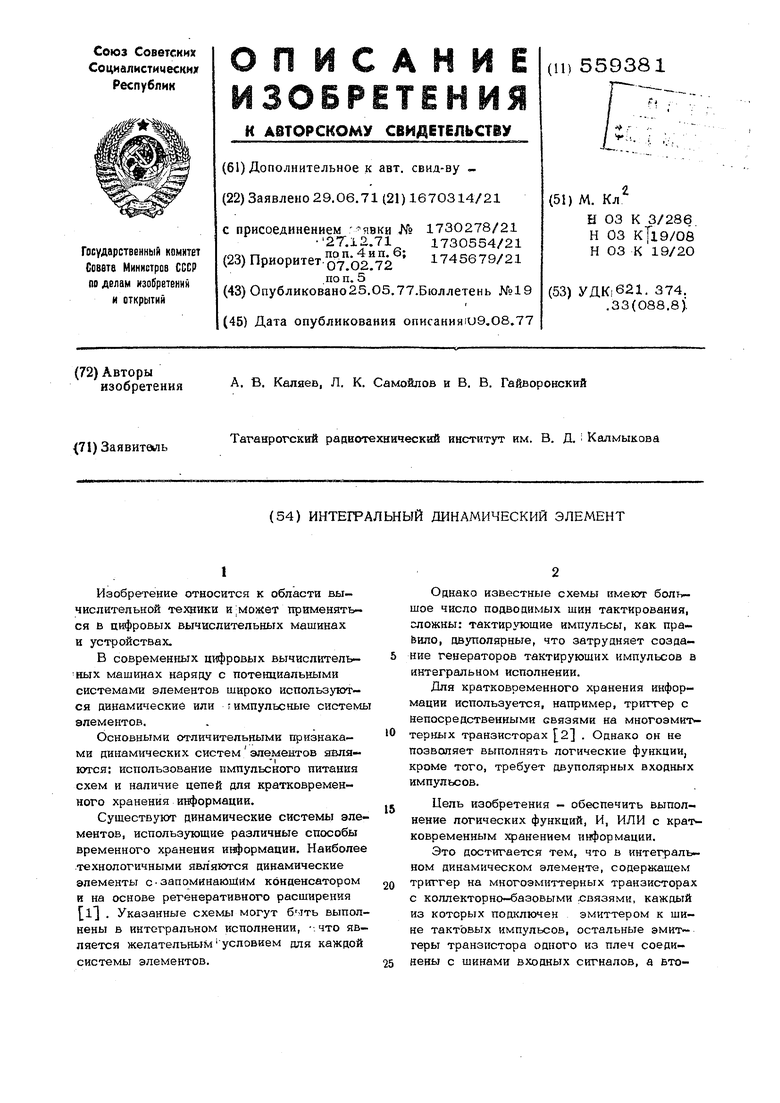

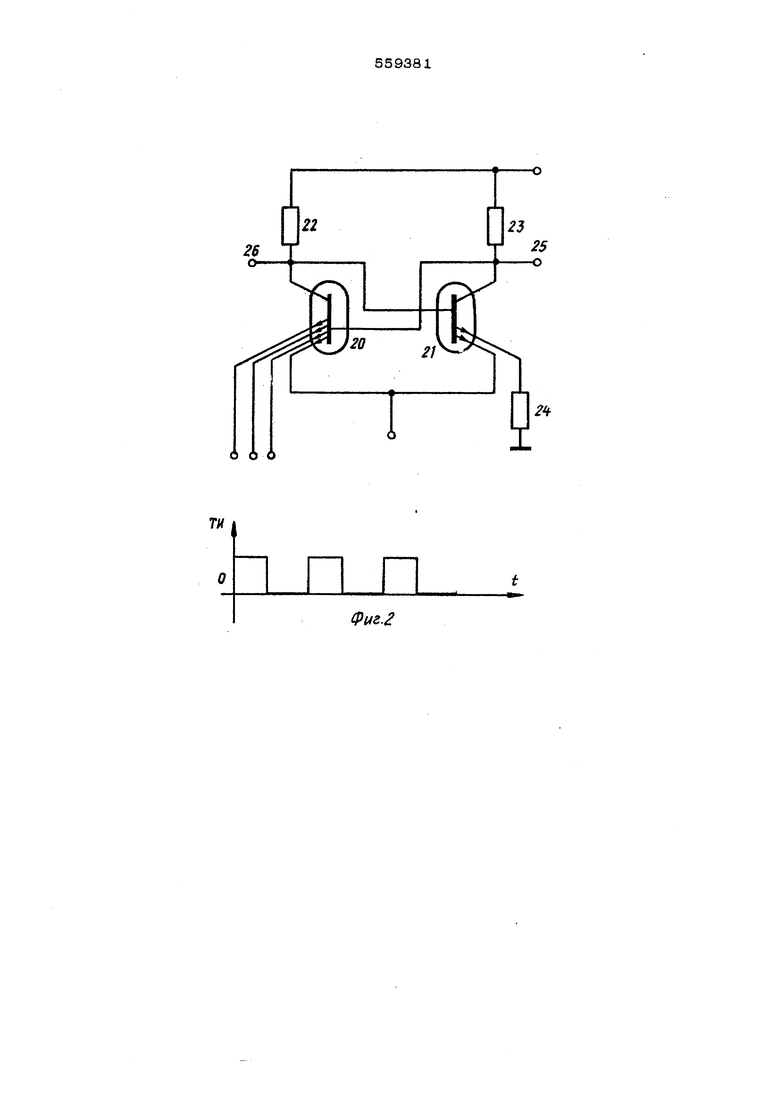

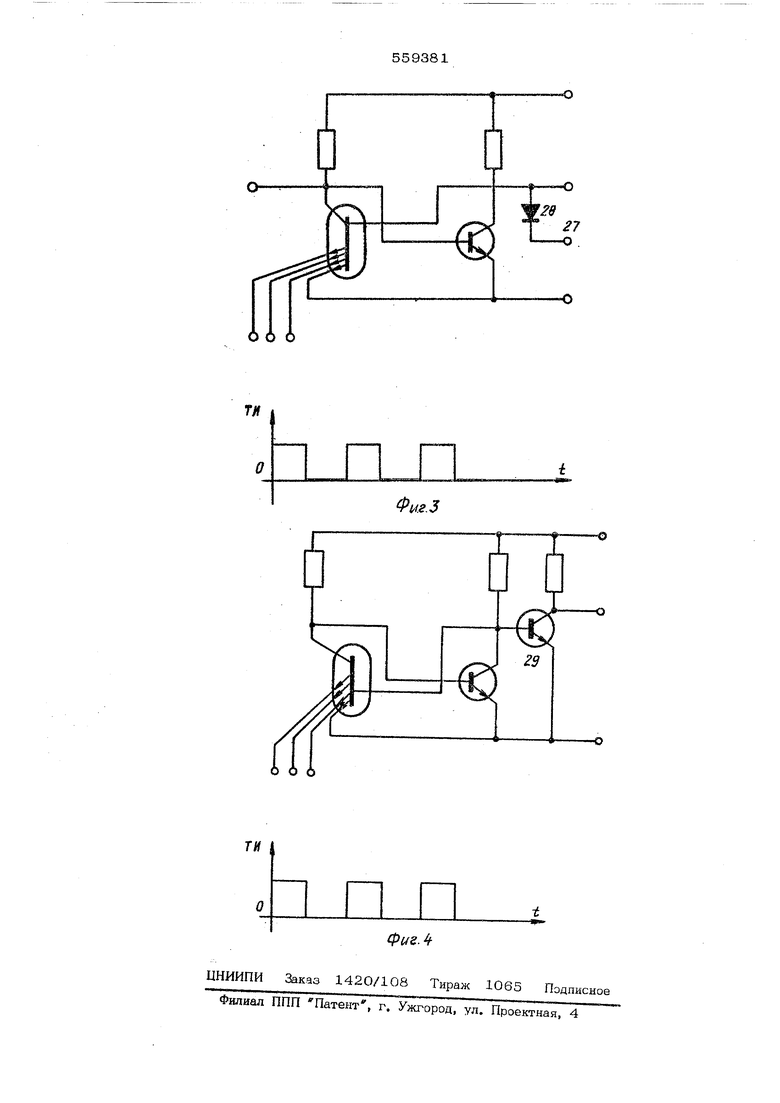

Это достигается тем, что в интегральном динамическом элементе, содержащем триггер на многоэмиттерных транзисторах с коллектор но-базовыми связями, каждый из которых подключен эмиттером к шине тактовых импульсов, остальные эмит- геры транзистора одного из плеч соединены с шинами входных сигналов, а второе плечо содержит средства асимметрии в виде активного сопротивления; средства асимметрии выполнены в виде резисто ров, включенных в -чэмиттерные цепи тран аистора, с целью повышения надежности, эмитггеры |транзистора второго плеча подкпючены к шинам парафазных входных ; сигналов; используемый в качестве сред-i ства асимметрии схемы резистор, включенный в эмиттерную цепь транзистора вт рого триггера, подключен к общей шине; в качестве средства асимметрии -Г,схемы использован транзистор, включенный по схеме с общим эмиттером, база которого соединена с коллектором транзистора второго плеча триггера, с целью получения дополнительного инвертированного выхода и возможности использования во втором плече триггера одноэмиттерного транзистора; в качестве средства асимметрии использован диод, подключенный v одним электродом к коллектору транзистора второго, плеча, а другим электродом - к источнику опорного напряжения, с целью фиксации уровня выходного сигнала и воз- можности использования во втором плече триггера одноэмиттерного транзистора. На фиг. 1 изображен интегральньтй динамический элемент с выходными усилите |ными каскадами на транзисторах, у которого асимметрия в плечи триггеров внесена с помощью дополнительных резисторов, включенных во входные : цепи элемента; на фиг. 2 - интегральный динамический элемент, 1у которого принудительная установка триггера в нулевое состояние ос5тцествляется с помощью резистора включенного в эми1;тррную цепь транзистора, второго плеча триггера; на фиг. 3интегральный динамический элемент с асимметрией, внесенной в плечи триггера с помощью источника напряжения и диода фиксаиин; на фиг. 4,- интегральный динамичес - кий элемент, у которого усилительный каскад на транзисторе, включенном по схеме с ОЭ, вносит асимметрию в плечи триггера, шун тируя переходом Э-Б базу мноГоэмиттер- ного транзистора на шину тактового напряжения, и обеспечивает возможность получения дополнительного инвертированного выхода. Работа всех перечисленных элементов идентична вследствие выполнения их на основе триггера с непосредственными связями и средствами ассиметрии в плечах, поэтому рассмотрим только элемент, изображенный на фиг. 1. Интегральный динамический элемент содержит прямые входы 1, 2 и 3 логиЧ1а лого элемента, вход 4 тактирующего напряжения, инверсные входы 5, 6 и 7 логического элеме1 та, дополнительные резисторы 8, 9 .и 10 для разбаланса, эмиттеры 11 и 12, подключенные ко входу тактирующего напряжения, многоэмитгерные транзисторы (МЭТ) 13 и 14, обхваченные перекрестными триггерными связями, резисторы 15 и 16 коллекторных нагрузок, напряжение 17 источника питания, инверсный выход 18 и прямой логический выход 19 логического элемента. Устройство работает следующим образом, В работе динамического элемента можно выделить два режима; режим образования (записи) логической функции и режим временного хранения полученной, логической функции. Тактирующее напряжение поступает на вход 4 (на объединенную пару эмиттеров 11 и 12), Информация в прямом коде подается на входы 1, 2, и 3, а в инверсном - на 5, 6 и 7. Установка нового состояния триггера происходит при подаче положительного тактирующего импульса напряжения на эмиттеры 11 и 12, которые закрываются. Ин- формация поступает на входы в парафазном коде. Единица информации кодируется вы-соким уровнем сигнала. Пусть на всех прямых входах высокие . уровни сигнала, тогда многоэмиттерный транзистор 13 закрывается по всем эмиттерам (на шине тактирования высокий уровень), а транзистор 14 открыт, так как на эмиттеры 5, 6 и 7 подается низкий уровень напряжения. Если на все прямые входы подается) низкий уровень напряжения, то на входы 5, 6 и 7 - высокие уровни (вследствие парафазного входа). При таком сочетании входных сигналов закрыт транзистор 14 по всем эмиттерам и открыт -транзистор 13, Пусть на rf прямых входах логического элемента низкий уровень напряжения (где П -i, 2), и, соответственно на т -инверсных входах - низкий уровень (где т3- п при общем числе информационных дов, равном трем). Объединенная пара эмиттеров отключена от схемы триггера (на шине тактирования высокий уровень). Вслед-. ствие несимметричности плеч триггера из-за резисторов 8, 9 и 10 создается преимущество у транзистора 13 к открыванию, положительная обратная связь приводит к открыванию транзистора 13 и закрывагшю транзистора 14. При этом на вы ход а 19 реализуется логическая функция И для прямых входов элемента, на выходе 18 функ-. ция - И-МЕ для высоких уровней инверсных входных сигналов. Тогда по правилу де-Моргана на выходе 19 - функция ИЛИ НЕ, а на выходе 18 - функция -ИЛИ для низких уровней входных сигналов, т.е. система элементов обладает функциональной полнотой. На выходе 18 реализуется логическая функция И для высоких уровней входных сигналов да входах 1, 2 и 3 На выходе 19 реализуется логическая фун ция ИЛИ для низких уровней входных сиг.налов на входах 5, 6 и 7. После образования нового состояния тр ,гера подается тактирующее напряжение, ра ное О. Обьединенные эмиттеры 11 и 12 шунтируются на землю, фиксируя новое состояние. При этом остальные эмиттеры транзисторов отключаются от схемы триггера. Интегральный динамический элемент, изображенный на .фиг. 2, состоит из одного многоэмиттерного транзистора (МЭТ 2О, одного двуэмиттерного транзистора 21; и коллекторных нагрузок 22 и 23. :Принцип его действия аналогичен элемен,ту, изображенному на фиг. 1. Разбаланс внесен резистором 24, соединяющим один из эмиттеров транзистора 21 с общей шиной (земля), 25 - инверсный выход элемента, 26 - прямой выход. Эмиттеры транзисторов обоих плеч триггера соедине с шиной тактирующего напряжения. В интегральном динамическом элементе, изображенном на фиг, 3, разбаланс внесен источником напряжения фиксации 2 и диодом 28. Интегральный динамический элемент, изображенный на фиг. 4, состоит из триггера на транзисторах с коллекторно-ба:зовыми связями и усилительного каскада на транзисторе 29, который выполняет функцию внесения разбаланса, а также,слу жит для получения дополнительного инверс ного значения информации.

Формула изобретения

1. Интегральный динамический элемент, содержащий триггер на многоэмиттерных транзисторах с коллекторно-базовыми свяИсточники информации, принятые во внимание при экспертизе:

1.Филиппов А. Г. Транзисторные ди:намические элементы ЦВМ. Л1.., Советское

радио , 1969.

2.Электроника, 1967, № 4, с. 42. зями, каждый из которых подключен эмиттером к шине тактовых импульсов, о т личающийся тем, что, с целью выполнения логических функций И, ИЛИ, остальные эмиттеры транзистора одного из плеч соединены с шинами входных сигналов, а| второе плечо содержит средства асимметрии в виде активного сопротивления. 2.Устройство по п. 1, о т л и ч а ощ е е с я тем, что средства асимметрии выполнены в виде резисторов, включенных в эмиттерные цепи транзистора. 3.Устройство по п. п. 1 и 2, о т г личающееся тем, что, с целью .повышения надежности, эмиттеры транзистора второго плеча подключены к шинам парафазных входных сигналов. 4.Устройство по п.п. 1 и 2, о т л ичающееся тем, что используемый в качестве средства асимметрии схемы резистор, включенный в эмиттерную цепь транзистора второго триггера, подключен к общей шине. 5.Устройство по п. 1, о т л и ч а ющ е е с я тем, что в качестве средства асимметрии схемы использован транзистор, включенный по схеме с обшим эмиттером, база которого соединена с коллектором транзистора второго плеча триггера, с целью получения дополнительного инвертированного выхода и возможности использования во втором плече триггера одноэмиттерного транзистора. 6.Устройство по п. 1, отлича ющ е е с я тем, что в качестве средства асимметрии использован диод, подключенный одним электродом к коллектору трак- знстора второго плеча триггера, а другим электродом - к источнику опорного напряжения, с целью фиксации уровня выходного сигнала и возможности использования во втором плече триггера одноэмиттерного транзистора.

18

567

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| Устройство преобразования однофазового логического сигнала в парафазный ток | 1976 |

|

SU570201A1 |

| Интегральный динамический элемент | 1980 |

|

SU906005A2 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ—НЕ» и «И-ИЛИ» | 1970 |

|

SU260680A1 |

| Многорежимный преобразователь постоянного напряжения | 1984 |

|

SU1243076A1 |

| -К триггер | 1975 |

|

SU790124A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Микромощный логический элементи-или/и-или-HE | 1979 |

|

SU832725A1 |

.f

Фиг.2

Авторы

Даты

1977-05-25—Публикация

1971-06-29—Подача