Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств вычислительных машин.

Известны запоминающие элементы на МОПтранзисторах, содержащие триггер с непосредственными связями, соединенный с двумя: разрядными и двумя координатными шинами с помощью двух пар проходных транзисторов..

Недостатком таких элементов является отсутствие автономных цепей управления в режимах записи и считывания, что снижает быстродействие ЗУ в целом.

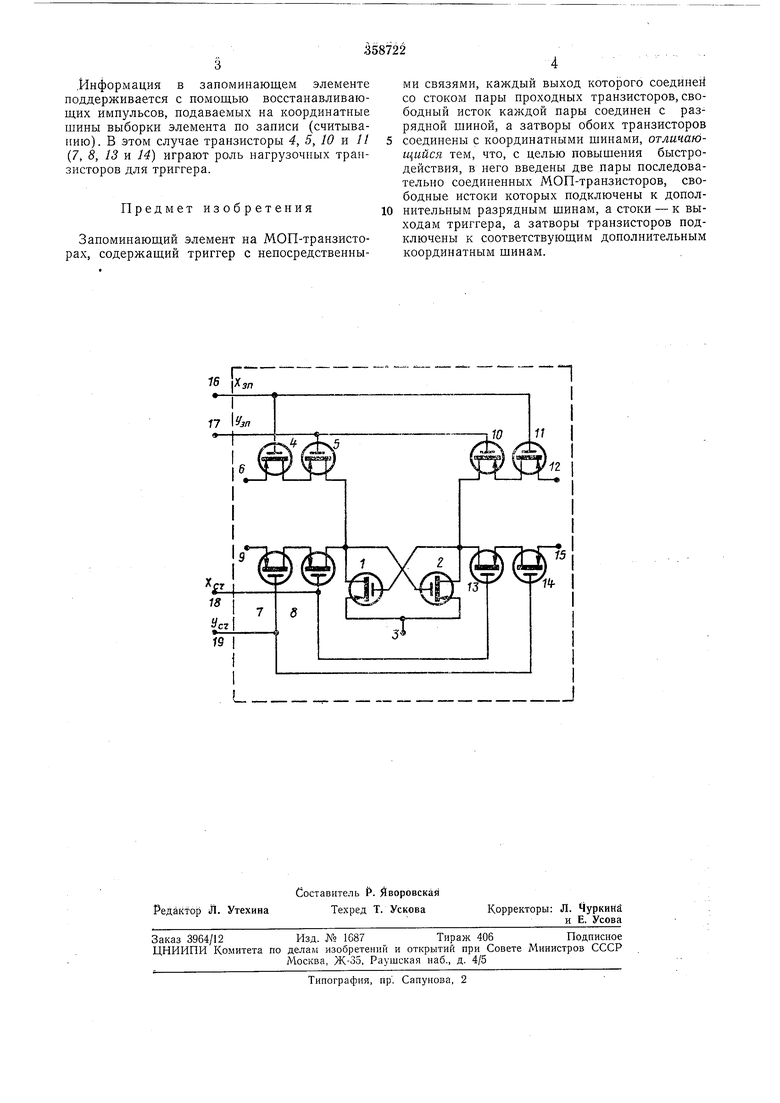

В предлагаемый элемент введены дополнительно две разрядные и две координатные шины и две пары последовательно соединенных МОП-транзисторов, свободные истоки которых подключены раздельно к дополнительным разрядным шинам, а стоки - к стокам транзисторов, образующих триггер. Затворы: транзисторов дополнительных пар, непосредственно соединенных по истоку с дополнительными разрядными щинами, подключены к одной из дополнительных координатных шин,. а затворы двух других дополнительных транзисторов - ко второй дополнительной координатной шине.

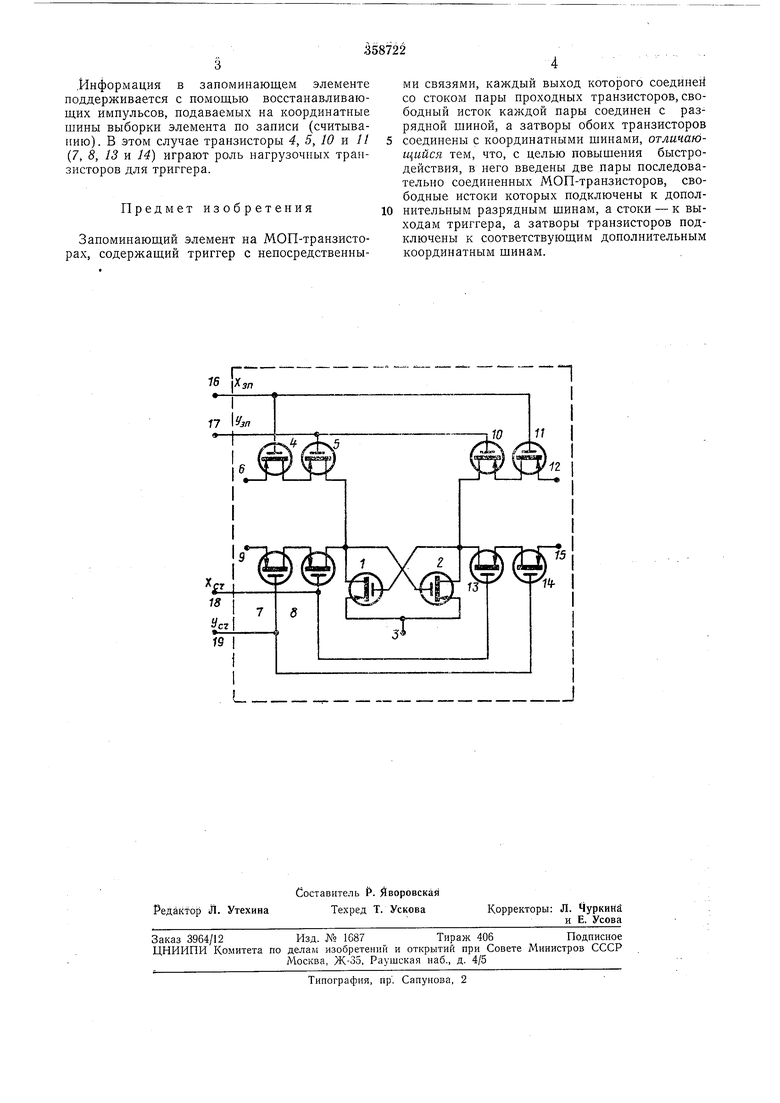

ми связями образован транзисторами 1 и 2, на объединенные истоки которых подается напряжение от постоянного источника питания

3.Одно плечо триггера через проходные транзисторы 4 и 5 соединено с разрядной щиной

«1 по записи 6, а через транзисторы 7 и S - разрядной шиной «1 по считыванию 9. Второе плечо триггера через проходные транзисторы 10 н И соединено с разрядной шиной «О

по записи 12, а через транзисторы 13 и 14 - с разрядной шиной «О по считыванию 15.

Затворы транзисторов 4 п 11 подключены к координатной щине выборки по записи Хзк 16, затворы транзисторов 5 и 11 - к координатной шине выборки по записи УЗП 17, затворы транзисторов 8 и 13 - к координатной щине выборки по считыванию сч 18, а затворы транзисторов 7 и 14 - к координатной шине выборки по считыванию УСЧ 19.

В режиме записи разрешающие уровни напряжения по координатным щинам выборки зп и УЗП открывают проходные транзисторы

4,5, 10, 11, и информация с разрядных щин «1 и «О по записи переписывается в триггер.

В режиме считывания разрешающие уровне напряжений по координатным щинам выборки Хсч и УСЧ открывают проходные транзисторы 7, 8, 13, 14, и информация из триггера поступает в разрядные щины «1 и «О по считыва.Информация в запоминающем элементе поддерживается с помощью восстанавливающих импульсов, подаваемых на координатные шины выборки элемента по записи (считыванию). В этом случае транзисторы 4, 5, 10 и 11 (7, 8, 13 и 14) играют роль нагрузочных транзисторов для триггера.

Предмет изобретения

Запоминающий элемент на МОП-транзисторах, содержащий триггер с непосредственными связями, каждый выход которого соединей со стоком пары проходных транзисторов, свободный исток каждой пары соединен с разрядной щиной, а затворы обоих транзисторов соединены с координатными щинами, отличающийся тем, что, с целью повышения быстродействия, в него введены две пары последовательно соединенных МОП-транзисторов, свободные истоки которых подключены к дополнительным разрядным шинам, а стоки - к выходам триггера, а затворы транзисторов подключены к соответствующим дополнительным координатным шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU343308A1 |

| ИНТЕГРАЛЬНАЯ МАТРИЦА НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU342222A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ | 1970 |

|

SU283307A1 |

| Накопитель постоянного запоминающего устройства с электрической записью информции | 1973 |

|

SU466552A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1336112A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU903982A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

| Квазистатическая ячейка памяти | 1974 |

|

SU541198A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

Даты

1972-01-01—Публикация