Предлагаемое устройство относится к области вычислительной техники и может быть использовано для построения накопителей запоминающих устройств без разрушения информации при считывании в универсальных и специализированных вычислительных машинах.

Известны запоминающие элементы без разрущсния информации при считывании для запоминающего устройства матричного типа с произвольной выборкой, содерлсащие триггер с двумя устойчивыми состояниями и перекрестными непосредственными связями на МОП-транзисторах, проходные и координатный МОП-транзисторы. Запись информации и считывание хранящегося кода производятся с помощью проходных и координатного МОПтранзисторов. Для снижения мощности рассеивания триггер подключеи к источнику питания с помощью восстанавливающих импульсов, периодически открывающих по затворам нагрузочные МОП-транзисторы.

Недостаткол таких элементов является больщая мощность рассеивания.

В предлагаемом элементе с целью уменьщения потребляемой мощности содержится две собирательные схемы, первые входы которых соединены с источником импульсного питания, вторые входы-с координатными щинамн выборки элемента; выходы собирательных схем

связаны соответственно с затвором координатного транзистора и с его истоком.

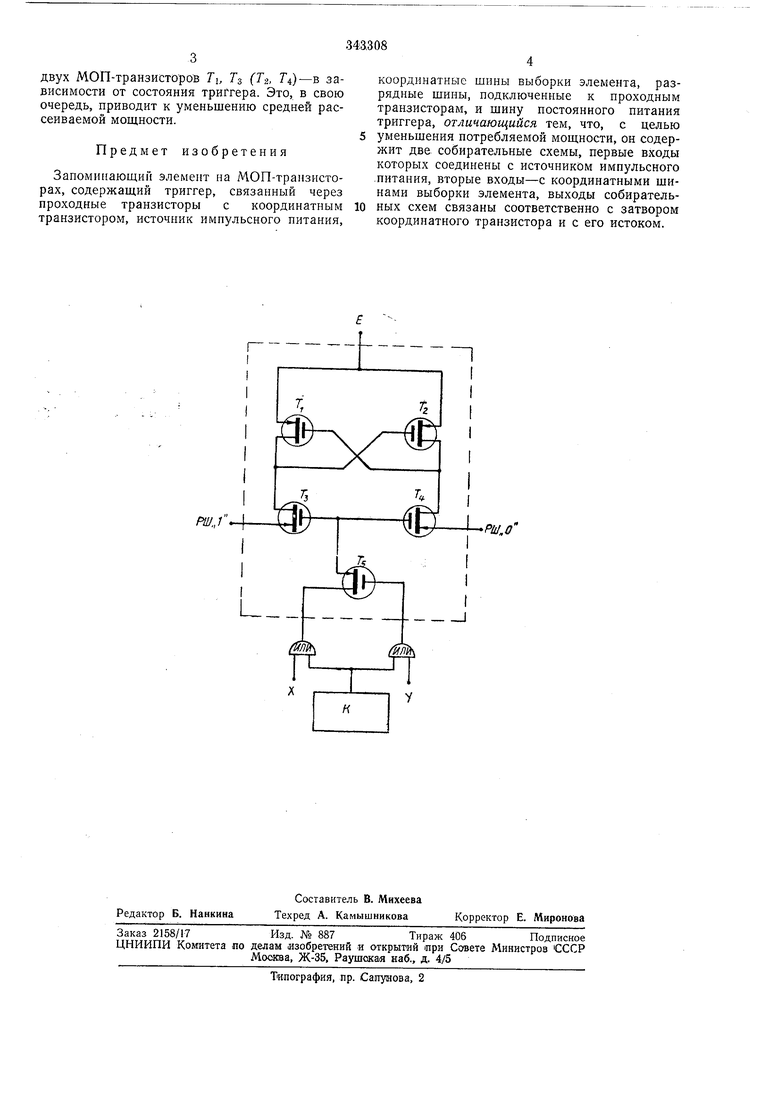

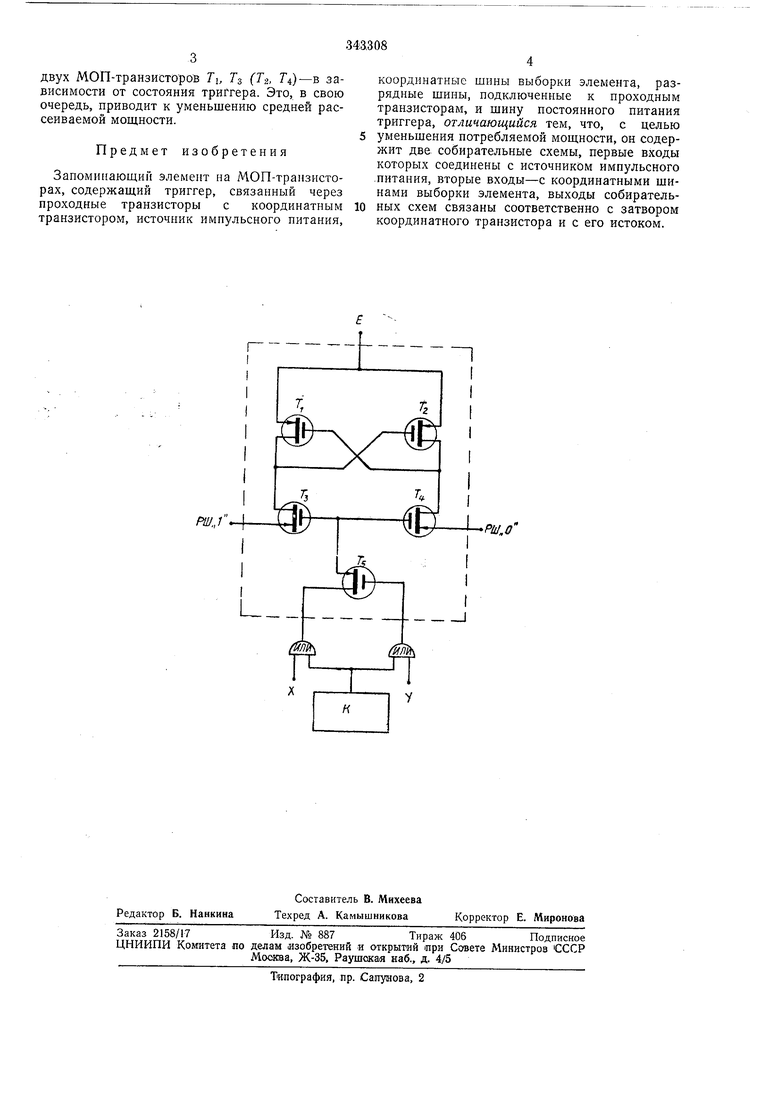

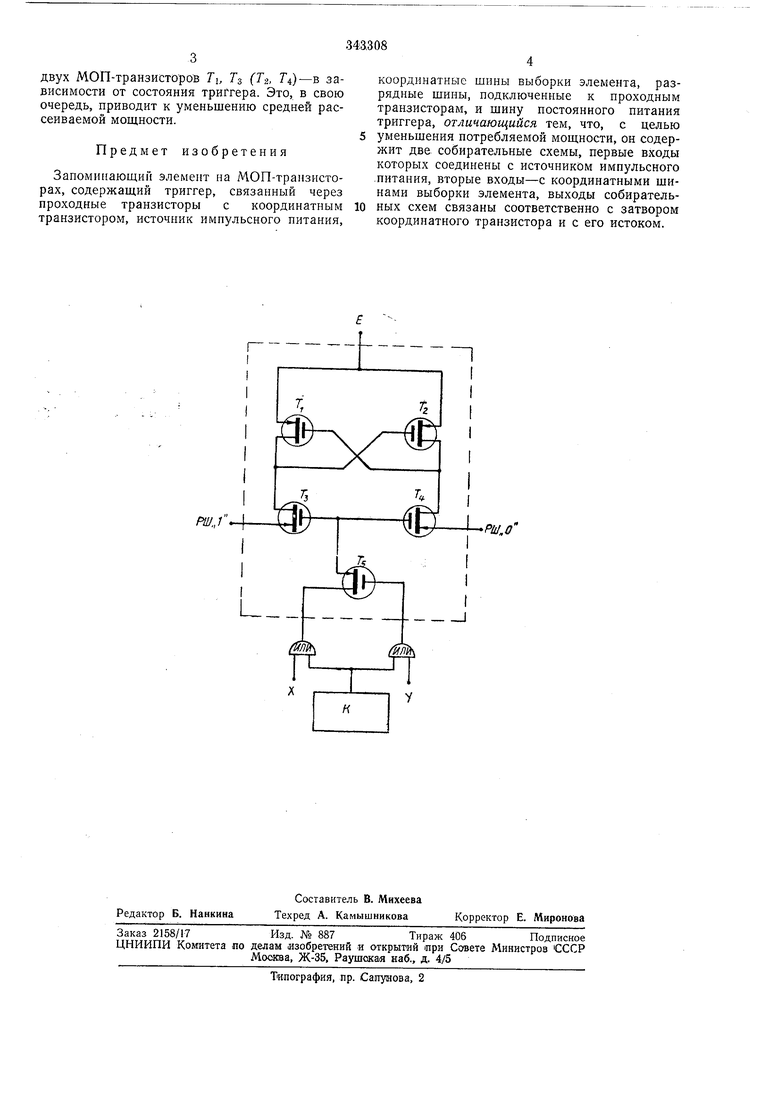

На чертеже показана принципиальная электрическая схема предлагаемого устройства.

Триггер с непосредственными перекрестными связями образован МОП-транзисторами Г и Т-2, на объединенные истоки которых подается напряжение от постоянного источника питания Е. Одно плечо триггера через проходной МОП-транзистор Гз соединено с разрядной щиной «1 {РШ«1), второе-через проходной МОП-транзистор разрядной щиной «О (РШ«0). Затворы МОП-транзисторов Гз и Т

соединены с истоком координатного МОПтранзистора TS, который по стоку и затвору через две собирательные схемы «ИЛИ связан с щпнами выборки элемента по координатам X н Y и источником импульсного питания /С.

В режиме хранения информации восстанавливающие импульсы подаются на сток и затвор координатного МОП-транзистора Т. При этом импульсы с выхода Т открывают по затворам Тз и Т, которые на время действия импульсов играют роль нагрузочных МОП-транзисторов.

двух МОП-Транзисторов Ti, Тз (Тг, Т)-в зависимости от состояния триггера. Это, в свою очередь, приводит к уменьшению средней рассеиваемой мощности.

Предмет изобретения

Запоминающий элемент на МОП-транзисторах, содержащий триггер, связанный через проходные транзисторы с координатным транзистором, источник импульсного питания.

координатные шины выоорки элемента, разрядные шины, подключенные к проходным транзисторам, и щину постоянного питания триггера, отличающийся тем, что, с целью

уменьшения потребляемой мощности, он содержит две собирательные схемы, первые входы которых соединены с источником импульсного ,питания, вторые входы-с координатными шинами выборки элемента, выходы собирательных схем связаны соответственно с затвором координатного транзистора и с его истоком.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU358722A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Накопитель постоянного запоминающего устройства с электрической записью информции | 1973 |

|

SU466552A1 |

| ИНТЕГРАЛЬНАЯ МАТРИЦА НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU342222A1 |

| ЯЧЕЙКА ПАМЯТИ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU326641A1 |

| Постоянное запоминающее устройство | 1973 |

|

SU444246A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU335720A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU903982A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

т, Г

Даты

1972-01-01—Публикация