Изобретение отиосится к области выч слительной техники.

Известны запомииа ощие устройства иа транзисторах со структурой металл-д 1электрик-полупроводник (МДП-транзисторах), построенные на динамических запоминаюгцих элементах.

Иедостатком известных динамических запомииающих элементов является то, что они не могут при храиении информации самостоятельно восстанавливать свое предыдущее состояние.

Иредлагаемый запоминающий элемент состоит из одного биполярного и двух МДПтранзисторов и отличается тем, что в нем база биполярного транзистора соединена со стоком одного МДП-транзистора, а эмиттер биноляриого и затвор другого МДП-транзистора подсоединены к источнику питания.

Благодаря этому заиомннающнй элемент обладает способностью самовосстанавливать предыдущее состояние при импульсном питании.

Запоминающий элемент имеет всего три вывода, так как импульсный режим питания благодаря временному разделению сигналов нозволяет ио одним и тем же шинам подавать нмиульсы храиения инфорл ацни, заннси, стирания и ечитьшаиия.

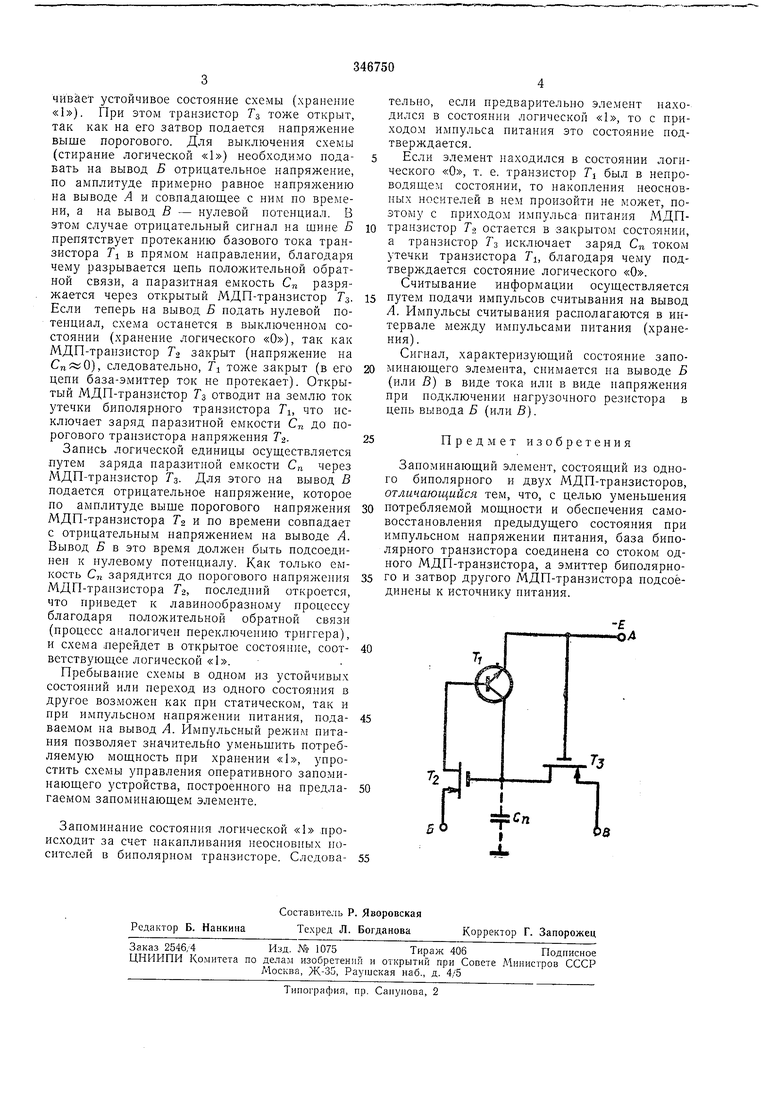

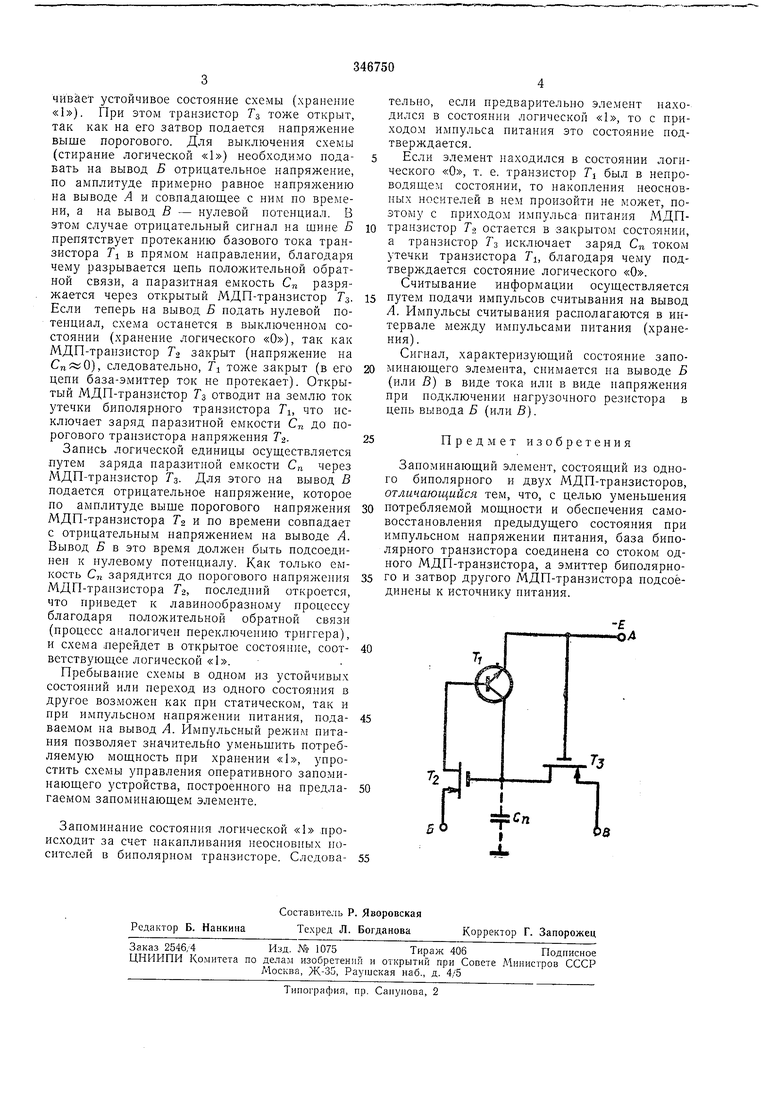

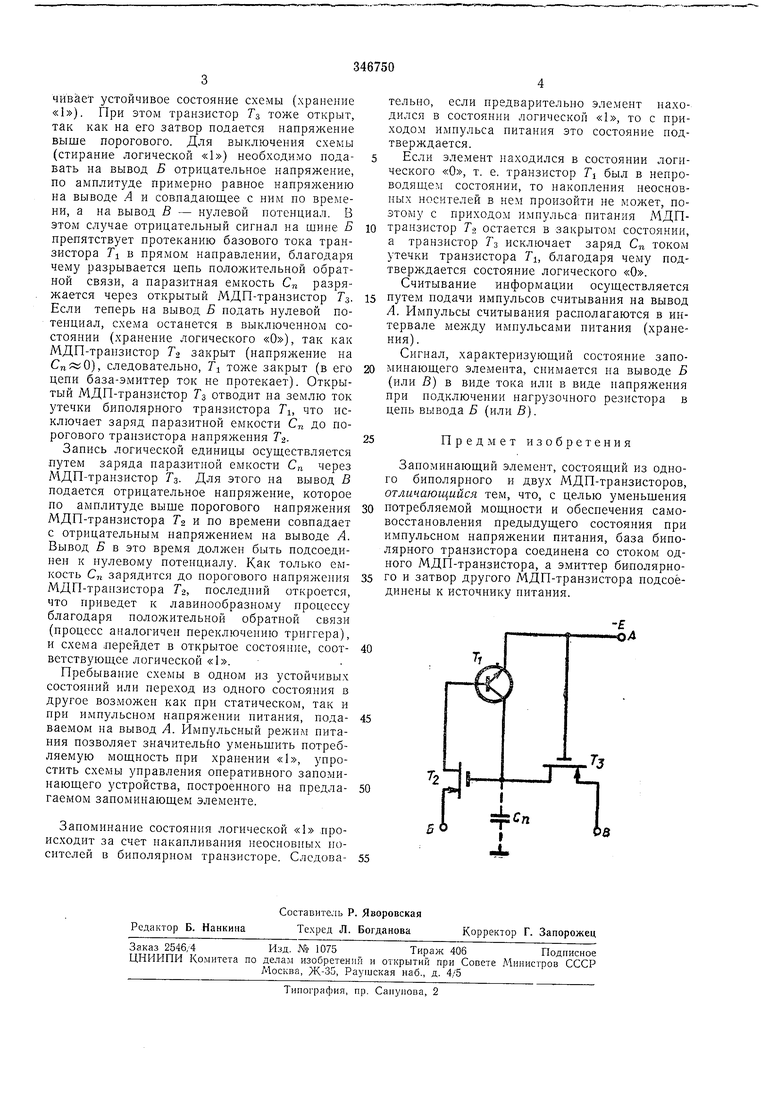

Электрическая схема запоминающего элемента нриведена на чертеже.

Она содержит одни бинолярный транзистор TI и два Л1ДП-траизистора Го и Гз. На схеме ноказаиа пуиктиром емкость С„, которая представляет собой суммарную емкость затвора МДП-транзнстора Т-2 относительно истока н подложки, если подложка заземлена, н емкость сток-истока МДП-транзистора Гз. В схеме нснользуются биполярный транзистор типа п-р-п, МДП-транзисторы - р-канальные. Па вывод А при хранении н считывании информации подаются отрицательные импульсы относнтельно выводов Б и В. На выводы Б и S

при стирании и заннеи ннформацин подаются отрицательные нмпульеы.

Принцин работы запоминающего элемента заключается в следующем.

Если паразитная емкость С„ была заряжена

предварительно до порогового напряжения МДП-транзнстора Т-2, io цоследний будет находиться в открытом состоянии, что приведет к открыванию транзнстора Т, так как в этом случае в цепи база-эмиттер транзистора TI

протекает ток. Открытое состояние транзистора TI обеепечивает иа затворе транзистора Т-2 нанряжение, почги равиое Е, которое должно быть выще норогового напряжения МДП-транзисторов, т. е. в схеме возникает ноложитель

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1974 |

|

SU491155A1 |

| Долговременный запоминающий элемент | 1978 |

|

SU680054A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| ВЫСОКОВОЛЬТНЫЙ ТРАНЗИСТОРНЫЙ КЛЮЧ | 1992 |

|

RU2006181C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| Буферный каскад | 1975 |

|

SU517085A1 |

| Импульсный стабилизатор напряжения | 1991 |

|

SU1815626A1 |

| Схема управления силовым ключом на основе БТИЗ или МДП-транзисторов | 2024 |

|

RU2825437C1 |

| Полевой транзисторный ключ | 1990 |

|

SU1734205A1 |

| Ключевое устройство | 1990 |

|

SU1721796A1 |

Даты

1972-01-01—Публикация