ним по времени, а на шину С ноложнтс.чьное напряжение +. В этом случае разность потенцналов в эмиттерно-базовой цепн транзистора 1 близка к нулю, токи эмнттера н коллектора надают, нотенциал на емкостн возрастает по мере заряда ее током полевого транзистора 3 до напряжения -{-Е на шине 6. Если напряжение на шине 4 вновь установить равным ну.тю, схема остается в выключенной (логический «О), так как МДП-транзистор 2 закрыт высоким потенциалом коллектора (напряжение на конденсаторе 7 близко к ), следовательно, транзнстор 1 тоже закрыт. Открытый МДП-транзистор 3 исключает разряд емкости током утечки биполярного транзистора.

Запись логической «I осуш;ествляется путем разряда конденсатора 7 через транзнстор 3 при подаче нулевого нотенциала на шнну 6, совпадающего но времени с отрицательным потенциалом иа шине 5 н нулевым на шине 4. Как только потенциал на конденсаторе 7 опустится ниже порога запирания МДП-транзнстора 2, последний открывается, что ириводнт к лавинообразному процессу открывання транзисторов 1 н 2 и быстрому разряду конденсатора. Прн этом схема переходит в открытое состояние, соответствующее логической «1.

Пребыванне схемы в одном из устойчивых состояний или переход из одного состояния в другое возможен как при статическом, так н нри имиульсном напряженнн питания, подаваемом на шину 5. В этом случае нанряжение на шине 5 должио изменяться от ноложительного уровня -{-2Е до отрицательного напряжения -Е. Если в схеме была записана логическая «1, то напряжение на конденсаторе было бы близко к иулю. Потенциал -i-2E на шиие 5 удерживает транзисторы 1 и 3 в запертом состоянии и не допускает заряд конденсатора 7 от нотенциала на выводе 6. С приходом импульса питания -Е на шину 5 открываются все транзисторы схемы, н она остается в открытом состоянии. Следовательно, подтверждается предварительное состояние схемы: логическая «1. Еслн в схеме записан логический «О, то напряжение на конденсаторе 7 блнзко к , транзистор 2 открыт потенциалом на шине 5, однако транзистор 1 заперт этим же потенциалом.

поэтому заряд конденсатора 7 сохраняется неизменным. Прнход отрицательного нмпульса 2Е па шнну 5 запрещает протекание тока через транзистор 2, и схема остается в закрытом состоянии. Таким образом, подтверждается предварительное состояние схемы: логический «О.

Имнульсный режим питания шины позволяет значительно умеиьшить нотребляемую

мощность при храиении логической «1.

Считывание информации осуществляется путем нодачи отрицательиых импульсов считывания -Е иа шину 5. Импульсы считывания расиолагаются в интервале между импульсами питания. Сигнал, характеризующий состояние ЗЭ, снимается па шине 4 (или 6) в внде тока или нанряжеиия при подключении нагрузочного резистора в цепь шины 4 (или 6).

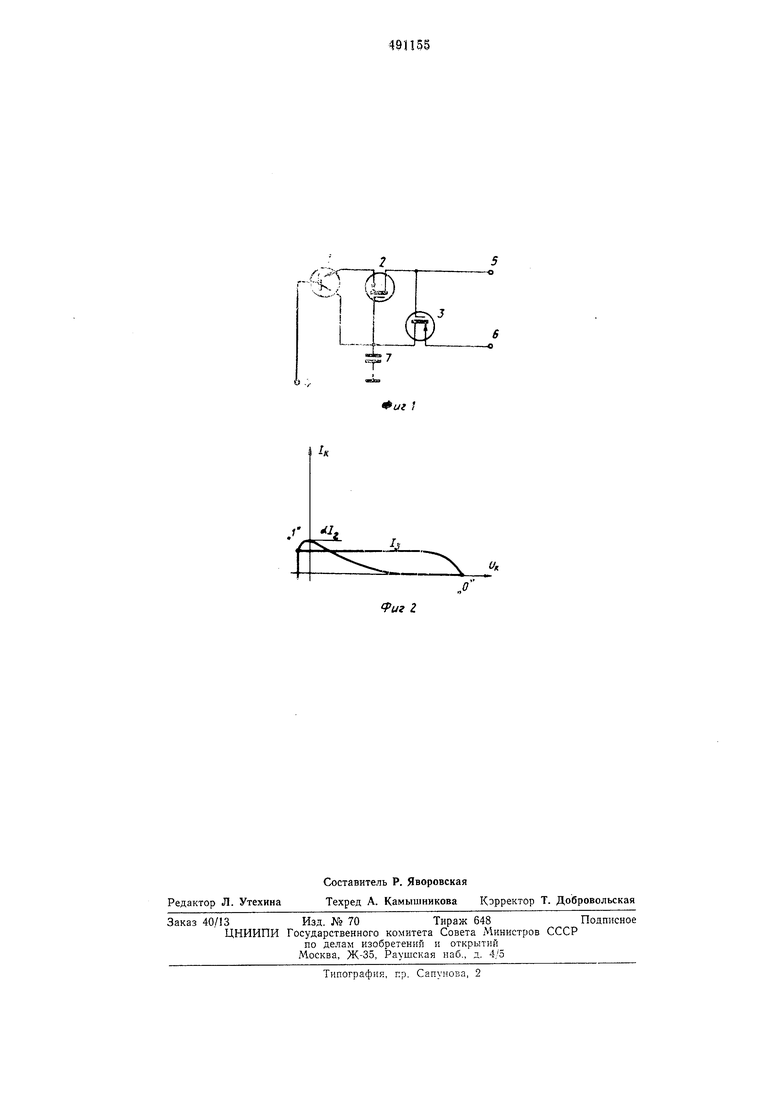

Задание тока эмиттера биполярного транзистора, (а не тока базы, как в прототипе) снижает критичность ЗЭ к разбросу коэффициеита усиления по току транзистора в схе:ие с общей базой (а). Известно, что разброс

в значеннях р, где 5 - коэффициент усиления транзистора но напряжению, во много раз превышает разброс в значеннях а. Поэтому предлагаемая схема меньше критична к разбросу нараметров элементов.

Кроме того, задание тока эмиттера позволяет значительно уменьшить глубину насыщения бниолярного транзнстора, что увеличивает быстродействие схемы.

Предмет изобретения

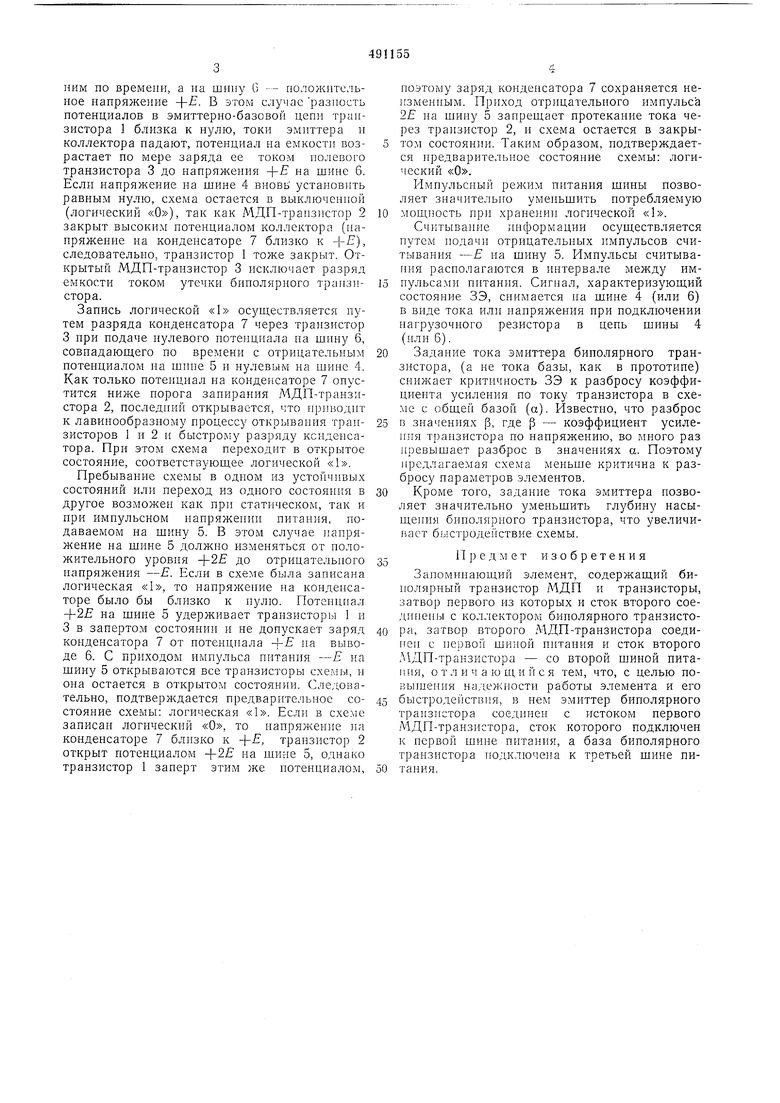

Запоминающий элемент, содержащий биполярный транзистор МДП и транзисторы, затвор нервого из которых и сток второго соединены с коллектором биполярного транзисторя, затвор второго МДИ-транзистора соединен с первой шиной питания и сток второго МДП-транзистора - со второй шиной питания, отличающийся тем, что, с целью но} ы1пення надежности работы элемента и его

быстродействия, в нем эмиттер биполярного транзистора соединен с истоком первого МДП-транзистора, сток которого подключен к первой шине питания, а база биполярного транзистора подключена к третьей шине питания,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент на мдп транзисторах | 1973 |

|

SU450230A1 |

| ЯЧЕЙКА ПАМЯТИ | 1973 |

|

SU409293A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| Импульсный стабилизатор напряжения | 2021 |

|

RU2755496C1 |

| Одновибратор | 1978 |

|

SU764105A2 |

| Инвертор | 1991 |

|

SU1817240A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1994 |

|

RU2114500C1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ | 1972 |

|

SU346750A1 |

Авторы

Даты

1975-11-05—Публикация

1974-06-04—Подача