Изобретение относится к многоканальным вычислительным устройствам со с.хемой (реализацией програММ для регистрации :и статистической обработки сигналов, .получаемых в процессе физического или биологического эксиеримеита, а также для определения формы интегральных сигналов.

Известны лгногоканальные вычислительные устройства для регистрации, статистической обработки .сиГлалоБ, а также для определения формы интегральных сигналов. При интегрировании, наряду с полезным сигиалом, неизбежно присутствуют шумы, которые также интегрируются, в результате чего сигналы становятся нестадионарными и их д}гспереия увеличивается пр.име1рно проиорциональио времени интегрирования.

В предлагаемом устройстве для у.меньшения влияния шумов на результат интегрирования сигналов типа производных спектров поглощения, а также уменьшения .погрешности вычисления некоторых параметров сигнала, иапример второго момента, а также для применения устройства и в других с 1учаях, когда сигнал имеет ветви с положительными « отрицательными зиачениями ординат и плошади под этими ветвями априорно равны, в вычислительном устройстве из,меивн порядок включения каналов. При интегрироваиии сум.мировацие чисел иачииается от иулевого канала в направлении нарастания номеров каналов, ио лишь до половины обшего количества каналов, а затем от последнего канала-в .направлении убывания номеров каналов в пределах

второй половины общего количества каналов. При таком построении вычислительного устройства дисперсия шумов нарастает сим.метрично от крыльев сигнала к его центру. При это. влия.нле шумов на результат интегрироваиия уменьшается, так как в данном случае на обоих крыльях сигнала дисперсия шумов .ми:нимальна, а ее мнксимальное значение приходится на центральную область, где сигнал также .максимален. Это, в свою очередь, приводит к уменьшению погрешностей при поатедующей обработке интегрированного сигнала. Выигрыш, получаемый за счет предлагаемого из.менения порядка .включения каналов в вычислительном устройстве, тем больше, чем

меньше отношение сигнала к шуму и че.м больше коррелированы шу.мы.

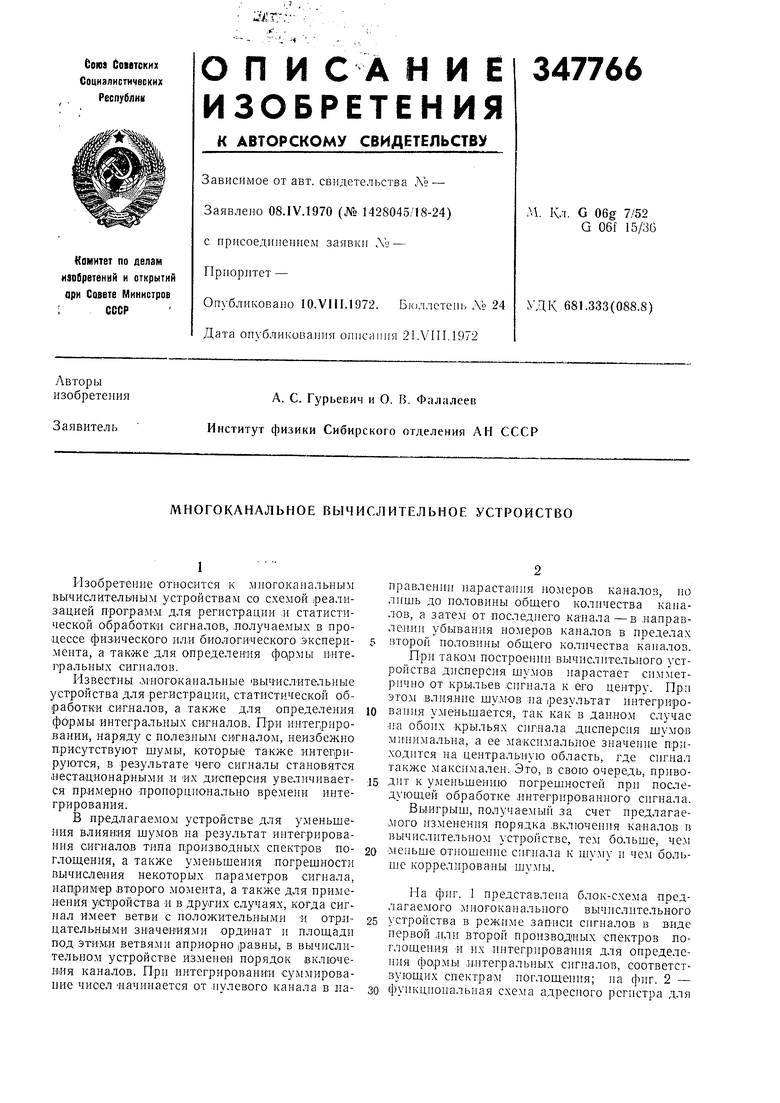

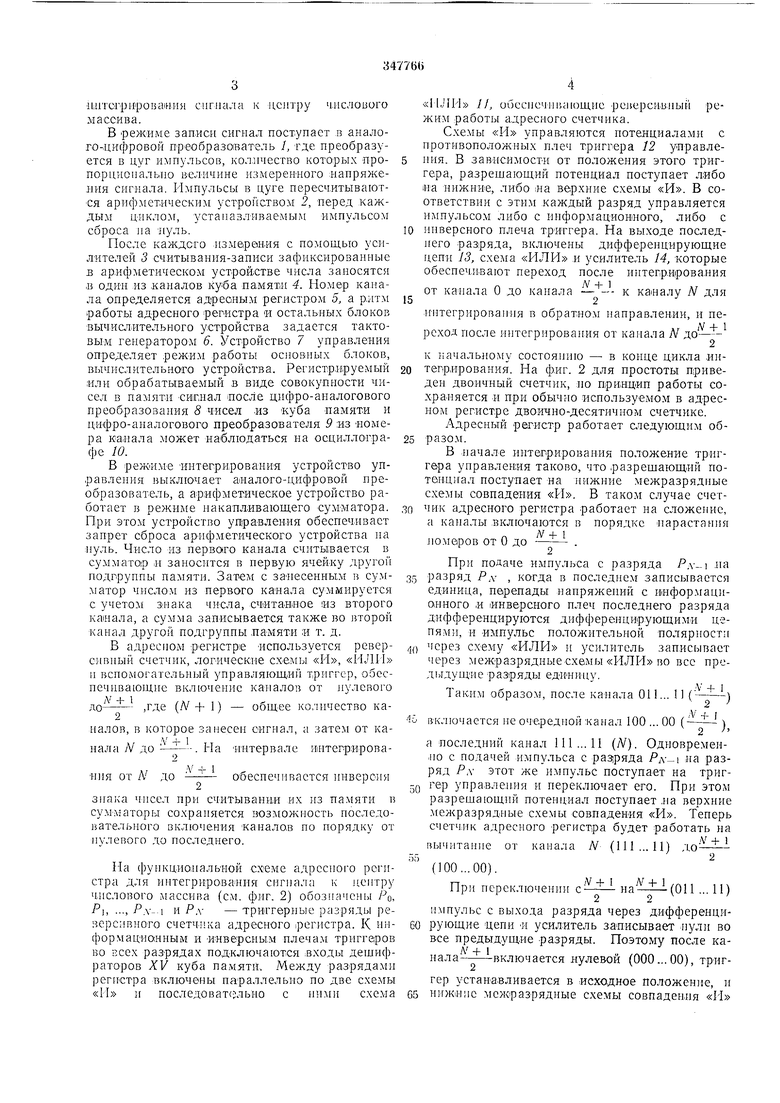

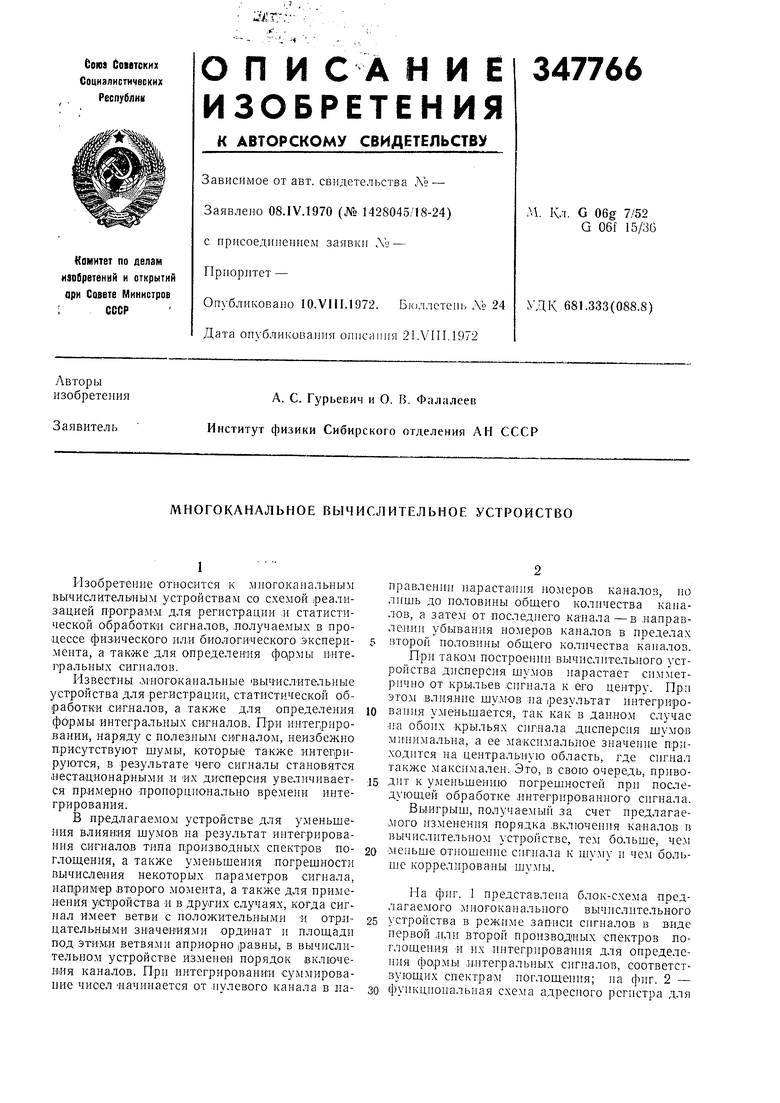

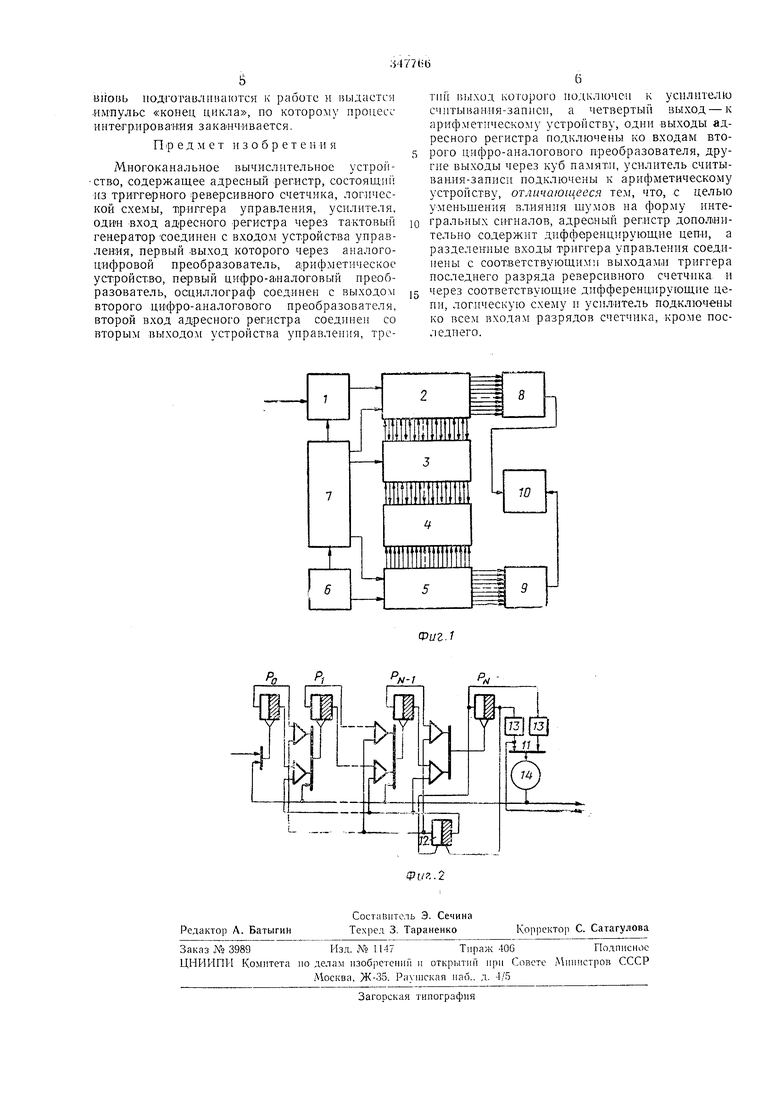

Па фиг. 1 представлена блок-схема предлагаемого .многоканального вычислительного

строиства в режиме записи сигналов в виде первой ллн второй производных -спектров поглощения и их интегрирования для определения формы интегральных сигналов, соответствующих спектрам поглощ ения; на фиг. 2 - 30 функциональная схема адресного регистра для iiiUTCi-pifpoBaiHjisi сигнала к центру Ч.НСЛОБОГО массива. В режи1ме зап.иси сигнал поступает в аналого-цифровой преобразователь /, где нреобразуетея в цуг импульсов, коллчество которых пропорниоиалыю величине измеренного :иапряжеиия сигнала. РЬшульсы в цуге пересчитывают€я арифметическим устройством 2, перед каждым цикло г, устанавливаемым импульсом сброса иа цуль. После каждого изм&реция с помощью усилителей 3 считывапия-записи зафиксированные в арифметическом устройстве числа заносятся .в один из каналов куба памяти 4. Номер канала определяется адресным регистром 5, а рлггм работы адресного регистра и остальных блоков вычислительного устройства задается тактовым генератором 6. Устройство 7 управления определяет режим работы ос1юв:иых блоков, вычислительного устройства. Регистрируемый или обрабатываемый в виде совокупности чисел в памяти сиглшл после дифро-апалогового преобразования 8 чисел из куба памяти и цифро-аналогового преобразователя 9 из номера ка.иала может наблюдаться па осциллографе 10. В режиме интегрирования устройство управлення выключает аналого-цифровой преобразователь, а арифметическое устройство работает в режиме накапливающего сумматора, При этом устройство удравления обеспечивает запрет сброса арифметического устройства иа пуль. Число из первого канала считывается в сумматор и заносится в первую ячейку другой подгруппы памяти. Затем с затюсениым в cy.vматор числом из первого каиала суммируется с учетом 3|нака числа, считавное из второго канала, а сумма записывается также во второй канал другой подгруппы памяти и т. д. В адресном регистре используется реверсивный счетчик, логические схемы «И, «ИЛ11 и вспомогательный управляющий триггер, обеспечивающие включение каналов от нулевого ,где (/V -Ь 1) - общее количество каналов, в которое занесен сигнал, а затем от каиала yV до ----. Па интервале интегрированпя от Л до обеспечивается инверсия знака чисел при считывании их из памяти п сумматоры сохраняется возможность последовательного включения каналов по порядку от пулевого до последнего. На (1)ункциональной схеме адресного регистра для интегрирования сигнала к центру числового массива (см. фиг. 2) обозначены РО, PI, ..., Р.-- и P.V - триггерные разряды реверсивного счетчика адресного регистра. К информационным и инверсным плеча.м триггеров во нсех разрядах подключаются ;входы дещифраторо.в XV куба памяти. Между разрядами регистра включены параллельно по две схе.мы «И и последоват ;льио с ними схема « IJIlI //, обеспечн1;а1ощие реверсивный режим работы адресного счетчика. Схемы «И управляются потенциалами с противоположных плеч триггера 12 управлеиия. В зависимости от положения этого триггера, разрещающий потепциал поступает либо 1па нижние, либо :на верхние схемы «И. В соответствии с этим каждый разряд управляется импульсо.м либо с информационного, либо с инверсного плеча триггера. На выходе последнего разряда, включены дифференцирующие цепи J3, схема «НЛИ и усилитель 14, которые обеспеч-и.вают переход после интегрирования от канала О до каналак каналу N для интегрирования в обратном направлении, и переход после интегрирования от канала N до к начальному состоянию - в конце цикла интегрирования. На фнг. 2 для простоты приведен двоичный счетчик, но принцип работы сохраняется и при обычно используемом в адресном регистре двоично-десятичиом счетчике. Адресный регистр работает следующим образом. В начале интегрирования положение трнггера унравления таково, что разрещающий потенциал поступает на нижние межразрядпые схемы совпадеиия «И. В таком случае счетчнк адресного регистра работает на сложение, а каналы .включаются в порядке парастання номеров от О до . При подаче импульса с разряда P.v-i на разряд РЛ- , когда в последнем записывается единица, перепады напряжепий с пифор.мациопного и инверсного плеч последнего разряда дифференцируются дифференцирующими цепями, и импульс положительной поляр1гости через схему «ИЛИ и усилитель записывает через межразрядные схемы «ИЛИ во все предыдущие разряды единицу. Таким образом, после канала 011... 11 {--- включается не очередной канал 100 ... 00 ( ) а последний канал 111... И (/V). Одновременно с подачей импульса с разряда PA-I на разряд Р. этот же импульс поступает на триггер управлення и переключает его. При этом разрещающнй потенциал поступает иа верхние межразрядные схемы еовпадения «И. Теперь счетчик адресного регистра будет работать па вычитание от канала N- (111... 11) до (100 ...00). „аЛ1±1(011...11) При переключенни с 22 импульс с выхода разряда через дифференцирующие цепи И усилитель заиисывает нули во все предыдущие разряды. Поэтому после каВНОВЬ 11одгогаи„и иак)тся к работе и ныдастся имПульс «конец цикла, по которому процесс интегр.ированяя зака ч-иваетея.

Предмет изобретен и я

М,ногоканальное вычислительное устройство, содержащее адресный регистр, состоящий из трИГгерного реверсивного счетчика, логической схемы, Т1риггера управления, усилителя, один вход адресного регистра через тактовый генератор соединен с входом устройства управления, первый .выход которого через аналогоцифровой преобразователь, а;рифметическое устройство, первый цифро-а/налоговый преобразователь, осциллограф соединен с выходом второго цифро-а.иалогового преобразователя, второй вход адресного регистра соединен со вторьп выходом устройства управления, третин 15ы.од которого иодключеи к усилителю считывания-записи, а четвертый выход - к арифметическому устройству, одни выходы адресного регистра подключены ко входам второго цифро-аналогового преобразователя, другие выходы через куб памяти, усилитель считыванля-записи подключены к арифметическому устройству, отличающееся тем, что, с целью уменьщения влияния щумов на форму интегральных сигналов, адресный регистр дополнительно содержит диффереицирующие цеш, а разделенные входы триггера управления соединены с соответствующими выхода ьи триггера последнего разряда реверсивного счетчика и через соответствующие дифференцирующие цепи, логическую схему и усилитель подключены ко всем входам разрядов счетчика, кроме последнего.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

Даты

1972-01-01—Публикация