Изобретение относится к системам связи и может быть использовано в аппаратуре асинхронной передачи двоичной информации.

Известно устройство асинхронного ввода двоичной информации в цифровой тракт методом двустороннего стаффинга, содержащее блок памяти, фазовый компаратор и блок формирования команд. В таких устройствах от числа символов в кодовой комбинации, составляющей команду, зависит достоверность приема команд, которая определяется числом допустимых сбоев посылок, составляющих команду, не приводящим к нарущению правильности приема этой команды на приемной станции. Увеличение числа команд ведет к уменьщению числа посылок, которыми различаются команды, поэтому для сохранения той же достоверности необходимо увеличить число посылок в команде символов кодовой комбинации.

Целью изобретения является уменьщение общего числа команд и повыщение достоверности передаваемых сообщений. Это достигается тем, что блок формирования команд содержит узел периодического переключения команд, например счетный триггер, один выход которого подключен ко входу формирователя команды «+, а другой - ко входу формирователя команды «-. При этом к одному входу узла периодического переключения команд

подключен выход фазового компаратора, а на другой вход узла периодического переключения команд подается импульсная последовательность с частотой следования команд.

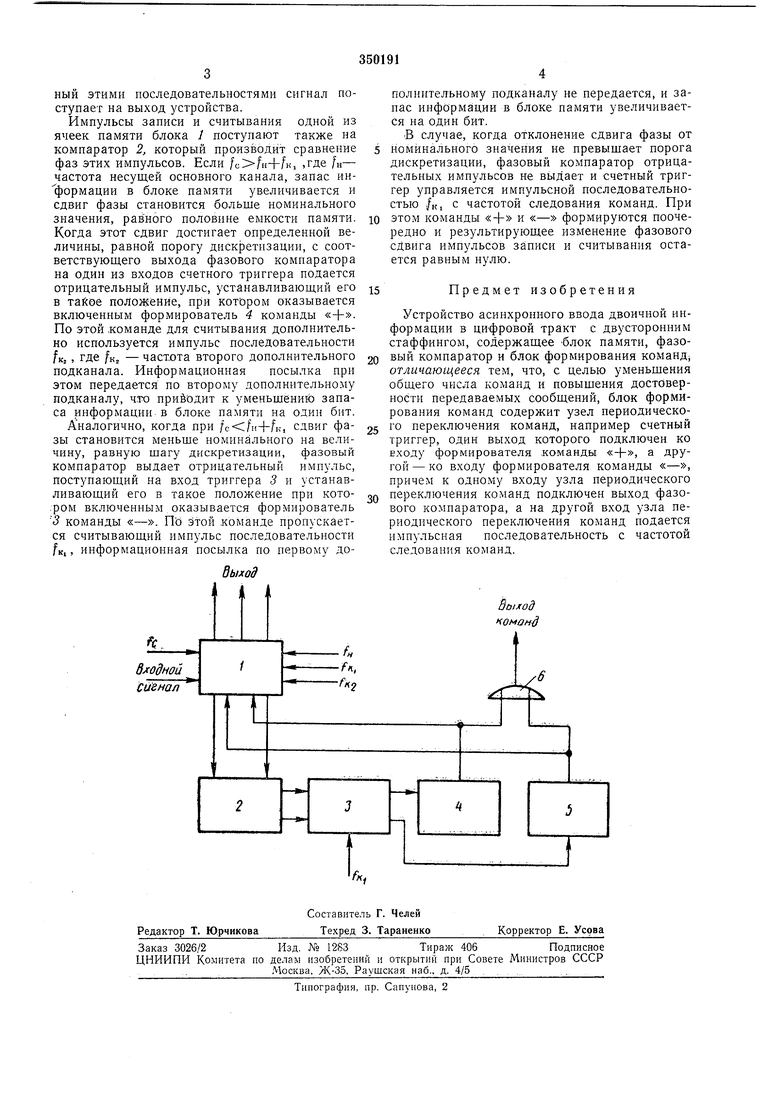

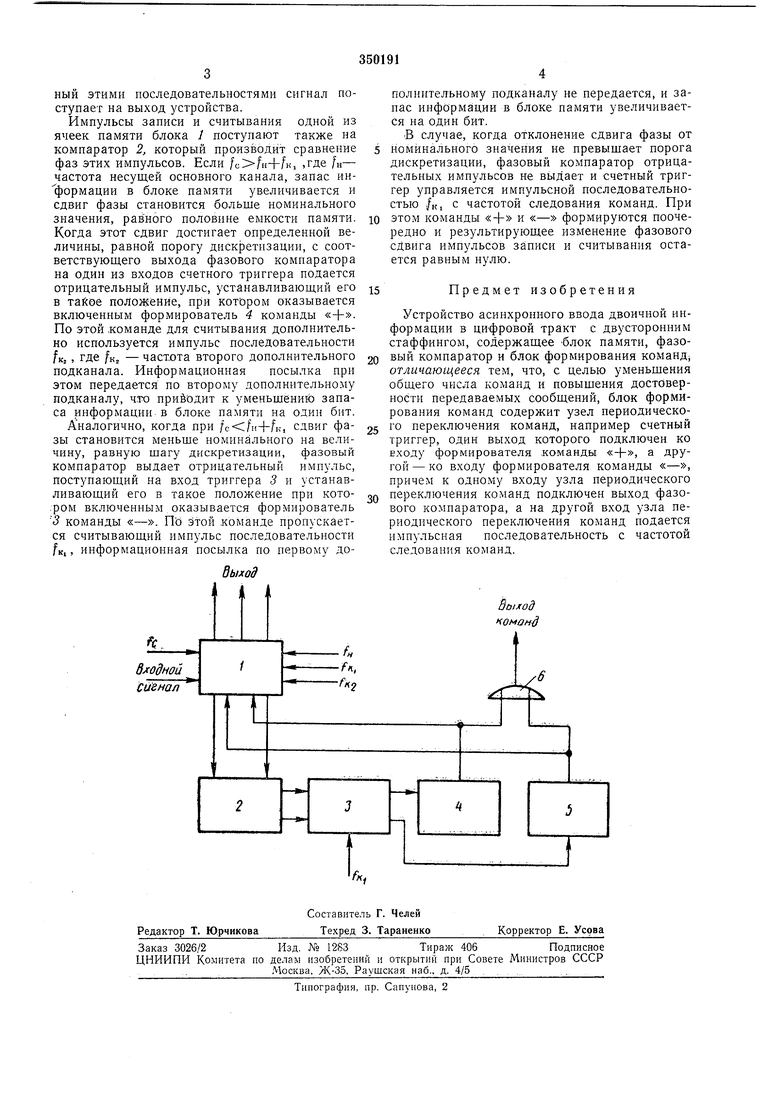

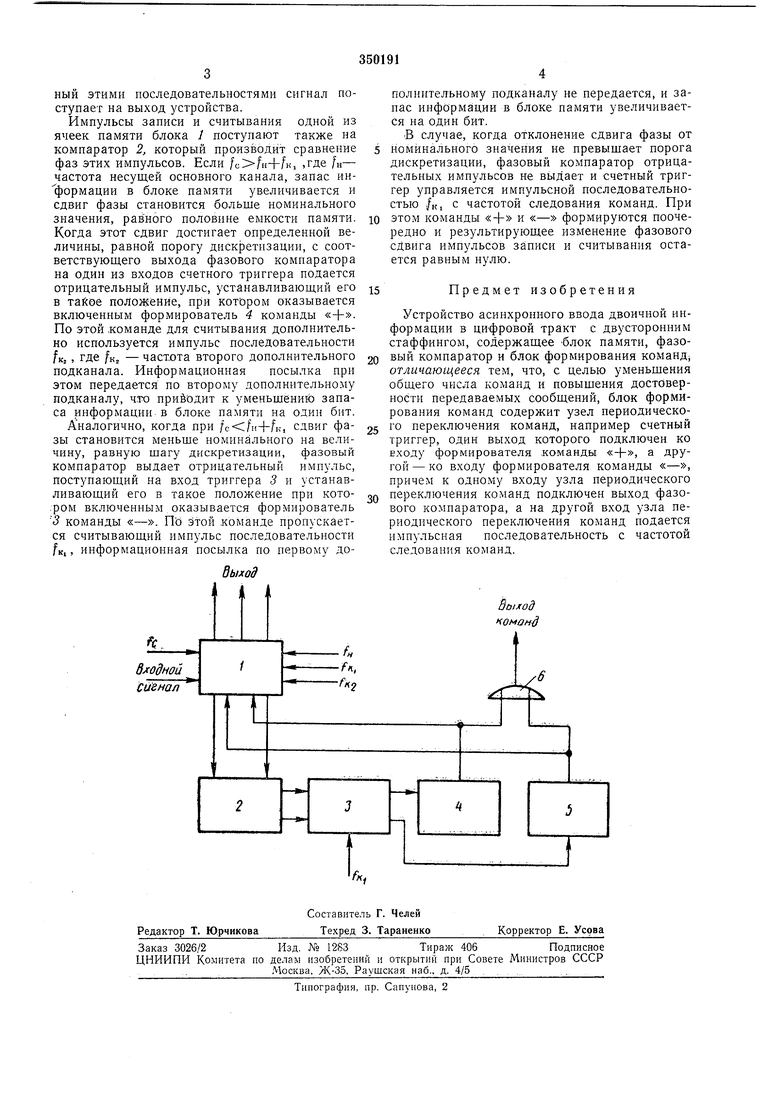

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит блок 1 памяти, фазовый компаратор 2; блок формирования команд, состоящий из узла 3 периодического

переключения команд, формирователя 4 команды «-f и формирователя 5 команды и схему «ИЛИ 6. В качестве узла периодического переключения команд может использоваться, например, счетный триггер, один

выход которого подключен ко входу формирователя 4, а другой - ко входу формирователя 5. К одному входу узла периодического переключения команд подключен вы.ход фазового компаратора, а на другой его вход подается импульсная последовательность с частотой следования команд f KI

Поступающий на вход устройства линейный сигнал записывается в блоке /, причем тактовая частота /с сигнала используется для формирования импульсов записи. На распределитель считывания блока / подаются три импульсные последовательности, соответствующие временным позициям основного и двух доиолнительных подканалов, отводимым для

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЧАСТОТНЫХ ПОСЫЛОК | 1973 |

|

SU408323A1 |

| Устройство асинхронного ввода двоичных сигналов в цифровой тракт систем связи с двухсторонними временными сдвигами | 1973 |

|

SU472468A1 |

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| ВСЕСОЮаНАЯ i | 1973 |

|

SU372717A1 |

| Передатчик интервально-кодовых сигналов | 1982 |

|

SU1061283A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ЧАСТОТНЫХ ПОСЫЛОК | 1973 |

|

SU407323A1 |

| Логический коммутатор | 1977 |

|

SU652553A1 |

| Устройство для асинхронного сопряжения в синхронном канале связи | 1972 |

|

SU454702A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

Даты

1972-01-01—Публикация