Изобретение относится к измерительным автоматическим устройствам вычислительной техники и предназначено для автоматической проверки в динамическом режиме и с заданным быстродействием блоков долговременных (постоянных) запоминающих устройств, выполненных на ферритовых элементах.

В известных устройствах для проверки постоянных запоминающих устройств, содержащих генератор, схемы останова, линии задержки, счетчик, схемы сравнения числа, схемы сравнения адреса, ячейки «НЕ-ИЛИ, триггер останова, отсутствует автоматизация проверок: так, например, установка эталонного числа, а также адреса в соответствующих схемах сравнения производятся вручную - тумблерами. Вследствие ручной установки эталонного числа и адреса нроизводительность стенда и качество проверки низкие. Кроме этого, стенд не обеспечивает проверки запоминающих устройств по заданным значениям амплитуд сигнала и помехи.

Цель изобретения - автоматизация проверки, сокращение времени и повышение качества проверки запоминающих устройств.

Это достигается тем, что в устройство введены фотосчитывающий механизм, соединенный с регистром адресов и блоками управления и сравнения, блоки временной селекции и анализа амплитуд и генераторы стробов

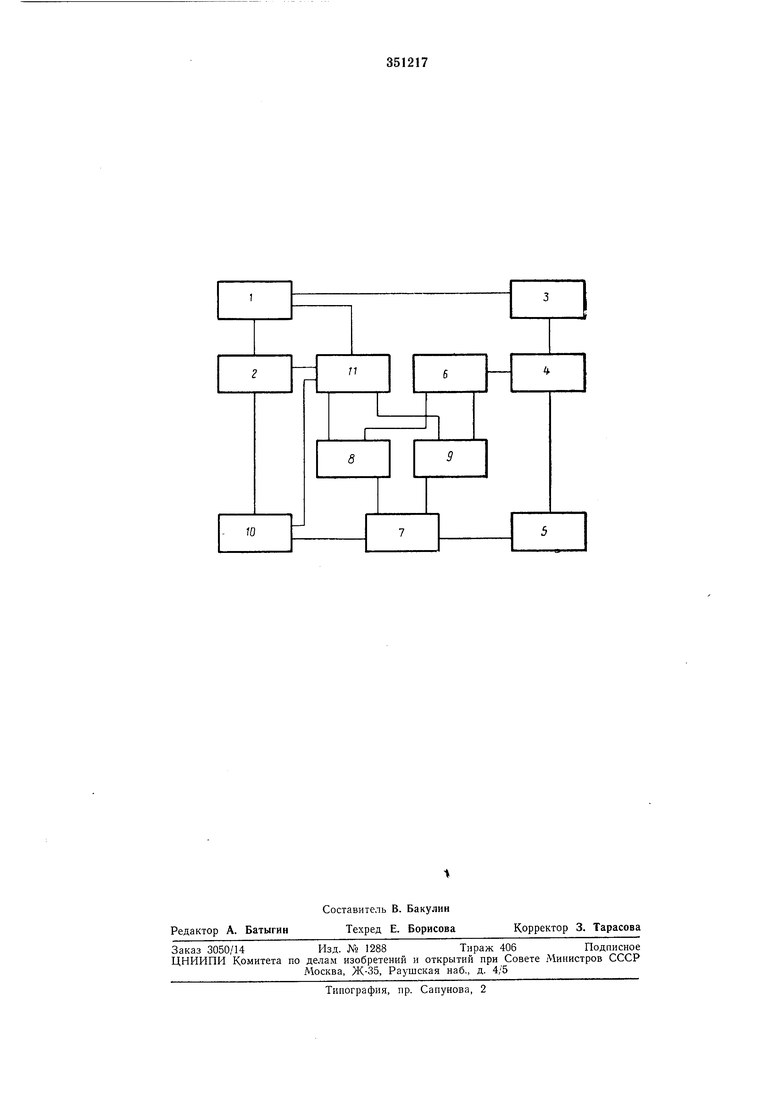

сигнала и помехи, причем блок анализа амплитуд соединен с блоками временной селекции, сравнения и управления, а блок управления соединен с генераторами стробов сигнала и помехи, которые подключены к генератору тактовых импульсов и блоку временной селекции, при этом блок временной селекции соединен с проверяемым блоком. Устройство автоматической проверки ферритовых блоков долговременной памяти работает по принципу сравнения программы, получаемой от проверяемых блоков, с эталонной программой, вводимой в устройство. На чертеже представлена блок-схема предлагаемого устройства.

Эталонную программу, а также закодированный адрес, нанесенные на перфоленту, с помощью фотосчитывающего механизма (ФСМ) 1 вводят соответственно в блок 2

сравнения и регистр 3 адреса.

Регистр 3 адреса соединен с дешифратором 4. С выхода последнего управляющие уровни поступают на входы проверяемого блока 5

и устанавливают адрес проверяемой информации. Носле установки проверки с генератора 6 тактовых импульсов через дещифратор иоступают импульсы опроса ферритовых схем блока памяти, на выходах которого появляетпого кода, программа которой соответствует установленному адресу.

Программа постунает на соответству1ош,ие входы блока 7 временной селекции. На другие входы блока 7 с генераторов 8 стробов сигнала н помехн 9 подаются импульсы. Импульсы сигнала и помехи с блока 7 временной селекции поступают на блок W анализа амплитуды, а с него - на блок 2 сравнения. Блок 10 анализа соединен с блоком 11 управления. На блок 7 временной селекции, кроме сигналов информации проверяемого блока, подаются импульсы с генераторов 8 стробов сигнала и помехи 9, на которые с генераторов 6 тактовых импульсов и блока // управления подаются импульсы. Блок 11 управления соединен с ФСМ / и блоком 2 сравнения.

Работа устройства начинается с ввода перфоленты в фотосчитывающий механизм. На перфоленте закодированы слулсебные команды: для обеспечения старт-стопного режима работы ФСМ 1 а также коды адресов проверяемого ферриточого блока памяти и эталонных программ.. Код адреса с ФСМ 1 поступает в регистр; 5 адреса, который соединен с дешифратором 4. С выхода последнего управляющие сигналы поступают на входы проверяемого блока 5 и устанавливают адрес проверяемой информации. После установки адреса с генератора 6 тактовых импульсов через дешифратор 4 поступают импульсы опроса ферритовых схем памяти блока. На входах последнего появляется информация в виде параллельного кода, программа которой соответствует установленному адресу. Информация постунает на соответствующие входы блока 7 временной селекции. На другие входы блока 7 с генераторов стробов сигнала и номехи поступают стробирующие импульсы. Временная селекция этих сигналов позволяет разделить полезный сигнал и помеху для последующего анализа их амплитуды и детализации характера неисправности проверяемого блока.

Имнульсы с выходов блока 7 временной селекции подаются на входы блока 10 анализа амнлитуд. На другие входы блока 10 подаются сигналы с блока 11 управления, обеспечивающие последовательный, в два этана, анаЛИЗ значений амплитуд сигналов.

На первом этапе анализируется величина амплитуды полезного сигнала по отнощению к заданным значениям, на втором этапе - величина амплитуды сигнала номехи. Если значения амплитуд полезного сигнала или сигнала номехи не вышли из заданного предела, блок 10 анализа амнлитуд выдает соответствующую программу на блок 2 сравнения. На другие входы блока 2 от ФСМ / поступает эталонная программа.

Если обе программы совпадают друг с другом, с блока 2 сравнения подается разрешающий сигнал на блок 11 управления, который, в свою очередь, выдает сигнал пуска на ФСМ /. Нри продвижении перфоленты считывается код следующего адреса и эталонная программа, соответствующая этому адресу.

После заверщения считывания эталонной программы блок 11 управления выдает сигнал остановки ФСМ 1, движение перфоленты прекращается и с блока управления подаются управляющие сигналы на генераторы стробов, блок анализа амплитуды и т. д.

Если при проверке испытуемого блока 5 программа, поступающая с него через блоки временной селекции и анализа амплитуды на блок сравнения, не совпадает с эталонной программой или значения амплитуды полезного сигнала (сигнала помехи) вышли из заданного нредела, с блока 2 сравнения поступает сигнал ощибки на блок // управления. При этом происходит детализация характера ощибки: но сигналу или по номехе, т. е. полезный сигнал ниже заданного нредела, сигнал помехи выше заданного предела. В этом случае блок // управления не выдает сигнал нуска ФСМ 1. Индикаторные устройства регистра адреса указывают адрес ошибки, индикаторные устройства блока сравнения указывают помер выхода блока, на котором информация не совпадает с эталонной, индикаторные устройства блока анализа амплитуд указывают характер ошибки: по полезному сигналу или сигналу помехи.

В этом случае фиксируются адрес и номер выхода проверяемого блока, после чего проверка блока продолжается.

Предмет изобретения

Устройство для проверки запоминающих устройств, содержащее блок управления, соединенный с блоком сравнения, регистр адреса, соединенный через дещифратор с проверяемым блоком и генератор тактовых импульсов, подключенный к дещифратору, отличающееся тем, что, с целью увеличения быстродействия и улучшения качества проверки, в него введены фотосчитывающий механизм, соединенный с регистром адреса и блоками унравления и сравнения, блоки временной селекции и анализа амнлитуд, и генераторы стробов сигнала и помехи, причем блок анализа амнлитуд соединен с блоками временной селекции, сравнения и унравления, а блок унравления соединен с генераторами стробов сигнала и помехи, которые подключены к генератору тактовых импульсов и блоку временной селекции, при этом блок временной селекции соединен с проверяемым блоком.

Авторы

Даты

1972-01-01—Публикация