1

Изобретение относится к разделу вычислительной техники - устройствам математического моделирования.

Известны устройства сложения, умножения, вычитания, функционального преобразования аналоговых сигналов, в которых для представления информации используются непрерывные электрические сигналы постоянного тока. Область примеиения таких устройств ограничена невысокой точностью вычислений.

Целью изобретения является повышение точности работы устройства при выполнении математических операций с аналоговыми сигналами, соизмеримой с точностью цифрового способа вычислений.

Поставленная цель достигается тем, что устройство содержит п структурно одинаковых вычислительных блоков, моделирующих математические операции.

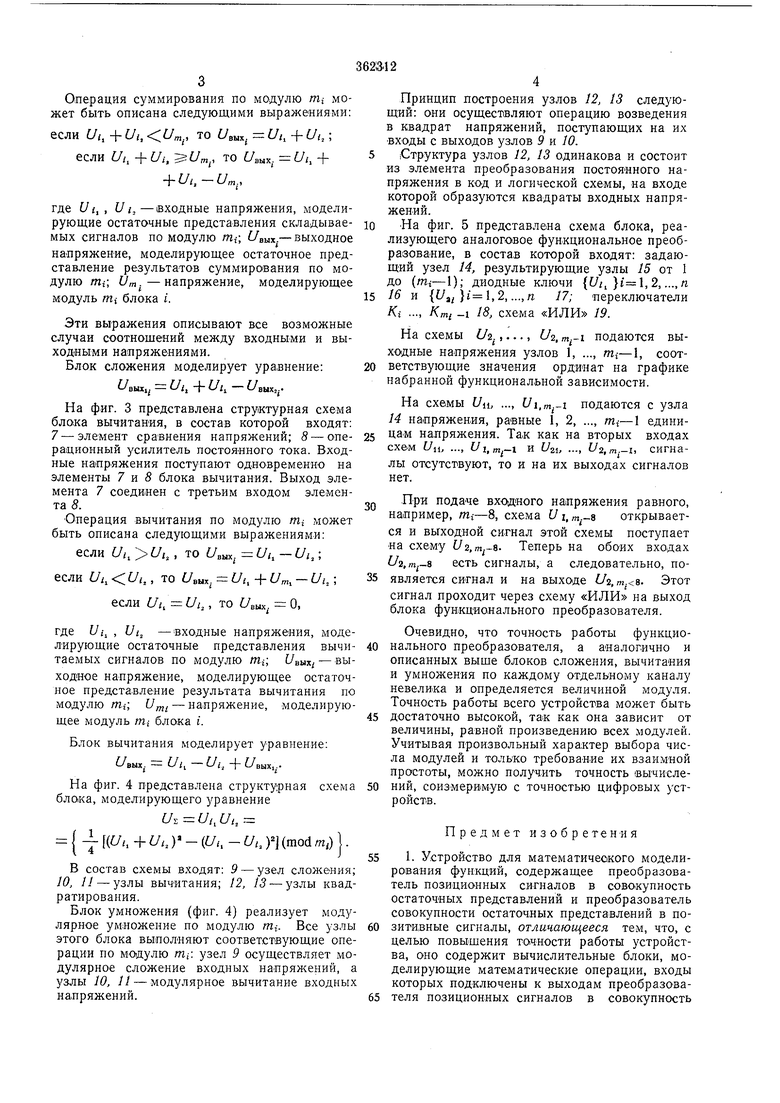

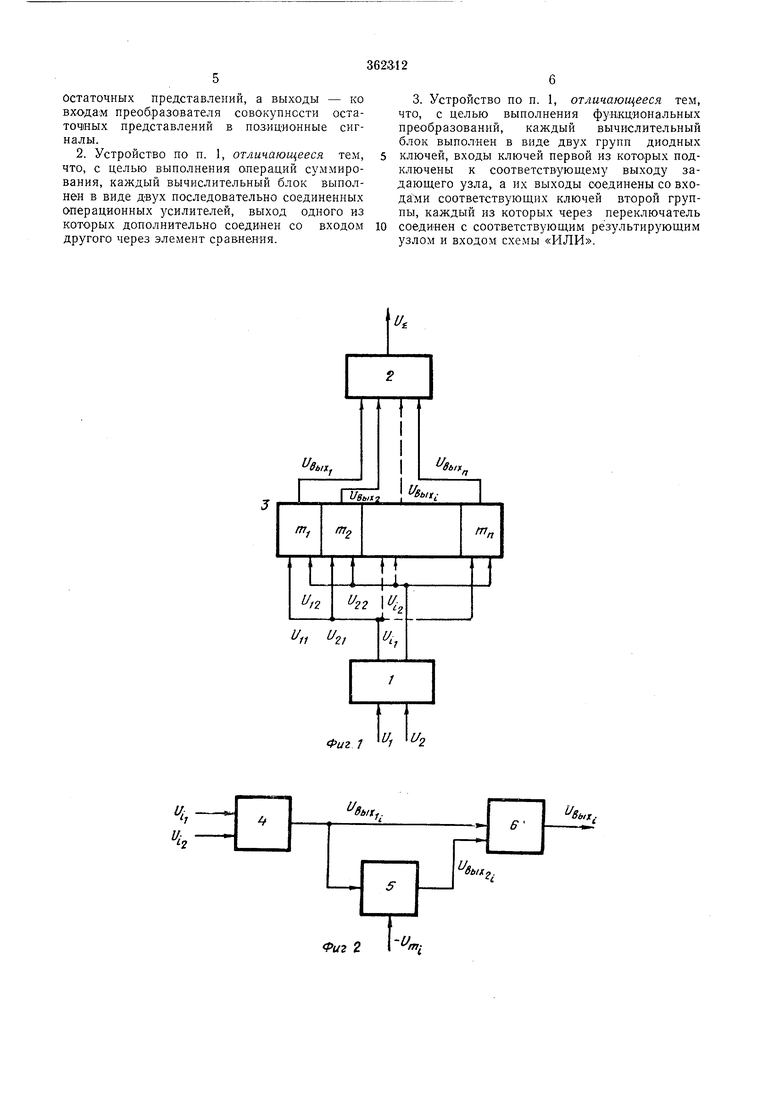

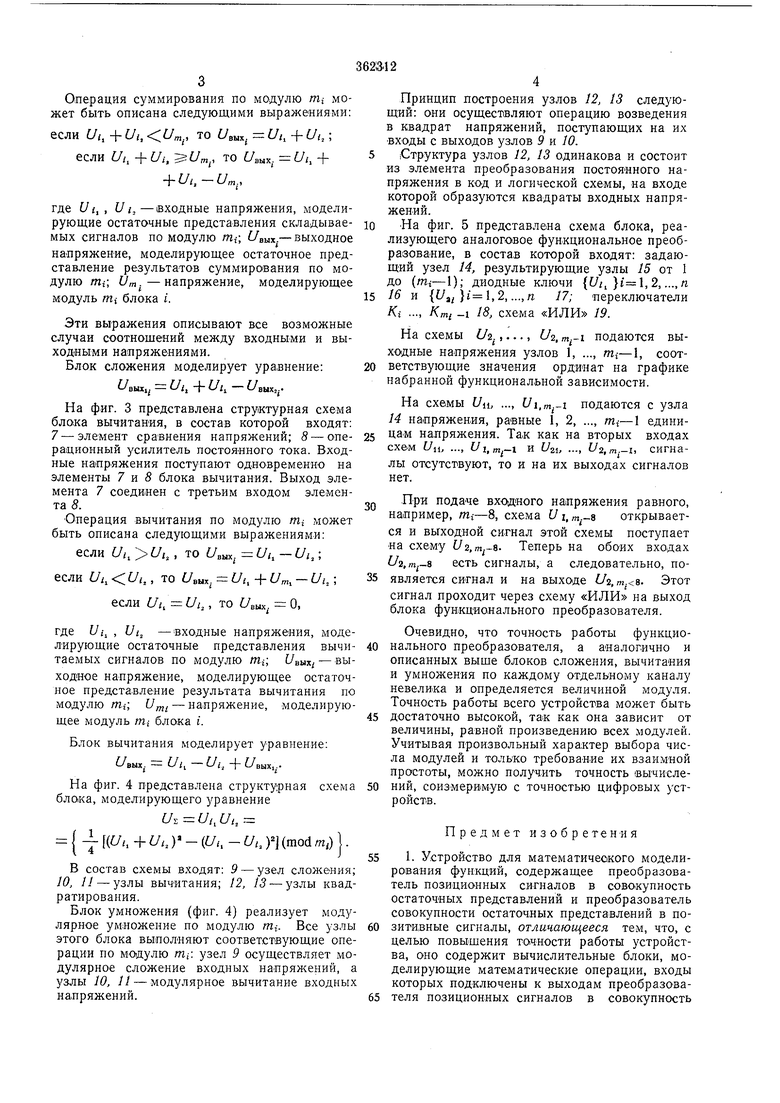

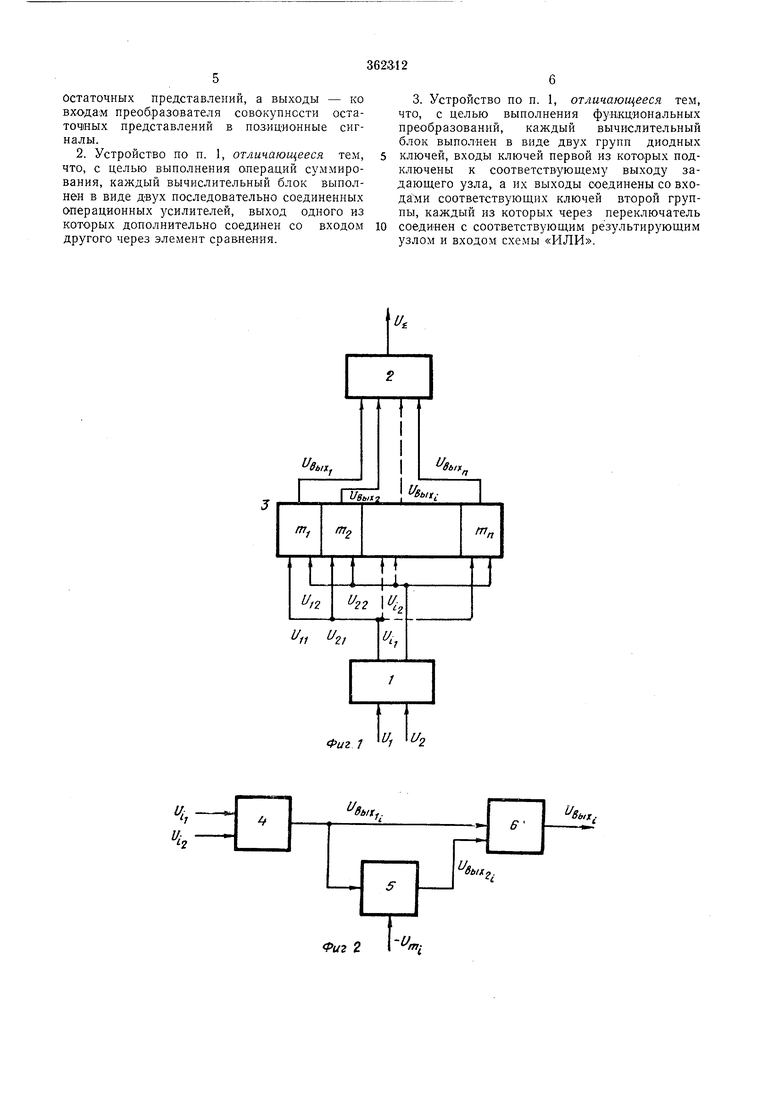

На фиг. 1 представлена принципиальная структурная схема устройства; на фиг. 2-5 частные случаи, реализующие соответственно операции сложения, вычитания, умножения и функционального преобразования.

На схеме (фиг. 1) представлены: / - входной преобразователь позиционных сигналов t/i и t/a в совокупности остаточных представлений {Ui, } ,2,...,n и (Ui, } ,2,..., п по модулям {гПг} ,2, ..., п; 2 - выходной преобразователь совокупности остаточных представлении на выходе схемы . в . позиционное представление t/i .

Устройство содержит также п блоков 5, обозначенных на фиг. 1 ть т, ..., т„. Число

блоков п равно числу модулей {т,-}1 1,2,..., л в системе остаточных классов. Количество модулей и их величина выбираются из соображений обеспечения необходимой точности вычислений. Определяющий возможную точность вычислений числовой диапазон, внутри которого вынолняется вычислительная операция, равен произведению модулей. Принцип работы всех блоков одинаков. На фиг. 2 представлена структурная схема

блока сложения, в состав которой входят: 4 - операционный усилитель постоянного тока (УПТ); 5 - элемент сравнения напряжений; 6 - дополнительный операционный усилитель. Выход УПТ 4 связан со входами элемента

сравнения и дополнительного УПТ, а выход элемента сравнения соединен со вторым входом дополнительного УПТ. В элементе сравнения осуществляется сравнение /вых,( с и,п. .

Входные и выходной сигналы каждого блока представляют собой электрические напряжения постоянного тока, которые могут принимать дискретные значения из целочисленного ряда, за:ключенного в пределах от О до

(Шг-1). Операция суммирования по модулю т; может быть описана следующими выражениями: если Ui, + Ui, Ут., то б/вых. Ui, + Ut,; если Ut + Ui, 5:f/m,, то f/вых,. Ui,+ ., где и i , и I,-входные напряжения, моделирующие остаточные представления складываемых сигналов по модулю тс, f/вых -выходное напряжение, моделирующее остаточное представление результатов суммирования по модулю /Иг-; Urn. - напряжение, моделирующее модуль nii блОКа /. Эти выражения описывают все возможные случаи соотнощений между входными и выходными напряжениями. Блок сложения моделирует уравнение: U,, Ui,,-U,.. На фиг. 3 представлена структурная схема блока вычитания, в состав которой входят: 7 - элемент сравнения напряжений; 8 - oneрационный усилитель постоянного тока. Входные напряжения поступают одновременно на элементы 7 и 8 блока вычитания. Выход элемента 7 соединен с третьим входом элемента 8. Операция вычитания по модулю /п может быть описана следующими выражениями: если Ui, Ui, то беых. Ui,-Ui,; если UL, Ui,, то t/вых, U(, + и т, - Ui,; если Ui, Ui, то бвых. О, где t/(, , Ut., -входные напряжения, моделирующие остаточные представления вычитаемых сигналов по модулю (Увых - выходное напряжение, моделирующее остаточ ное представление результата вычитания по модулю т,; - напряжение, моделирую щее модуль /П; блока г. Блок вычитания моделирует уравнение: вых; Ui - Ui + .на фиг. 4 представлена структурная схема блока, моделирующего уравнение U,Ut,Ui, (/. + Ui, У - (Ui, - Ui, Y (mod m,) В состав схемы входят: 9 - узел сложения 10, 11 - узлы вычитания; 12, 13--узлы квад ратирования. Блок умножения (фиг. 4) реализует моду лярное умножение по модулю т,. Все узлы этого блока выполняют соответствующие опе рации по модулю /П;: узел 9 осуществляет мо дулярное сложение входных напряжений, узлы 10, 11-модулярное вычитание входных напряжений. Принцип построения узлов 12, 13 следуюий: они осуществляют операцию возведения квадрат напряжений, поступающих на их ходы с выходов узлов 9 и 10. Структура узлов 12, 13 одинакова и состоит з элемента преобразования постоя«ного напряжения в код и логической схемы, на входе которой образуются квадраты входных напряжений. На фиг. 5 представлена схема блока, реализующего аналоговое функциональное преобразование, в состав которой входят: задающий узел 14, результирующие узлы 15 от 1 до (mi-I); диодные ключи (Ut ,2, ...,п 16 и {t/a ,2, ...,п 17; переключатели Кг ..., Kmi -I 18, схема «ИЛИ 19. На схемы Uz.,..., Uz,m-i подаются выходные напряжения узлов 1, ..., т,- 1, соответствующие значения ординат на графике набранной функциональной зависимости. На схемы t/ib ..., Ui,m.-i подаются с узла 14 напряжения, равные 1, 2, ..., единицам напряжения. Так как на вторых входах схем t/ib ..., U, и Uzi, ..., U.m.-i, сигналы отсутствуют, то и на их выходах сигналов нет. При подаче входного напряжения равного, например, OTJ-8, схема U i, „,.8 открывается и выходной сигнал этой схемы поступает «а схему t/2, ш.-в- Теперь на обоих входах и. есть сигналы, а следовательно, появляется сигнал и на выходе Uz,m.s. Этот сигнал проходит через схему «ИЛИ на выход блока функционального преобразователя. Очевидно, что точность работы функционального преобразователя, а аналогично и описанных выше блоков сложения, вычитания и умножения по каждому отдельному каналу невелика и определяется величиной модуля. Точность работы всего устройства может быть достаточно высокой, так как она зависит от величины, равной произведению всех модулей. Учитывая произвольный характер выбора числа модулей и только требование их взаимной простоты, можно получить точность вычислений, соиЗМерИ1мую с точностью цифровых устПредмет изобретения 1. Устройство для математического моделирования функций, содержащее преобразователь позиционных сигналов в совокупность остаточных представлений и преобразователь совокупности остаточных представлений в позитивные сигналы, отличающееся тем, что, с целью повыщения точности работы устройства, оно содержит вычислительные блоки, моделирующие математические операции, входы которых подключены к выходам преобразователя позиционных сигналов в совокупность

остаточных представлений, а выходы - ко входам преобразователя совокупности остаточных представлений в поанционные сигналы.

2. Устройство по п. 1, отличающееся тем, что, с целью выполнения операций суммирования, каждый вычислительный блок выполнен в виде двух последовательно соединенных операционных усилителей, выход одного из которых дополнительно соединен со входом другого через элемент сравнения.

3. Устройство по п. 1, отличающееся тем, что, с целью выполнения функциональных преобразований, каждый вычислительный блок выполнен в виде двух групп диодных ключей, входы ключей первой из которых подключены к соответствующему выходу задающего узла, а их выходы соединены со входами соответствующих ключей второй группы, каждый из которых через переключатель соединен с соответствующим результирующим узлом и входом схемы «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ СИГНАЛОВ | 1973 |

|

SU405114A1 |

| Устройство для определения остаточных напряжений при непрерывном травлении образца | 1973 |

|

SU567088A1 |

| Преобразователь перемещение-код | 1974 |

|

SU510732A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU374612A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Устройство для определения коэффициентов разложения корреляционной функции по системе ортонормированных базисных функций | 1985 |

|

SU1287196A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| Устройство для моделирования многолучевого радиоканала | 1974 |

|

SU516029A1 |

| Устройство для суммирования частотных импульсных последовательностей | 1979 |

|

SU1163332A1 |

| Арифметическое устройство в системе остаточных классов | 1985 |

|

SU1290315A1 |

Л

ых.

/77,

ГПп

и.

12

г/„ и,

Фиг Щ

; %

Фиг 2

1/А

I %/...

ивь,

т„

ТТ

К,

-и„.

т;

Авторы

Даты

1973-01-01—Публикация