фяцнента устройства, входы г-х составляющих (f 1,... , п) т-го и п-го коэффициентов устройства соединены с соответствующими входами соответственно (2j-l)-ro и 2у-го импульсных регулируемых элементов, к-е выходы (2г-1)-го и ( ,. ..., п-р+ 2,.. ,,п)импульсных регулируемых элементов соединены с первыми входами ()-го и 2k-ro элементов И, соответствующих ()-й и групп, 1-е вьжоды первого и второго импульсных регулируемых элементов соединены с первыми входами ()-го и элементов И соответственно первой и второй групп, выходы (2Е-1)-го и 2Е-ГО элементов И первой группы соединены с первыми входами элементов ИЛИ, соответственно первой и второй групп, выходы (2f-I)-ro и 2Е-ГО элементов И второй группы соединены с вторыми входами соответствующих -х элементов ИЛИ первой и второй групп, выходы (2К-1)-го и 2К-ГО элементов И (22-1)-й группы соединены с соответствующими номеру группы входами -х элементов ИЛИ соответственно первой и второй групп, выходь ()-го и 2k-го элементов И группы соединены с входами f-x элементов ШШ соответственно первой и второй групп вторые .входы (2К.-)-х элементов И первой и второй групп соединены с входами положительных знаков -х составляющих соответственно первого и второго слагаемых устройства, входы элементов И первой и второй групп соединены с входами отрицательных знаков f-x составляющих первого и второго слагаемых устройства, выходы f-x элементов ИЛИ первой и второй групп соединены с входами уменьшаемого и вычитаемого соответствующих Е-X блоков вычитания, выходы положительного и отрицательного результатов которых соединены соответственно с первым и вторым входами

2-го элемента ИЛИ третьей группы, выI ,

ход j-ro элемента ИЛИ третьей группы

соединен с входом уменьшаемого соответствующего селекторного блока, чход вычитаемого которого соединен с выходом реэультата соответствующего .блока умножения, рзретьи входы 1-х элементов ИЛИ третьей группы соединены соответственно с выходами переноса соответствующих (t-l)-x селекторных блоков, выходы положительной

н отрицательной последовательностей |-го селекторного блока соединены соответственно с входами сложения и вычитания j-ro реверсивного счетчика, выходы разрядов Е-го реверсивного счетчика соединены с соответствующими входами Е-го преобразователя код-частота, выход которого соединен с входом первого сомножителя f.-ro блока умножения и является выходом -й составляющей результата устройст ва, вторые входы j-x блоков умножения являются входами соответственно j-x составляющих импульсной последовательности устройства, третьи входы - входами j-x составляющих нулевого коэффициента устройства, выходы сигналов положительного и отрицательного переносов , -х реверсивных счетчиков соединены с установочными входами соответствующих триггеров первой группы, первый установочный вход (2-1)-го триггера второй группы соединен с выходом соответствующего триггера первой группы и с первым входом управления соответствующего блока нормализации модуля, второй установочный вход (i-l )-го триггера второй группы соединен с выходом соответствующего элемента ИЛИ четвертой группы, выход (-1 )-го триггера второй группы соединен с первым входом управления соответствующего блока нормализации знака, первые входы 2( -1) и 2(5-1)-го элементов И(2п+1)-н группы соединены с выходами соответственно положительного и отрицательного знаков результата(-1)-го блока вычитания и соответственно с вторым и третьим входами управления соответствующего блока нормализации знака, вторые входы - с выходами соответственно отрицательного л положительного знаков результата 1-го блока вычитания и вторым и третьим входами управления (Р-1)-го блока нормализации модуля, а выходы - соответственно с первым и вторым входами (2-1) -го элемента ИЛИ четвертой группы, входы первой и второй импульсных последовательностей блоков нормализации знака и блоков нормализации модуля являются соответственно входами импульсных последо, вательностей устройства, выходы последовательностей с первой по четвертую (-1)-го узла нормализации модуля соединены соответственно с(2Р-1 )-ми входами (-1)-х элементов ИЛИ первой и второй гру-пп и (2 +и-ми входами -X элементов ИЛИ первой и второй групп, выходы с первого по четвертый (Р- О-го узла нормализации знака соединены соответственно с ()-ми входами (Г-1)-X элементов ИЛИ первой и второй групп .и с (2 + + 1)-ми входами -х элементов ИЛИ пе вой и второй групп I выходы положительного знака результата блоков вычитания соединены с соответствующими входами элемента ИЛИ, выход которого является выходом знака результата устройства.

2. Устройство по п.1, отличающееся тем, что селекторный блок содержит вычитатель, элемент ИЛИ, элемент И, узел сравнения частот, при этом входы уменьшаемого и вычитаемого вычитателя являются соответствующими входами селекторног блока, первый выход вычитателя соединен с соответствующими входами элемента ИЛИ и первого элемента И, второй выход - с вторым входом элемента ИЛИ и первым входом второго элемента И, выход элемента ИЛИ соединен с первыми входами узла сравн ния частот и третьего элемента И, второй вход узла сравнения частот соединен с источником эталонной импульсной последовательности селекторного блока, первый выход - с вторыми входами первого и второго элементов И, второй выход - с вторым входом третьего элемента И, выход которого соединен с входом умножителя, выход умножителя и выходы первого и второго элементов И являются соответственно выходами переноса H выходми отрицательной и положительной импульсных последовательностей селекторного блока.

3. Устройство по п,1, о т л и чающеес я тем, что блок нормализации знака содержит шесть элементов И, первые входы первого и второго элементов И являются первым входом управления блока, вторые входы соответственно входами первой и второй импульсных последовательностей, выход первого элемента И соединен с первыми входами третьего и четвертого элементов-И, выход второго элемента И соединен: с первыми входами пятого и шестого элементов И, вторые входы третьего и пятого элементов И .являются вторым входом управления блока, вторые входы четвертого и шестого элементов И являются третьим входом управления блока, выходы элементов И с третьего по шестой являются выходами импульсных последовательностей с первой по четвертую блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU983704A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для интерполяции | 1985 |

|

SU1264202A1 |

| Цифровой преобразователь координат | 1980 |

|

SU943715A1 |

| Устройство для деления | 1981 |

|

SU1051535A1 |

| Устройство для преобразования Фурье | 1984 |

|

SU1195358A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

1. УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ЧАСТОТНЫХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее первый и второй импульсные регулируемые элементы, первый блок вычитания, первый блок умножения, первый реверсивный счетчик, первый преобразователь код-частота, причем первые выходы первого и второго импульсных регулируемых элементов соединены соот- . ветственно с первыми входами первого и второго элементов И соответствующих групп, вторые входы первых элементов И первой и второй групп соединены с входами положительных знаков первых составляющих соответственно первого и второго слагаемых. устройств, вторые входы вторых элементов И первой и «торой групп соединены с входами отрицательных зна.ков вторых составляющих соответственно первого и второго слагаемых устройств, выходы первого и второго элементов И первой группы соединены с первыми входами первых элементов ИЛИ соответственно первой и второй групп, выходы первого и второго элементов И второй группы - с вторыми входами первых элементов ИЛИ соответственно первой и второй групп, выходы которых соединены соответственно с входами уменьшаемого и вычитаемого первого блока вычитания, вы ходы положительного и отрицательного результатов которого соединены соответственно с первым и вторым входами первого элемента ИЛИ третьей группы, выходы разрядов первого реверсивного счетчика соединены с соответствующими входами первого преобразователя код-частота, выход которого соединен с входом первого сомножителя первого блока умножения (Л и является выходом первой составляющей результата устройства, о т л и 1ающееся тем, что, с целью повышения быстродействия, в него введены селекторш.1е блоки, Д 2п-2)импульсных регулируемых элементов п- число составляющих каждого слагаемого. ,

Изобретение относится к вычислительной технике и может быть использовано при построении частотно-импульсных вычислительных устройств высокой производительности, обладаю- 5 щих высокой точностью в статическом и дина:мическом режимах.

Цель изобретения - повьшение быстродействия.

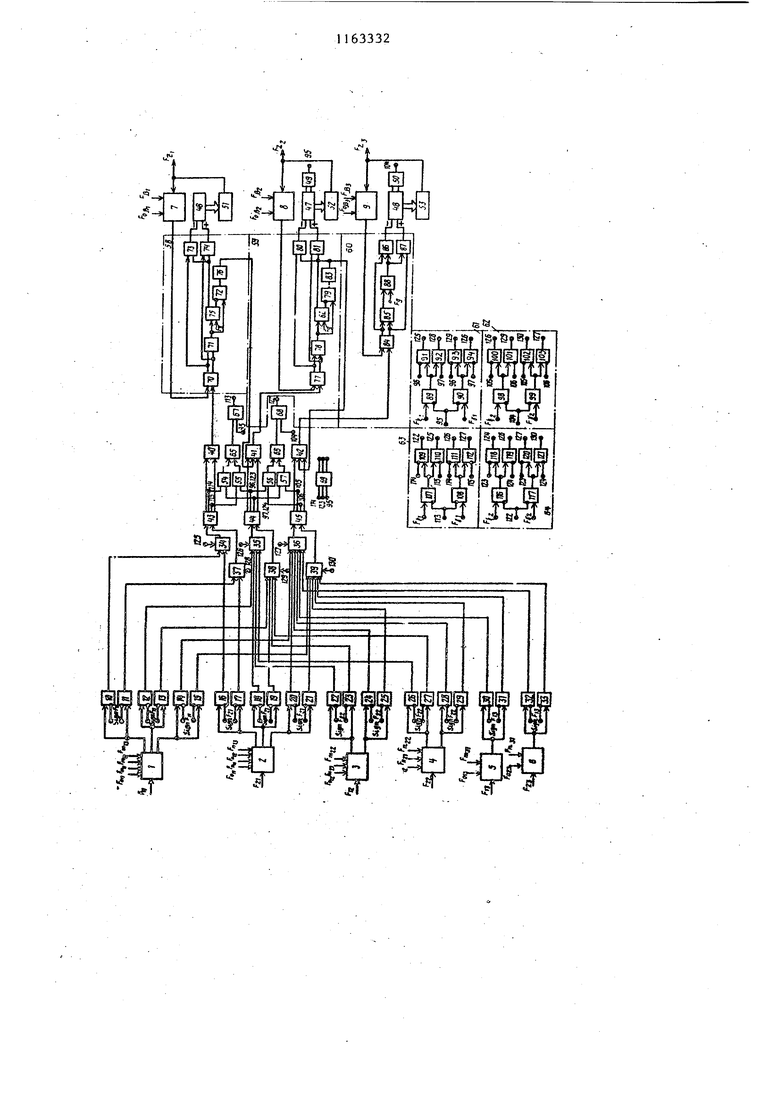

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство рассматривается в ва- . рианте для случая двух слагаемых(Р«2} tS и трёх каналов ) для представления составляющих слагаемых, масштабных коэффициентов и выходного сигнала.

Устройство содержит импульсные регулируемые элементы(ИРЭ) 1-6, блоки 7-9 умножения, элементы И 10 - 15 первой группы, элементы И 16 - 21 второй группы, элементы И 22 - 25 третьей группы, элементы И 26 - 29. четвертой группы,элементы И 30 и 31 пятой группы, элементы И 32 и 33 шестой группы, элементы ИЛИ 34 - 36 первой группы, элементы ИЛИ 37 - 39 второй группы, элементы ИЛИ 40 - 42 третьей группы, блоки 43 - 45 вычитания, .реверсивные счетчики46,- 48, триггеры 49 и. 50 первой группы, преобразователи 51 - 53 код - частота, элементы И 54 - 57 седьмой группы, селекторные блоки 58 - 60, блоки 61 и 62 но мализации модуля, блоки 63 и 6А нор мализации знака, элементы ИЛИ 65 и 66 четвертой группы, Т15иггеры 67 и 68 второй группы, элемент ИЛИ 69. Блок 58 содержит вычитатель 70,элемент ИЛИ 71, элементы И 72-74,узел 75 сравнения частот, умножитель 76. Кяок 59 содержит вычитатель 77,элемент ИЛИ 78, элементы И 79-81, узел 82 сравнения частот, умножитель 83. Блок 60 содержит вычитатель 84, эле мент ИЛИ 85, элементы И 86 и 87, узел 88 сравнения частот. Блок 61 с держит элементы И 89 - 94, входы 95-97 управления. Блок 62 содержит элементы И 98 - 103, входы 104 106 управления. Блок 63 содержит эл менты И 107 - 112, входы 113 - 115 управления. Блок 64 содержит элемен ты И 116 - 121, входы 122 - 124 управления. Элементы ИЛИ 34 - 39 имею дополнительные входы 125 - 130, сое диненные с выходами импульсных последозатбльностей блоков 61 - 64. Устройство работает следующим образом. Предположим, что необходимо ре ализовать операцию суммирования в обобщенном виде р Z ,X ,1 ТУ СО при представлении масштабных коэффи циентов и слагаемых в виде суммы составляющих пп V|iV r V, сучетом выражения (2) сумма (1) может быть записана, как V V -V .|r. CI где n - число составляющих слагаеMi.rs и Масштабных коэффициентов j р - число слагаемых. С уменьшением порядкового номера составляющих слагаемого можно снижать тачност:. представления соответ ствующего масштабного коэффициента без внесения дополнительной погрешности в результату, операции, выражение (3)„прииимает вид Р ппНИ Z-Z51x 51л,, ; () -1 откуда нетрудно записать соотношение для определения числа элементов И для представления знака слагаемых R 2 р (а, +ап)п - убывающая арифметическая прогрессия;+ d(n-l); а,1; d 1. С учетом значений а, а, R (1 +п)п р Для определения динамических характеристик устройства необходимо располагать значением числа слагаемых каждого канала 0- .представляющих произведение составляющих слагаемых и результата операции на масштабные коэффициенты, характеризуемые одинаковыми пределами изменения, Учитыва;., что при представлении составляющих слагаемых, результата операции и масштабных коэффициентов, используется принцип равномерного разбиения и принимая во внимание выражение (4) где 1 - порядковый номер канала; р - число слагаемых. Так как носителем информации является частота следования импульсов, представляющая временной п&раметр, целесообразно диапазоны изменения частот Гц составляющих слагаемых, масштабных коэффициентов и результата операции выбирать равными и лежащими в области высоких частот: i ( Ю); F,2 у ( Ю); 7 ()i i( lo); F, i() 15 2 j t i( 2 ( 10)iF2, 10) Максимальные значения частот составляющих масштабных коэффициентов выбираются согласно выражению F - «; Itp, « - предельная частота переключения выбранной элементной базы. F F -. in пгг nil 2 FOU F 012 F 013 Foai Foa2 F023F, F, 10 104 Моделирующие зависимости устрой ства имеют вид С учетом значений частот состав ляющих слагаемых и масштабных коэффициентов пределы изменения вход ных частот F2i (); F2i ( 10); F2j( Назначением селекторного блока является выделение из сигналов рас согласования Fg, которые формируют ся на выходе вычитателей 70, 77 и 84, составляющих, пропорциональных целой и дробной частей результата F. Рассмотрим функционирование селекторных блоков 58 - 60 на примере блока 59. Предположим, что один из входных сигналов получает приращение в виде скачка. Так как в общем случае в выходном сигнале вычитателя 77 имеют место .составля щие, пропорциональные целой и дроб ной частям выходной частотно-импульсной последовательности н первом выходе узла 82 формируется разрешающий, а на втором - запрещающий сигналы. Последовательность Fg поступает на вход счетчика 47. Так как преобразователь 52 формиру результирующий сигнал, содержащий только целые части, то по завершен переходного процесса на выходе выч тателя 77 имеет место сигнал, равн нулю либо соответствующий дроЗной части ,2. приводит соответственно к формированию разрешающего сигнала на втором выходе узла 82. Импульсная последовательность, про ходя через элемент И 79 и умножитель 83, поступает на третий вход элемента РШИ 42. Назначением блоков 61 и 62 нормализации модулей является устранение возможного переполнения счетчиков соответствукяцих каналов и организация процесса переноса единиц в старшие разряды. Рассмотрим работу блоков 61 и 62.Предположик, что необходимо реализовать операцию вида Z Ах + By При этом ту 1; х 587893; у 109981. При числе составляющих сумма составляющих и основание слагаемых X, у равны х 58; Х2 78; х 100; у 10; y. у 100; Z, 68; Zj 177; 2 174. Из приведенного примера следует, что в третьем и втором каналах имеет место переполнение, что соответствует появлению разрешающих сигналов на выходах триггеров 49 и 50. Следовательно, элементы И 89, 90, 98 и 99 открыты по соответствующим входам. Так как составляющие слагаемых положительны, на выходах положительного результата вычитателей 44 и 45 формируются разрешающие сигналы, т.е. элементы И 91, 93, 100 и 102 открыты. Частота Fc, пропорциональная единице перзполнения с помощью элементов И 89 и 91 и элемента ИЛИ 34,просуммируется с составляющей первого канала. Аналогично с ,пропорциональная, единице переполнения с помощью элементов И 98 и 100 и элемента ИЛИ 36, просуммируется с составляющей-второго канала. При этом с помощью элементов И 90 и 93, ИЛИ 37 и элементов И 99 и 102, Ш1И 39 во второй и третий каналы поступают частоты , пропорциональные основанию в виде вычитаемых. Следовательно, результирующее выражение принимает вид Z, 69; Z2 78; Z 74. При уменьшении слагаемых, напримеру 101106 10; у. 11; в счетчиках 47 и 48 записывается отрицательное значение код я., что приводит к возвращению триггеров 49 и 50 в исходное состояние, при котором элементы 89, 90, 98 и 99 закрыты по соответствующим входам. При этом

прекращается поступление сигналов, пропорциональных единицам переполнения через элементы ИЛИ 34 и 35 и вычитаемых через элементы ИЛИ 38 и 39. Результат операции равен

Z 68; Z,j 89; Zj- 99.

Назначением блоков 63 и 64 является формирование знака составляющих выходного сигнала

При правильном формировании составляющих результата суммы их знаки должны соответствовать знаку старшей составляющей.

Предположим, что необходимо реализовать операцию алгебраического суммирования Z - х-у 587893-109981.

При выбранном числе каналов основание составляющих слагаемых равно 100, т.е. х у 100. Следовательно,

х,58;

У1 -99; УЗ -81

Z Г2.

Полученный результат Z является ошибочным, так как по нему нельзя определить знак результата операции, а модульные значения составляющих являются неверными.

Блок 63 устраняет выявленные выше ошибки при формировании результата суммы. Последнее реализуется следующим образом. При Полученном значении 7- имеют место сигналы на выходе положительного знака результата вычитателя 43 и на выходе отрицательного знака результата вычитателя 44, что приводит в свою очередь к появлению сигнала на выходах элементов И 54 и ИЛИ 65. В результате триггер 67 изменяет свое состояние, сформировав на выходе разрешающий

сигнал. Элементы И 107, 108, 109 и

111 открыты по соответствующем входам. На вход элемента ИЛИ 37 поступает частотно-импульсная последовательность качестве вычитаемого,

пропорциональная единице математической величины первого канала, на вход элемента ИЛИ 35 поступает сигнал Fj, пропорциональный основанию, который просуммируется с последовательностью второго канала. При этом корректируется результат операции суммирования

Z, 47; Д 79; Z 12. Триггер 67 находится во вновь

сформированном положении до тех пор, пока составляющие входных сигналов х и у не изменяются до значений, при которых наступает переполнение счетчика 47, что вызывает появление

возбуждающего сигнала на первом выходе триггера 67, при котором он возвращается в исходное положение.

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 0 |

|

SU217047A1 |

| Паламарюк Г.О | |||

| Комбинированные вычислительные устройства | |||

| Рязань, 1975, с.98 | |||

| Авторское свидетельство СССР № 762010, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-23—Публикация

1979-07-27—Подача