112

Изобретение относится к вычислительной технике и может быть использовано в качестве одного из q-иЧных разрядов многоразрядного позиционного арифметического устройства быстро действующих вычислительных машин. Цель изобретения - расширение функциональных возможностей за счет выполнения обратного вычитания и сложения содержимого сумматора с единицей.

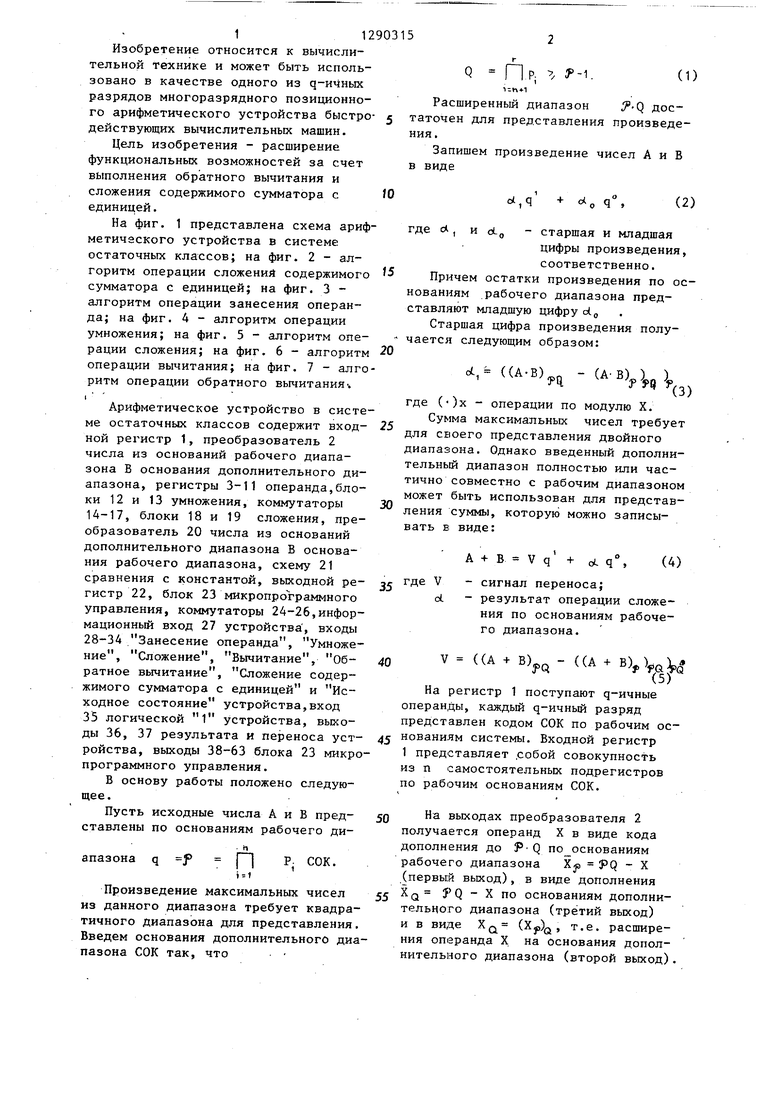

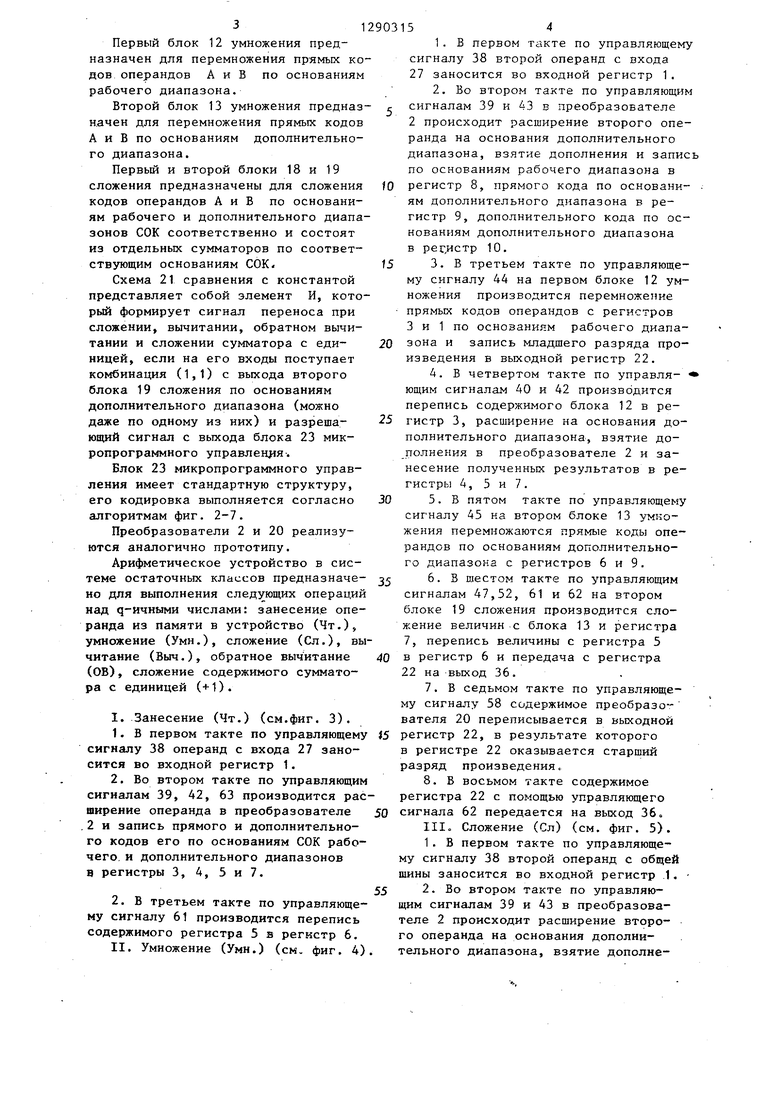

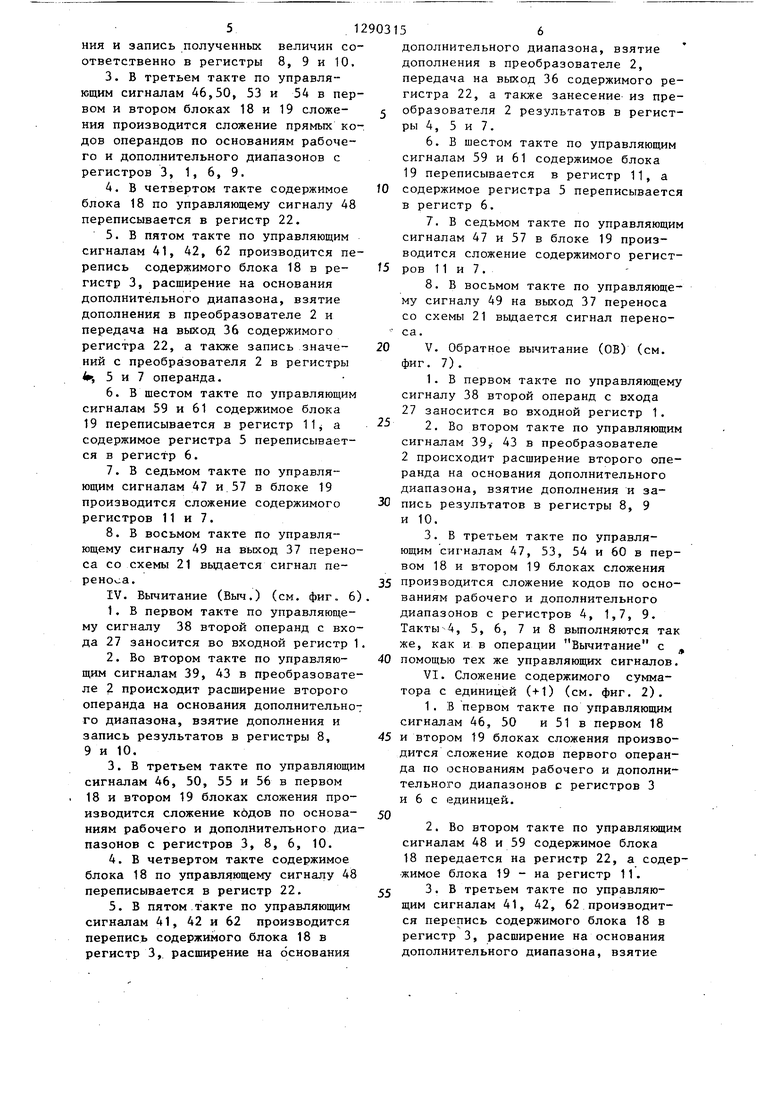

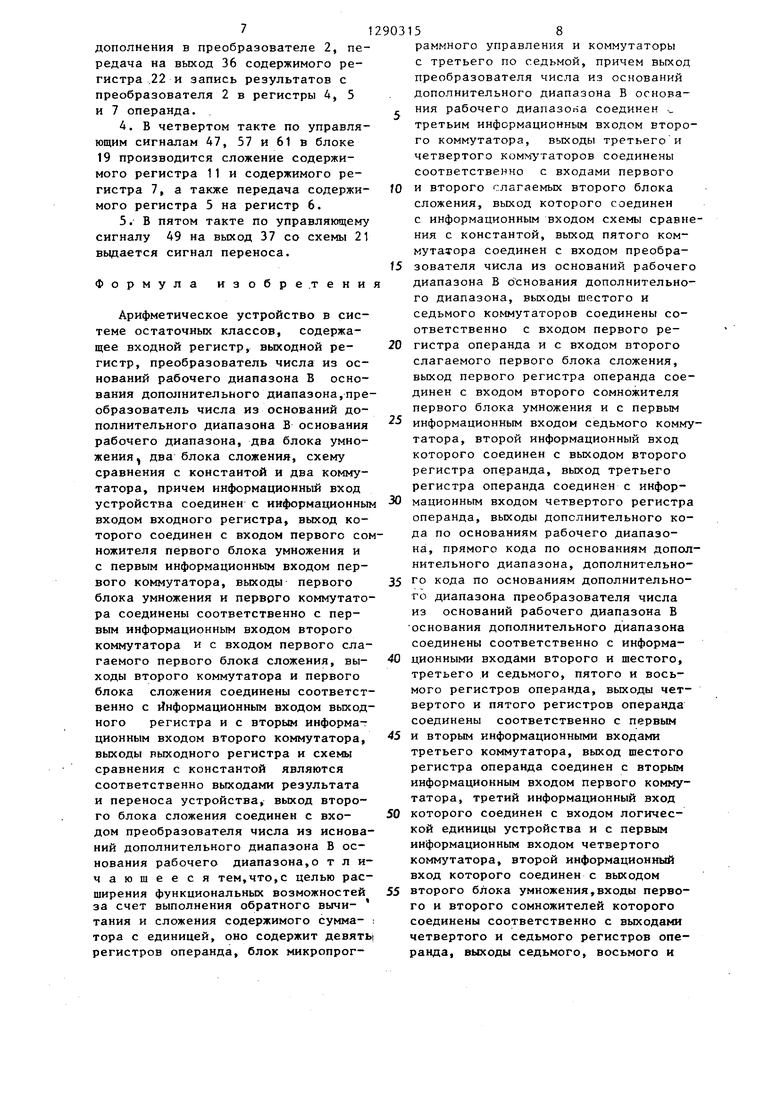

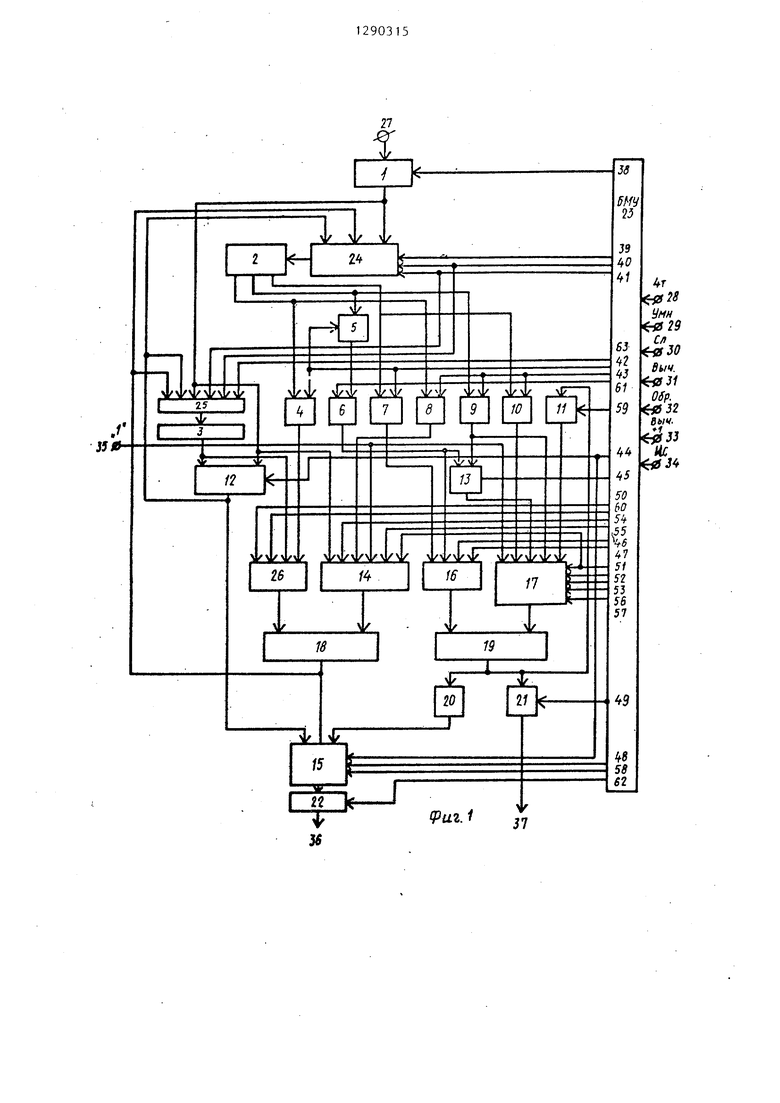

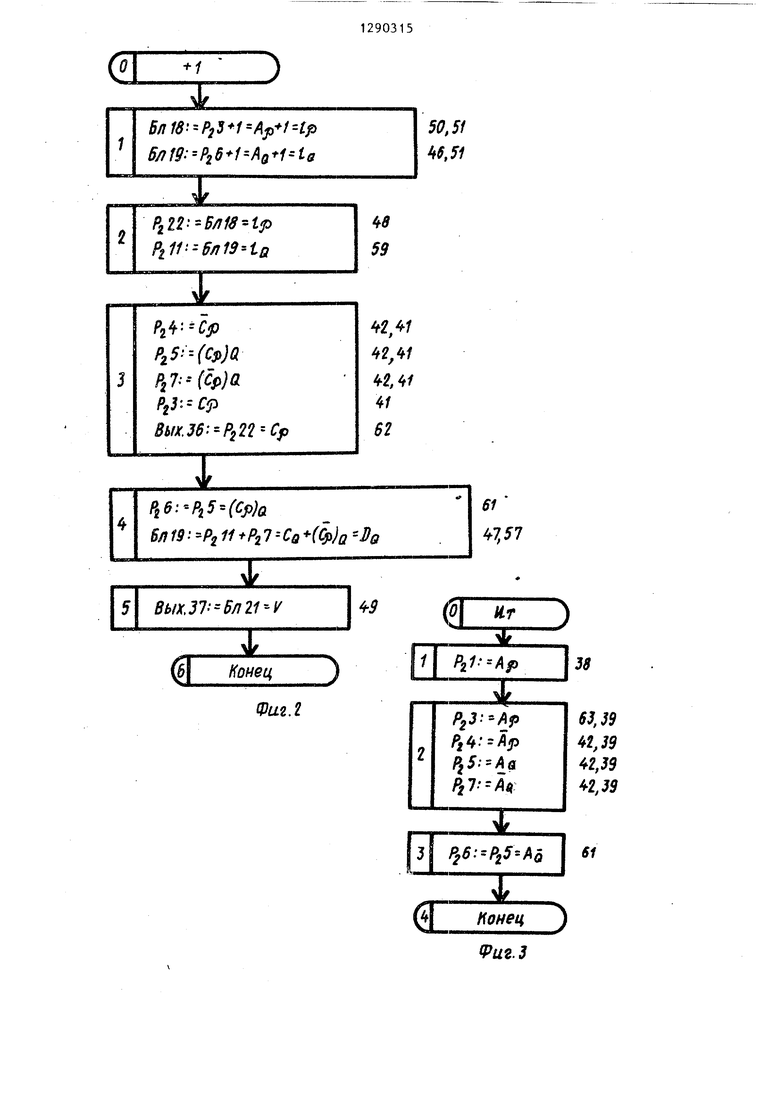

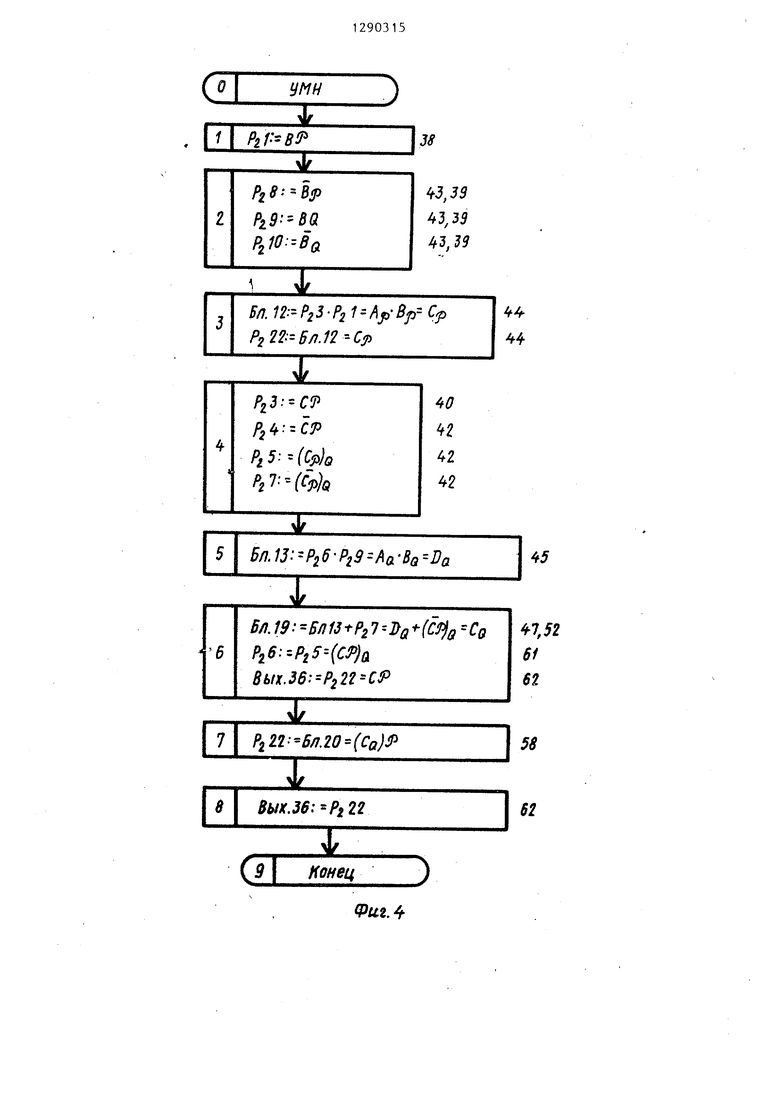

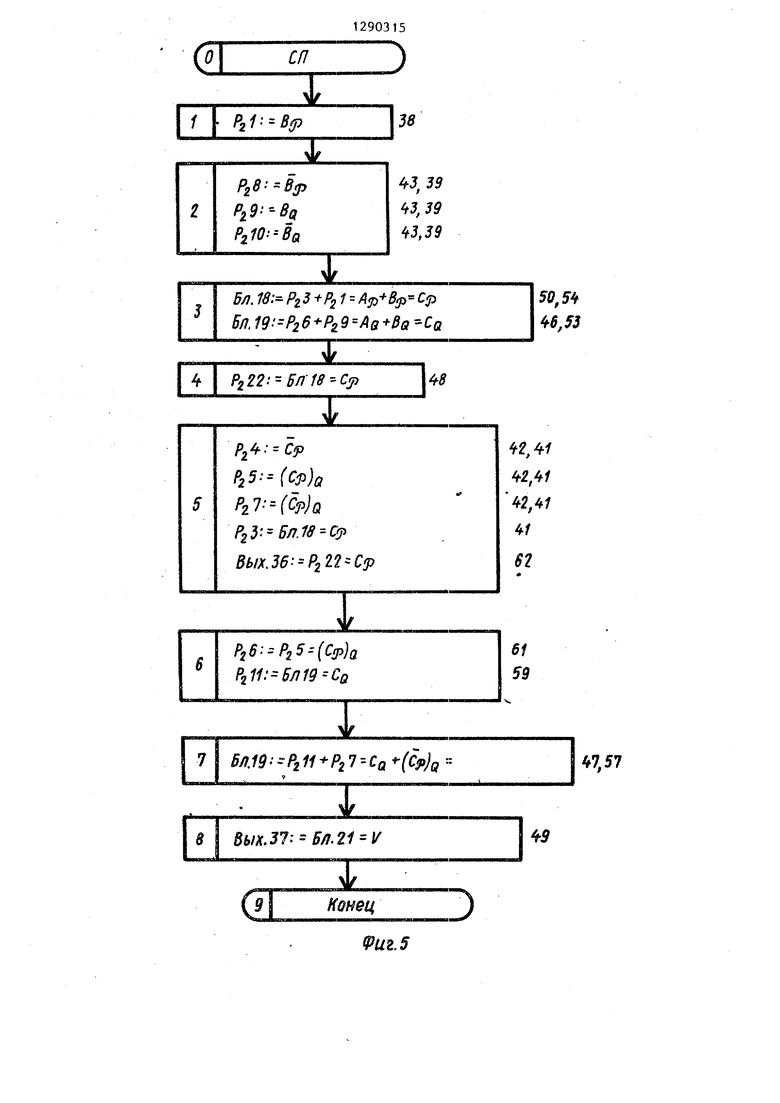

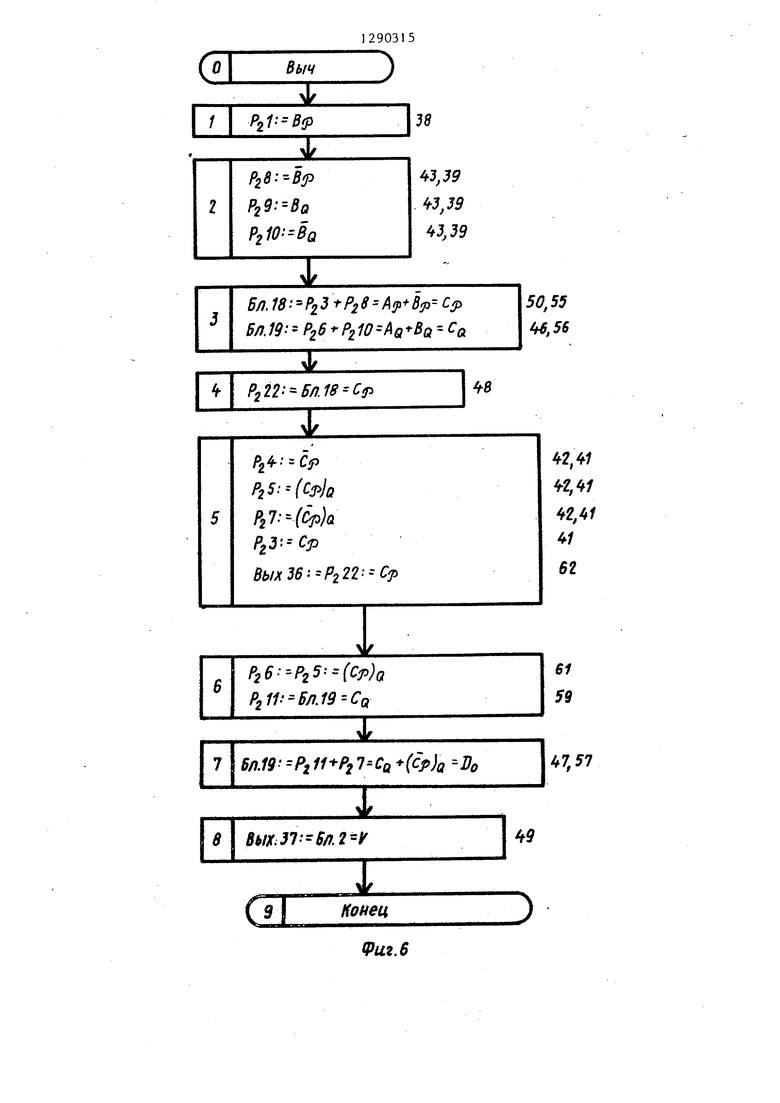

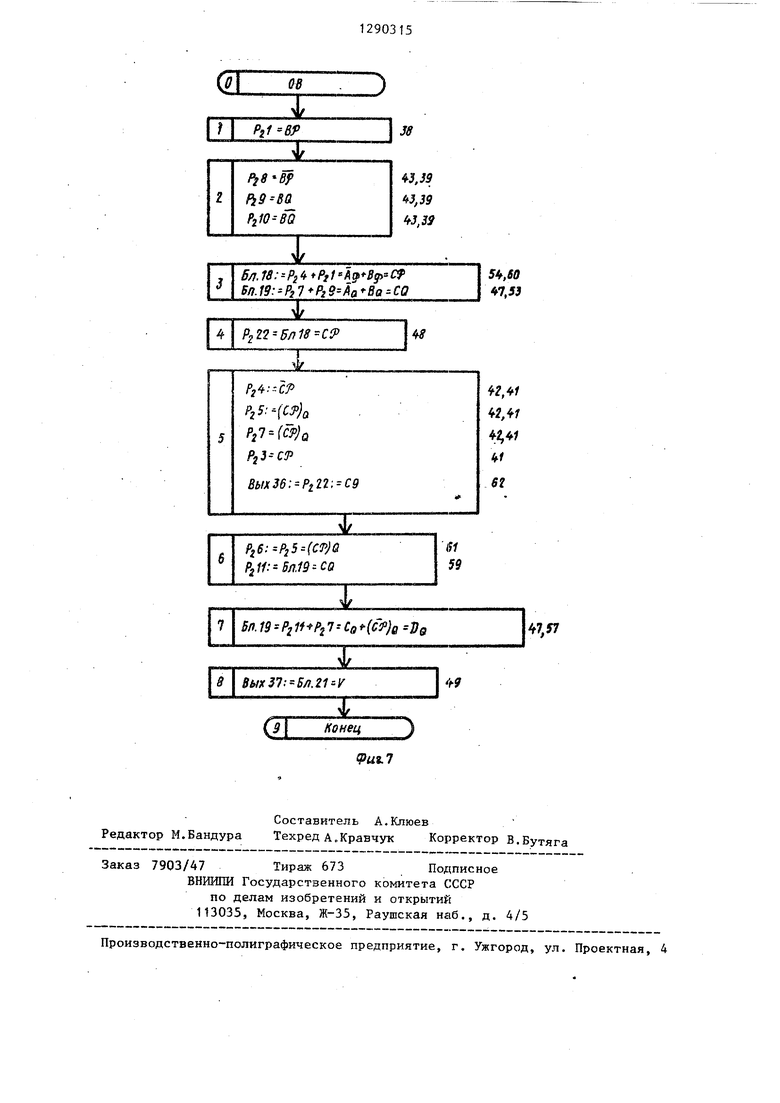

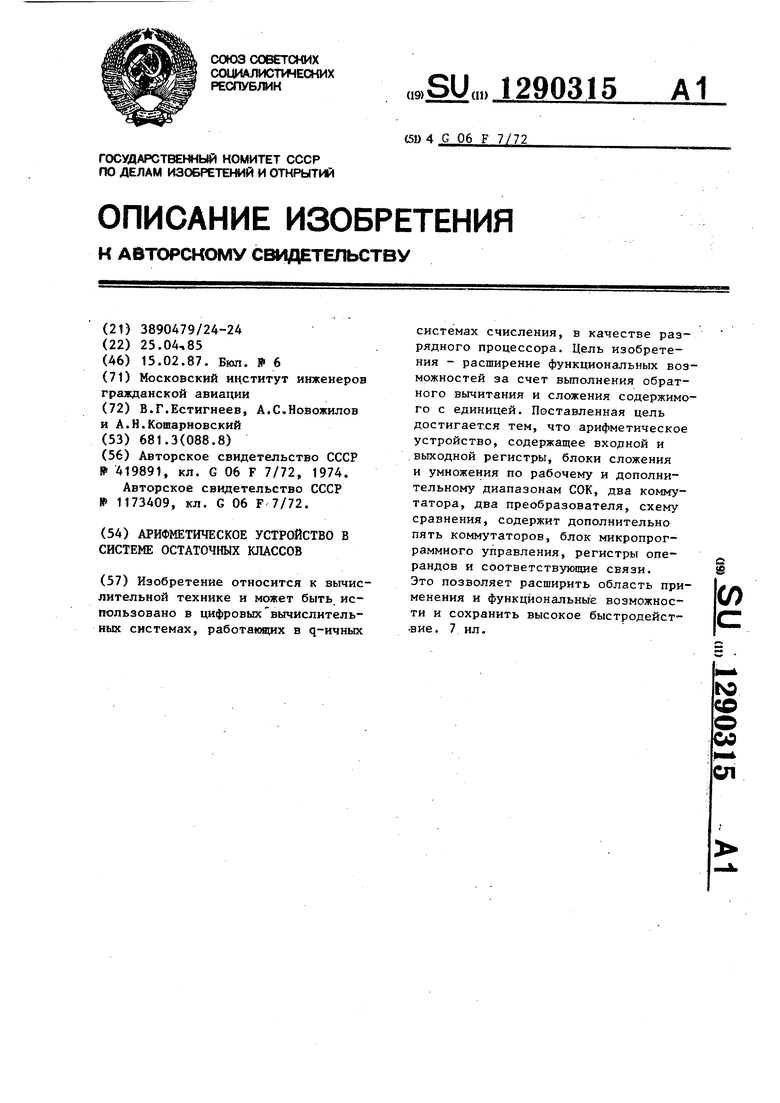

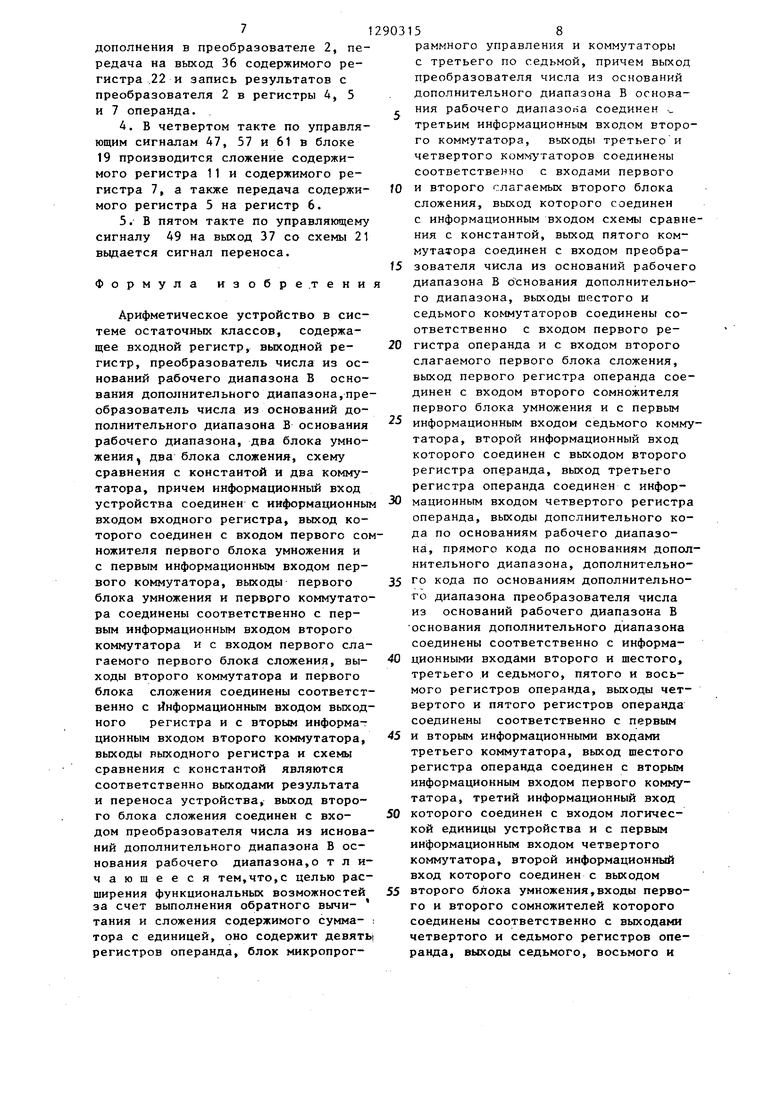

На фиг. 1 представлена схема арифметического устройства в системе остаточных классов; на фиг. 2 - алгоритм операции сложений содержимого сумматора с единицей; на фиг. 3 - алгоритм операции занесения операнда; на фиг. 4 - алгоритм операции умножения; на фиг. 5 - алгоритм операции сложения; на фиг. 6 - алгоритм операции вычитания; на фиг. 7 - алгоритм операции обратного вычитания .

I

Арифметическое устройство в системе остаточных классов содержит вход- ной регистр 1, преобразователь 2 числа из оснований рабочего диапазона В основания дополнительного диапазона, регистры 3-11 операнда,блоки 12 и 13 умножения, коммутаторы 14-17, блоки 18 и 19 сложения, преобразователь 20 числа из оснований дополнительного диапазона В основания рабочего диапазона, схему 21 сравнения с константой, выходной ре- гистр 22, блок 23 микропрограммного управления, коммутаторы 24-26,информационный вход 27 устройства , входы 28-34 Занесение операнда, Умножение, Сложение, Вычитание, Об- ратное вычитание, Сложение содержимого сумматора с единицей и Исходное состояние устройства,вход 35 логической 1 устройства, выходы 36, 37 результата и переноса уст- ройства, выходы 38-63 блока 23 микропрограммного управления.

В основу работы положено следующее.

Пусть исходные числа А и В пред- ставлены по основаниям рабочего диР. СОК.

апазона q f j |

i i

Произведение максимальных чисел из данного диапазона требует квадратичного диапазона для представления. Введем основания дополнительного диапазона СОК так, что

Q П.р. х -1.

(1)

Расширенный диапазон -Q достаточен для представления произведения.

Запишем произведение чисел А и Б в виде

ot,q + q

(2)

где с, и oLg - старшая и младшая

цифры произведения, соответственно.

Причем остатки произведения по основаниям .рабочего диапазона представляют младшую цифру dg

Старшая цифра произведения получается следующим образом:

с.,-((А.В) -(А.В)))

где (Ох - операции по модулю X.

Сумма максимальных чисел требует для своего представления двойного диапазона. Однако введенный дополнительный диапазон полностью или частично совместно с рабочим диапазоном может быть использован для представления суммы, которую можно записывать в виде:

А + В V q + oL q%

(4)

где V - сигнал переноса;

Ы - результат операции сложения по основаниям рабочего диапазона.

V ((А+ В)- ((А+ В),))р

На регистр 1 поступают q-ичные операнды, каждый q-ичньй разряд представлен кодом СОК по рабочим основаниям системы. Входной регистр 1 представляет .собой совокупность из п самостоятельных подрегистров по рабочим основаниям СОК.

На выходах преобразователя 2 получается операнд X в виде кода дополнения до Р Q по основаниям рабочего диапазона Х,р PQ - х (первый выход), в виде дополнения XQ У Q - X по основаниям дополнительного диапазона (третий выход) и в виде XQ (XJ,)Q , т.е. расширения операнда X на основания дополнительного диапазона (второй выход).

Первый блок 12 умножения предназначен для перемножения прямых кодов операндов А и В по основаниям рабочего диапазона.

Второй блок 13 умножения предназначен для перемножения прямых кодов А и В по основаниям дополнительного диапазона.

Первьш и второй блоки 18 и 19 сложения предназначены для сложения кодов операндов А и В по основаниям рабочего и дополнительного диапазонов СОК соответственно и состоят из отдельных сумматоров по соответствующим основаниям СОК.

Схема 21 сравнения с константой представляет собой элемент И, который формирует сигнал переноса при сложении, вычитании, обратном вычитании и сложении сумматора с единицей, если на его входы поступает комбинация (1,1) с выхода второго блока 19 сложения по основаниям дополнительного диапазона (можно даже по одному из них) и разрешающий сигнал с выхода блока 23 микропрограммного управлен 1я.

Блок 23 микропрограммного управления имеет стандартную структуру, его кодировка выполняется согласно алгоритмам фиг. 2-7.

Преобразователи 2 и 20 реализуются аналогично прототипу.

Арифметическое устройство в системе остаточных классов предназначено для выполнения следующих операций над q-ичными числами: занесение операнда из памяти в устройство (Чт.), умножение (Умн.), сложение (Сл.), вычитание (Выч.), обратное вычитание (ОБ), сложение содержимого сумматора с единицей (-«-1).

I, Занесение (Чт.) (см.фиг. 3).

1.В первом такте по управляющему сигналу 38 операнд с входа 27 заносится во входной регистр 1.

2.Во втором такте по управляющим сигналам 39, 42, 63 производится расширение операнда в преобразователе

,2 и запись прямого и дополнительного кодов его по основаниям СОК рабочего, и дополнительного диапазонов В регистры 3, 4, 5 и 7.

2. В третьем такте по управляющему сигналу 61 производится перепись содержимого регистра 5 в регистр 6.

II. Умножение (Умн.) (см. фиг. 4)

1.В первом такте по управляющему сигналу 38 второй операнд с входа

27 заносится во входной регистр 1.

2.Во втором такте по управляющим с сигналам 39 и 43 в преобразователе

2происходит расширение второго операнда на основания дополнительного диапазона, взятие дополнения и запись по основаниям рабочего диапазона в

O регистр 8, прямого кода по основами- . ям дополнительного диапазона в регистр 9, дополнительного кода по основаниям дополнительного диапазона в регистр 10.

5 3. В третьем такте по управляющему сигналу 44 на первом блоке 12 умножения производится перемножение прямых кодов операндов с регистров

3и 1 по основаниям рабочего диапа- 0 зона и запись младшего разряда произведения в выходной регистр 22.

4. В четвертом такте по управля- ющим сигналам 40 и 42 производится перепись содержимого блока 12 в ре5 гистр 3, расширение на основания дополнительного диапазона, взятие дополнения в преобразователе 2 и занесение полученных результатов в регистры 4, 5 и 7.

0 5. Б пятом такте по управляющему сигналу 45 ка втором блоке 13 умножения перемножаются прямые коды операндов по основаниям дополнительного диапазона с регистров 6 и 9.

2 6. В шестом такте по управляющим сигналам 47,52, 61 и 62 на втором блоке 19 сложения производится сложение величин с блока 13 и регистра 7, перепись величины с регистра 5

0 в регистр 6 и передача с регистра 22 на выход 36.

7.В седьмом такте по управляющему сигналу 58 содержимое преобразователя 20 переписывается в выходной

S регистр 22, в результате которого в регистре 22 оказывается старший разряд произведения.

8.Б восьмом такте содержимое регистра 22 с помощью управляющего

0 сигнала 62 передается на выход 36. III, Сложение (Сл) (см. фиг. 5). 1. В первом такте по управляющему сигналу 38 второй операнд с общей шины заносится во входной регистр .1, 5 2. Во втором такте по управляющим сигналам 39 и 43 в преобразователе 2 происходит расширение второго операнда на основания дополнительного диапазона, взятие дополнения и запись полученных величин соответственно в регистры 8, 9 и 10.

3.В третьем такте по управляющим сигналам 46,50, 53 и 54 в первом и втором блоках 18 и 19 сложе- ния производится сложение прямых кодов операндов по основаниям рабочего и дополнительного диапазонов с регистров 3, 1, 6, 9.

4.В четвертом такте содержимое блока 18 по управляющему сигналу 48 переписывается в регистр 22.

5.В пятом такте по управляющим сигналам 41, 42, 62 производится перепись содержимого блока 18 в ре- гистр 3, расширение на основания дополнительного диапазона, взятие дополнения в преобразователе 2 и передача на выход 36 содержимого регистра 22, а также запись значе- НИИ с преобразователя 2 в регистры

i 5 и 7 операнда.

6.В шестом такте по управляющим сигналам 59 и 61 содержимое блока

19 переписывается в регистр 11j а содержимое регистра 5 переписывается в регистр 6.

7.В седьмом такте по управляющим сигналам 47 и.57 в блоке 19 производится сложение содержимого регистров 11 и 7.

8.В восьмом такте по управляющему сигналу 49 на вькод 37 переноса со схемы 21 вьщается сигнал переноса.

IV. Вычитание (Выч.) (см. фиг.. 6

1.В первом такте по управляющему сигналу 38 второй операнд с входа 27 заносится во входной регистр 1

2.Во втором такте по управляю- щим сигналам 39, 43 в преобразователе 2 происходит расширение второго операнда на основания дополнительно

го диапазона, взятие дополнения и запись результатов в регистры 8, 9 и 10.

3.В третьем такте по управляющи сигналам 46, 50, 55 и 56 в первом

18 и втором 19 блоках сложения производится сложение кбдов по основа- ниям рабочего и дополнительного диапазонов с регистров 3, 8, 6, 10.

4.В четвертом такте содержимое блока 18 по управляющему сигналу 48 переписывается в регистр 22.

5.В пятом такте по управляющим сигналам 41, 42 и 62 производится перепись содержимого блока 18 в регистр 3, расширение на основания

дополнительного диапазона, взятие дополнения в преобразователе 2, передача на выход 36 содержимого регистра 22, а также занесение из преобразователя 2 результатов в регистры 4, 5 и 7.

6.В шестом такте по управляющим сигналам 59 и 61 содержимое блока 19 переписывается в регистр 11, а содержимое регистра 5 переписывается в регистр 6.

7.В седьмом такте по управляющим сигналам 47 и 57 в блоке 19 производится сложение содержимого регистров 11 и 7 .

8.В восьмом такте по управляющему сигналу 49 на выход 37 переноса со схемы 21 выдается сигнал переноса.

V.Обратное вычитание (ОВ) (см. фиг. 7).

1.В первом такте по управляющему сигналу 38 второй операнд с входа

27 заносится во входной регистр 1.

2.Во втором такте по управляющим сигналам 39,- 43 в преобразователе

2 происходит расширение второго операнда на основания дополнительного диапазона, взятие дополнения и запись результатов в регистры 8, 9 и 10.

3.Б третьем такте по управляющим сигналам 47, 53, 54 и 60 в первом 18 и втором 19 блоках сложения производится сложение кодов по основаниям рабочего и дополнительного диапазонов с регистров 4, 1,7, 9. Такты-4, 5, 6, 7 и 8 вьшолняются так же, как и в операции Вычитание с помощью тех же управляющих сигналов.

VI.Сложение содержимого сумматора с единицей () (см. фиг. 2).

1.В первом такте по управляющим сигналам 46, 50 и 51 в первом 18

и втором 19 блоках сложения производится сложение кодов первого операнда по основаниям рабочего и дополнительного диапазонов с регистров 3 и 6 с единицей.

2.Во втором такте по управляющим сигналам 48 и 59 содержимое блока

18 передается на регистр 22, а содержимое блока 19 - на регистр 11.

3.В третьем такте по управляющим сигналам 41, 42, 62 производится перепись содержимого блока 18 в регистр 3, расширение на основания дополнительного диапазона, взятие

7

дополнения в преобразователе 2, передача на выход 36 содержимого регистра .22 и запись результатов с преобразователя 2 в регистры 4, 5 и 7 операнда.

4.В четвертом такте по управляющим сигналам 47, 57 и 61 в блоке 19 производится сложение содержимого регистра 11 и содержимого регистра 7, а также передача содержи- мого регистра 5 на регистр 6.

5.В пятом такте по управляющему сигналу 49 на выход 37 со схемы 21 выдается сигнал переноса.

Формула изобретени

Арифметическое устройство в системе остаточных классов, содержащее входной регистр, выходной ре- гистр, преобразователь числа из оснований рабочего диапазона В основания дополнительного диапазона,преобразователь числа из оснований дополнительного диапазона В основания рабочего диапазона, два блока умножения, два блока сложения, схему сравнения с константой и два коммутатора, причем информационный вход устройства соединен с информационны входом входного регистра, выход которого соединен с входом первого соножителя первого блока умножения и с первым информационным входом первого коммутатора, выходы первого блока умножения и первого коммутатора соединены соответственно с первым информационным входом второго коммутатора и с входом первого слагаемого первого блока сложения, вы- ходы второго коммутатора и первого блока сложения соединены соответственно с информационным входом выходного регистра и с вторым информационным входом второго коммутатора, выходы яыходного регистра и схемы сравнения с константой являются соответственно выходами результата и переноса устройства, выход второго блока сложения соединен с вхо- дом преобразователя числа из иснова ний дополнительного диапазона В основания рабочего диапазона,о т л и- чаюшееся тем,что,с целью расширения функциональных возможностей за счет выполнения обратного вычи- танин и сложения содержимого сумма- тора с единицей, оно содержит девять регистров операнда, блок микропрог5

3

5

0 5

158

раммного управления и коммутаторы с третьего по седьмой, причем выход преобразователя числа из оснований дополнительного диапазона В основания рабочего диапазона соединен . третьим информационньш входом второго коммутатора, выходы третьего и четвертого коммутаторов соединены соответственно с входами первого и второго слагаемых второго блока сложения, выход которого соединен с информационным входом схемы сравнения с константой, выход пятого коммутатора соединен с входом преобразователя числа из оснований рабочего диапазона В основания дополнительного диапазона, выходы шестого и седьмого коммутаторов соединены соответственно с входом первого регистра операнда и с входом второго слагаемого первого блока сложения, выход первого регистра операнда соединен с входом второго сомножителя первого блока умножения и с первым информационным входом седьмого коммутатора, второй информационный вход которого соединен с выходом второго регистра операнда, выход третьего регистра операнда соединен с информационным входом четвертого регистра операнда, выходы дополнительного кода по основаниям рабочего диапазона, прямого кода по основаниям дополнительного диапазона, дополнительного кода по основаниям дополнительного диапазона преобразователя числа из оснований рабочего диапазона В основания дополнительного диапазона соединены соответственно с информационными входами второго и шестого, третьего и седьмого, пятого и восьмого регистров операнда, выходы четвертого и пятого регистров операнда соединены соответственно с первым и вторым информационными входами третьего коммутатора, выход шестого регистра операнда соединен с вторым информационным входом первого коммутатора, третий информационный вход которого соединен с входом логической единицы устройства и с первым информационным входом четвертого коммутатора, второй информационный вход которого соединен с выходом второго блока умножения,входы первого и второго сомножителей которого соединены соответственно с выходами четвертого и седьмого регистров операнда, выходы седьмого, восьмого и

912

девятого регистров операнда со.едине- ны соответственно с третьим, четвертым и пятым информационными входами четвертого коммутатора, выход входного регистра соединен с первыми . информационными входами пятого и шестого коммутаторов, второй и третий информационные входы которых соединены соответственно с выходами первого блока умножения- и первого блока сложения, выход второго блока сложения соединен с информационным входом девятого регистра операнда, входы Занесение операнда, Умножение, Сложение, Вычитание, Обратное вычитание, Сложение содержимого сумматора с единицей и Исходное состояние устройства соединены соответственно с входами блока микропрограммного управления, вход разрешения приема входного регистра и первый управляющий вход пятого коммутатора.соединены соответственно, с первым и вторым выходами блока микропрограммного управления, третий и четвертый выходы которого соединены соответственно с вторым и третьим управляющими входаьш пятого коммутатора, входы разрешения приема второго, третьего и пятого регистров операнда соединены с пятым выходом блока микропрограммного управления, шестой выход которого соединен с входами разрешения приема шестого, седьмого и восьмого регистров операнда, вход разрешения первого блока умножения соединен с первым управляющим входом второго коммутатора и с седьмым выходом блока микропрограммного управления, вось

0

5

31

0

5

0

5

0

510

мой, девятый, десятый, одиннадцатый и тринадцатый выходы которого соединены соответственно с входом разрешения второго блока умножения, первым и вторым управляющими входами третьего коммутатора, вторым управляющим входом второго коммутатора, входом разрешения схемы сравнения с константой и с первым управляющим входом седьмого коммутатора, первый, второй и третий управляющие входы четвертого коммутатора соединены соответственно с четырнадцатым, пятнадцатым и шестнадцатым вькодами блока микропрограммного управления, семнадцатый, восемнадцатый, девятнадцатый, двадцатый, двадцать первый, двадцать второй, двадцать третий, двадцать четвертый, двадцать пятый и двадцать шестой выходы которого соединены соответственно с первым и вторым управляющими входами первого коммутатора, четвертым и пятым управляющими входами четвертого коммутатора, третьим управляющим входом второго коммутатора, входом разрешения приема девятого регистра операнда, вторым управляющим входом седьмого коммутатора, входом разрешения приема четвертого регистра, входом разрешения выдачи выходного регистра и с первым управляющим входом шестого коммутатора, второй и третий управляющие входы которого соединены соответственно с вторым и третьим управляющими входами пятого коммутатора, первьй управляющий вход четвертого коммутатора соединен с третьим управляющим входом первого, коммутатора.

(Риг.З

(0 Iy/JH

. ч

, I 1 I PjI -BS

71 гг-вл,го(Са)з

B ВЫХ..22

ОI f(offeцJ

38

3,39 43,39 4,39

4 4

4-7,52

6f

62

58

62

fpuiA

Редактор М.Бандура

Составитель А.Клюев

Техред А.Кравчук Корректор В.Бутяга

Заказ 7903/47 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

Изобретение относится к вычислительной технике и может быть, использовано в цифровых вычислительных системах, работающих в q-ичных системах счисления, в качестве разрядного процессора. Цель изобретения - расширение функциональных возможностей за счет вьтолнения обратного вычитания и сложения содержимого с единицей. Поставленная цель достигается тем, что арифметическое устройство, содержащее входной и выходной регистры, блоки сложения и умножения по рабочему и дополнительному диапазонам СОК, два коммутатора, два преобразователя, схему сравнения, содержит дополнительно пять коммутаторов, блок микропрограммного управления, регистры операндов и соответствующие связи. Это позволяет расширить область применения и функциональные возможности и сохранить высокое быстродействие. 7 ил. i (Л 1С со со ел

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 1972 |

|

SU419891A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор-умножитель | 1983 |

|

SU1173409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-25—Подача