1

Изобретение относится к автомати.ке и вычислительной технике и предназначено для индвкацгии вел.ич;И1Н.

Известен дискретный иидижатор, содержащий набор отдельных световых И:нди1каторных элемеитогв, образующих и-ндицирую-щий профИчЛь, приемный регистр, вьшолненный на триггерах, подключенный к дешифратору, связанному через транз.истор«ые ключи с ииди каторньпфи эле гента1ми, переключатели и логические схемы. Однако и и дин а тор ха1ра1ктеризуется недостаточной точностью отсчета, увеличение которой связано с увеличением дискретных световых индикаторов, количества элементов, ra6ap«TOiB.

Предлагаемый инди катор отличается от известнОГО тем, что в него введены упр аеления и входные разрядные ячейки, выполненные на схемах «И, первые входы которых Объединены по группам, выход одной ив схем «И ячей-ки i-oro р азряда подключен к единичному входу триггера соответствующего разряда прие.МНого регистра и соединен с .вьгходом одной из схем «И ячей-ки последующего разряда, а другие входы схем «И ячейки /-ОГО разряда, выходы которьгх Объедииены с выхода.ми схем «И ячеек предыдущих L-1 и I-2 разрядов соответственно, объединены и подключены через схемы «И к выходам три.ггера управления и через схему «ИЛИ и инверторы - к другим входам

схем «И входных разрядных ячеек, выходы

которых связаны с входами соответствующих

триггеров приемного регистра; выхо-ды дешифратора, объединенные в группы через

схемы «ИЛИ и переключатели связаны с

входами триггера упр.а1влени1я и с шиной

сброса в нуль триггеров приемного регистра.

Это позволяет увеличить точность отсчета

и уменьшить габариты прибора.

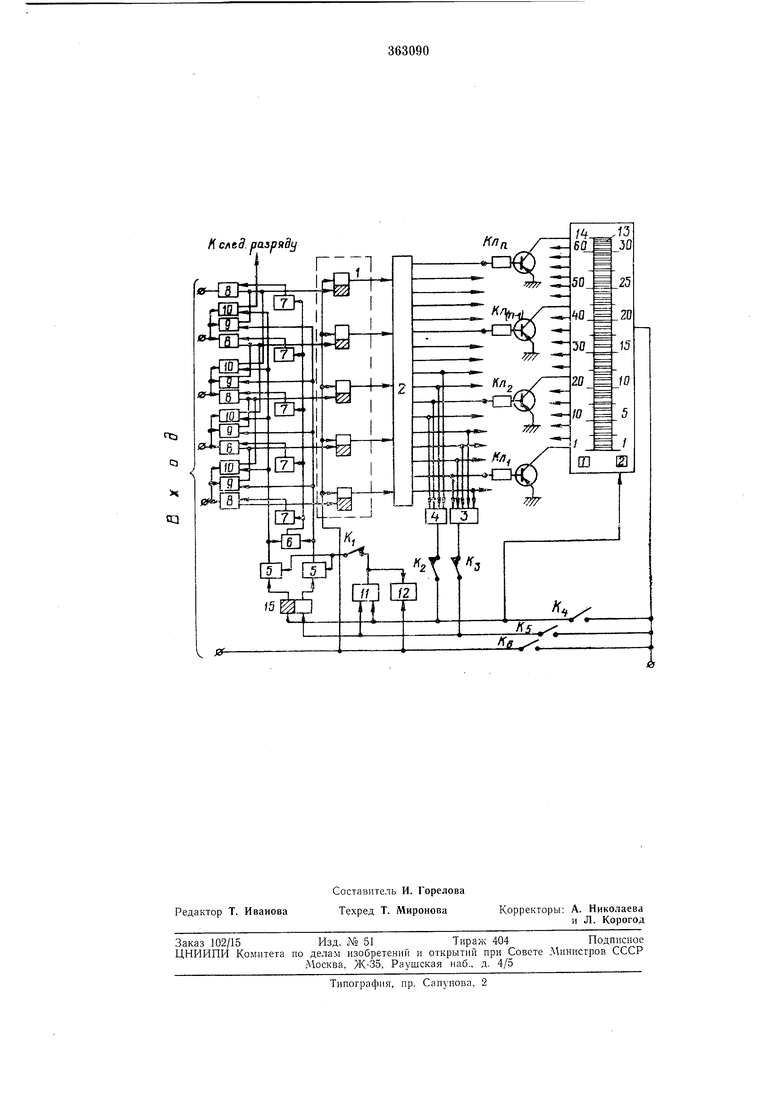

Иа чертеже изо.бражен llpeдлaгa. дискретный многопредельный индИКатор.

Устройство содержит приемный регистр /, дешифратор 2, схемы «ИЛИ 3 и 4, схемы

«И 5, схему «ИЛИ 6, инвертор 7, схемы «И 8. 9 10, схему «ИЛИ //, схему 12 сброса, индикаторные элементы 13, отсчетную шкалу 14, триггер 15 управления, транзисторные ключи , переключатель .

Устройство ра-ботает следующим образом.

Входной сигнал в дво1ИЧНОМ коде поступает

на приемный регистр / индикатора. Выходы

приемного регистра подключены к входу дешифратора 2, выходные щины которого разделены на группы. Потенциалы выходных шин групп через собирательные схемы «ИЛИ и 4 и нормально замкнутые контакты К-у и /(з управляют работой триггера

75 управления. ЕС ли I ,на щход регистра / аиришел коа, соответствлаошшй .вчсрой npyniiie шлш, то высокий 11оте1 гц1нал «1 ггройает через схему «ИЛИ 4 II шср&бросит триггер 15 в TaiKlOe положение, при .кОторЮМ потеищиал «1 с егю В1ьгхояа 5 г.ровдет через ехему «И 5 и, ic оциой стороны, постутит Через схему «ИЛИ 6 «а инвертО|ры «НЕ 7, отсутствие потенщиалз; на iiainpiysiKe которы-х з,а1Кроет схемьг «И 8 всех входных ,р.а|3рядныХ шин регистра 1, с другой 10 стороны, потеициал- «1 с выкода «И 5 поступит На iBce схемы «И 5 и, отэароет «к, тем cai.M.UiM КОд мл.адших раз:р Я д.о13 будет :одв:И1Н1у1Т в CTOipoiHy |Ста.р:Ш|И1х на один разр-яд. Если, сигнал |Пр1И1Ш:ел с третьей грудтны шии 15 де1ШИ:фр1атОра 2 схему «ИЛИ 3, то тришгер 15 буиет переброшен в другое положение. Пр1Н этом Bice разрядные схемы «И 8 будут закрыты, .а разрешающий нотенци ал с тришгера 15 noiCTynHT од новраменно на все20 схемы «И 10. TaiKHiM о.бр.азом,, iBiXoanou код сдви1нется уже н.а два разряда). При индикаггора без сдвига, т. е. в перисй групне шин дешифратора 2 1потенцИалы. с выхода. cx.eiM «ИЛИ 3 V( 4 не выда.ются25 и, следовательно, потаициал на выходе сх.е1мы «ИЛИ 11 отсутствует, те:м самым будут 3ia..Kip.biTbi схемы «И 5, на (Входе инверторов «НЕ 7 отсутствуют потенци а.лы. «О, .и- вььсокИ|й потапциал «1 с И1Х нагрузок п-остуюает30 па. все схемы «И S и открыВа.ет доступ к-ода. в регистпр. После при.хода с выч1И1Сли.т.еля -кОМЗнды «сбр1ос iBce триггеры: регистра / будут нахоДИТЫС.Я ,в .нулево М иоложении, и схема инди-35 ка:то.ра будет под.гото|влена длй зриам-а .еледующей и1Н|форМ1аци;и без сдвига «ода. НО при по|сту1плении знач.ания такого .кода, при. KOTopiOM нео бходим 0 осуществить .сдвиг, возмоя на зан.И1СЬ в регИ1Стр / одно1Вре.мен.но н40 сдвинутого кода. Для устр.аиани.я «на1к.ладки пр Ихадя.щегО без сдвига и сд1В Инутого кодовв индикаторе нреду;Смютрана с.хема. 12 сброса, которая вырабатывает импульс сброса необХ.ОДИМОЙ длительпюсти от .перепада нанряже-45 инЯ, постунаю.щего с шин де.ши(фратор.а 2 через схе.мы «ИЛИ 3, 4 и //. РЬмпльс сброса сбрасы1В,ает с тр.иггерО)В :репиСтра / ищ-формащиио, гюсрушИВШ.ую через схемы «И 8, а К1иф:ормац:ИЯ, 1юстул и:в1ша я со схе:М 5 и 10, будет заииюаша со caiBWDOiM. iB случае необходимости pai6iOTH иеди1катор.а -без сдвига кодов ие1ре«:ДЮчателъ К размъ «ается, тем са-мьвм ютюрывается доступ кода только через схемы «И 8. В и«ди1като1ре тредусмотрен и вы|бо1р rpynin aiBTOiMaiTin4eiOKOM piai6oTU а-индикатора, ЧТ;0 дости;гаетоя выключением переключателей /Са и /Сз. При ручнам управлеиии ищди1катОр01М ис(Польэуются конта1кты К., /Cs, К&. П р е д м е т и з о. б р е т е н и я Дискретный 1М1но1ГО;предельный индикатор, содержащий п-рие.М1НЫй релистр, вынюитненный на триггерах, подключенный IK дешифратору, с1В1Яза1ННО му через транэисторные ключи с индикаторными эламеитами, нереклю1чател1И и лопическме схемы, отличающийся тем, чтО, с целью увеличения то141ности и уменышеиия габаритов, в него введены триггер управления и входны.е р.азрядные ячейки, 1ВЫ1Полненные на схемах «И, нервые входы которЫиХ объедине пы ino грунпам, одно.й из схем «И ячейки г-ого р:азр.яда .под1КЛЮче1Н к единичному входу тр1И1Пгера 1соответ1ствуюшего разряда .приемного. рег«)ст,ра и соеди(Нен с вьаходо1М одной из схем «И я.чейки п.оследующего раз.ряда, а другие входы схем «И Я1Ч.ей1КИ Х-ого р.азряда., (выходы которых объединены, с выхода.ми охе.м «И ячеек предыдушжх г-1 и i-2 раз рядов с.о.от1ветст1В1ан Н;о, о.бъед.И1наны и подключены через сх.емы «И к .выходам триггера унр.авления 1И через схе.му «ИЛИ и инверторы, - к дру1ГИ1м .входам схем «И в.ход.иы.х разрЯ.днььх ячеек, выхо.ды которы-х авязавы .с входа1М1И, .со10Т1В.ет1ств(ую.щих т|р1И1Ггер.О|В приемного регистра; выходы дешифратора, 0|бъединенн.ые в труины, через «ИЛИ и переключатели связаны С |входа;ми триггера нра1В ления и. с шиной сброса в нуль тригге ров пр.ием.лого регистра.

к след, разряду

па о

X

ол

Vt

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU743218A1 |

| Устройство для отображения информации на экране матричного индикатора | 1984 |

|

SU1246130A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Измерительное информационное устройство | 1984 |

|

SU1314360A1 |

| Ячейка однородной структуры | 1990 |

|

SU1789977A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1785076A1 |

| УСТРОЙСТВО для ГЕНЕРАЦИИ п-РАЗРЯДНОГО ТРОИЧНОГО КОДА ПОСТОЯННОГО ВЕСА | 1968 |

|

SU231219A1 |

Авторы

Даты

1973-01-01—Публикация