Предлагаемое устройство представляет собой функциональный аналого-цифровой преобразователь и предназначено для использования в приборостроении,управляющих и информационно-измерительных системах.

Известны аналого-цифровые преобразователи, использующие для реализации нелинейной зависимости дробно-рациональные приближения. Недостатком этих устройств является понижение класса точности по сравнению с линейным аналого- цифровым преобразованием за счет использования прецизионных нелинейных элементов.

Аналогом предлагаемого устройства служит также линейный конвейерный преобразователь. Недостатком этого аналога является невозможность получения функционального преобразования.

Аналогом предлагаемого устройства, в котором устранены недостатки первых двух аналогов, является аналсго-цифропой преобразователь, который выполняет функциональное преобразование напряжения в код с обеспечением нелинейной гиперболической зависимости между кодом и напряжением. Недостатком аналога является алгоритмический способ вычисления нелинейной зависимости, уступающий по быст- родейстсию конвейеру.

оо ел о

VJ

О

л

Наиболее близким к предлагаемому устройству по технической сущности является прототип, который обеспечивает выполнение экспоненциального аналого-цифрового преобразования на основе быстродействующей конвейерной схемы вычисления. Недостатком прототипа является невозможность вычисления гиперболического синуса и косинуса.

Целью изобретения является расширение области применения за счет большей информативности выходных функций (обеспечения формирования выходных сигналов по закону гиперболического синуса и косинуса).

Поставленная цель достигается тем, что в известном устройстве, содержащем сумматор, цифроаналоговый преобразователь, блок вычислений, выполненный в виде последовательно соединенных счетных ячеек на первом регистре, первом сумматоре и триггере каждая, а также счетчик, вход сброса которого соединен со входом сброса регистра и является первой шиной начальной установки, вход счета - соединен со входом записи регистра и является тактирующей шиной, а выход - соединен со входами дешифратора и постоянного запоминающего устройства, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом регистра, а выход - соединен с информационным входом регистра, выход цифроаналогового преобразователя соединен с первым входом компаратора, второй вход которого является входной шиной, выход компаратора соединен с входом управления сумматора и с информационным входом триггеров счетных ячеек, входы синхронизации которых соединены с соответствующими выходами дешифратора, а выход триггера в каждой счетной ячейке соединен со входом установки режима сложение/вычитание первого сумматора данной счетной ячейки, первый информационный вход которого соединен с первым выходом соответствующего первого регистра, входы начальной установки первых регистров всех счетных ячеек объединены и являются второй шиной начальной установки, выход первого сумматора последней счетной ячейки является первой выходной шиной, отличающийся тем, что, с целью расширения области применения за счет обеспечения формирования выходных сигналов по закону гиперболического синуса и косинуса в каждую счетную ячейку введены вторые регистр и сумматор, причем вход начальной установки второго регистра объединен со входом начальной установки первого реги-

стра данной счетной ячейки, вход установки режима сложение/вычитание второго сумматора объединен с одноименным входом первого сумматора данной счетной ячейки,

второй информационный вход которого соединен с первым выходом соответствующего второго регистра с использованием монтажного сдвига, второй выход которого соединен с первым информационным вхо0 дом второго сумматора данной счетной ячейки, второй информационный вход которого соединен с использованием монтажного сдвига со вторым выходом первого регистра данной счетной ячейки, а выход 5 со входом второго регистра последующей счетной ячейки, выход второго сумматора последней счетной ячейки является второй выходной шиной.

Совокупность введенных элементов и

0 связей, построенных по принципу последовательной декомпозиции и конвейерной композиции позволяет осуществить вычисление гиперболического синуса одновременносаналогоцифровым

5 преобразованием. Такой подход к решению поставленной задачи в известных автору устройствах не встречался, из чего следует, что отличия являются существенными.

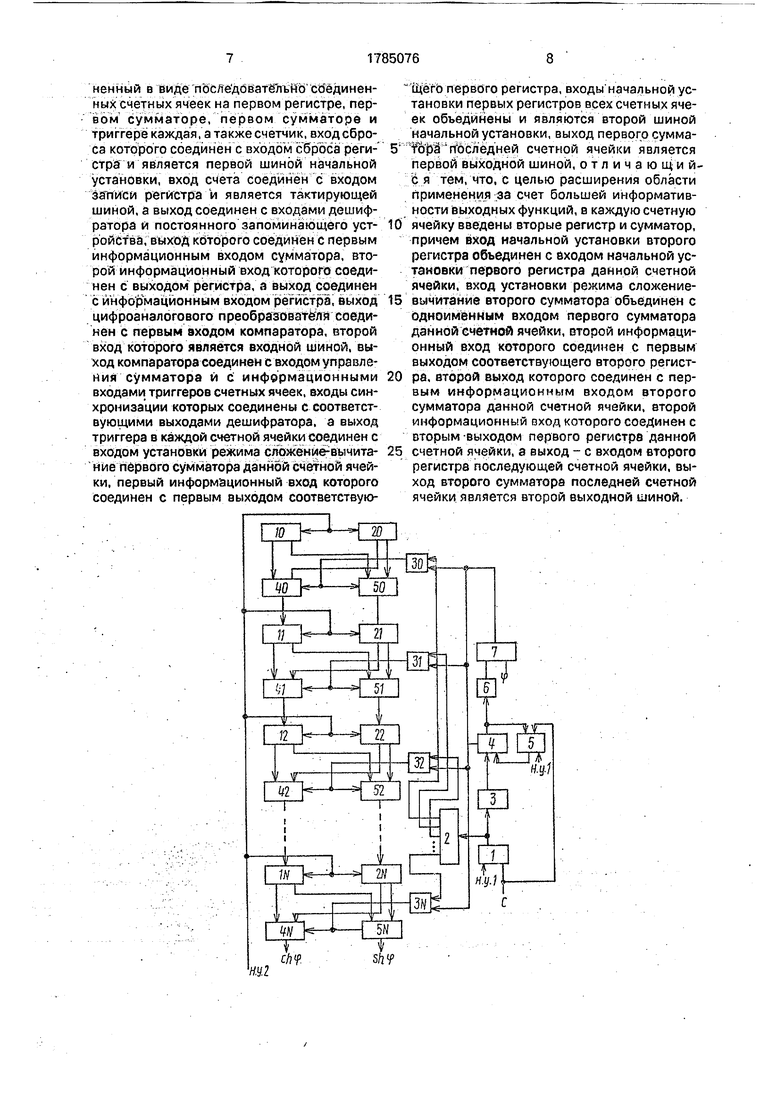

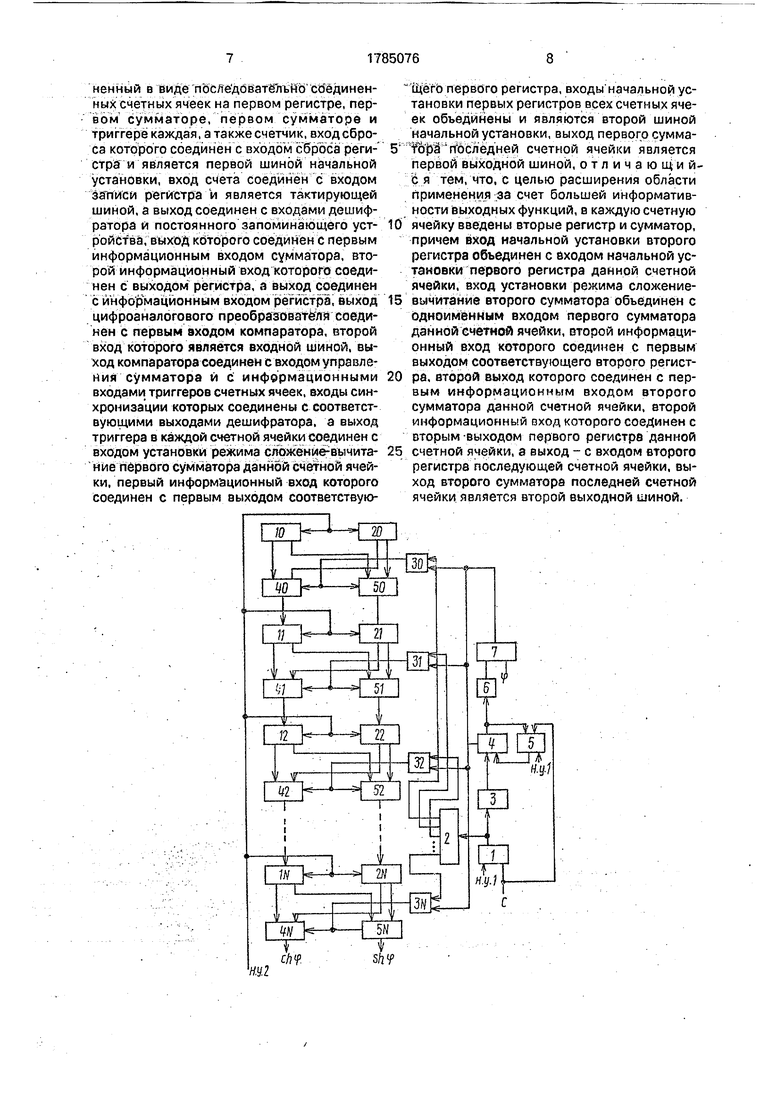

На чертеже представлена схема пред0 латаемого устройства.

Предлагаемое устройство содержит счетчик 1, дешифратор 2, постоянное запоминающее устройство 3, сумматор 4, регистр 5, цифроаналоговый преобразователь

5 6, компаратор 7, первые регистры конвейера 10,11, 121N, вторые регистры конвейера 20, 21, 222IM, триггеры конвейера 30,

31, 323N, первые сумматоры конвейера

40, 41,424N, вторые сумматоры конвейе0 ра 50, 51, 525N, первый вход начального

установа(н.у. 1) соединен со входами сброса счетчика 1 и регистра 5, вход счета счетчика 1 соединен со входом строба записи регистра 5 и соединен со входом тактирующей

5 синхросерии устройства, выход счетчика 1 соединен со входом дешифратора 2 и постоянного запоминающего устройства 3, выход постоянного запоминающего устройства 3 соединен б первым входом сумматора 4,

0 второй вход сумматора 4 соединен с выходом регистра 5, выход сумматора 5 соединен со входами регистра 5 и цифроаналогового преобразователя 6, выход цифроаналогового преобразователя 6

5 соединен с первым входом компаратора 7, второй вход компаратора 7 соединен со входом аргумента устройства, выход компаратора 7 соединен с D-ьходами D-триггеров 30, 31, 33,...,3N и входом управления режимом сложение/вычитание сумматора 4, первый, второй, третий, ,.,,М-ый выходы дешифратора 2 соединены соответственно со входами синхронизации триггеров 30, 31,

323N, выходы триггеров 30, 31, 323N

соединены со входами установки режима сложение/вычитание сумматоров 40, 42, 424N, 50, 51, 525N, второй вход начальной установки (н.у. 2) соединен со входами начальной установки регистров 10,11, 121N, 20. 21, 222N. первый выход регистров 10,11,121N, соединен с первым

входом сумматоров 40, 41, 42,...,4N, второй

выход регистров 10, 11, 121N соединен

со вторым входом сумматоров 50, 51,

525N, первый выход регистров 20, 21,

222N соединен со вторым входом сумматоров 40,41. 424N, выходами устройства

являются выходы сумматоров 4N и 5N.

Устройство работает следующим образом. При поступлении входного сигнала на вход компаратора 7 происходит сравнение этого сигнала с результатом декодирования на цифроаналоговом преобразователе б, декодирующем код, снимаемый с выхода сумматора 4. Сумматор 4 осуществляет сложение начального значения кода, установленного в регистре 5 сбросом сигнала н.у. 1. и значения эталонного гиперболического арктангенса, считываемого из постоянного запоминающего устройства 3. Математически эти действия представляются следующим образом:

-1

02 р -Arth2

Результат сравнения фиксируется в триггере 30 в виде настроечной переменной (.настраивающей первый ярус конвейера на режим сложения или вычитания а сумматорах 40 и 50. Математическое представление уравнений, решаемых в первом ярусе конвейера, имеет следующий вид:

sign Јi sign 0i Јi Ј i yi.

Однакозапуск действий в конвейере не связан с работой аналоговой части преобразователя. Конвейер запускается по сигналу н.у. 2 независимо от запуска н.у. 1. После занесения признака сложение/вычитание в триггер 30 устройство переходит к формированию такого же признака в триггере 31 в соответствии с тактовой частотой С, которая зависит только от частотных характеристик аналоговой части.

Второй такт ввода аналогового сигнала в устройство осуществляется путем инкре- ментации кода в счетчике 1 и выбора следующей эталонной константы из постоянного 5 запоминающего устройства 3. В связи с тем. что алгоритм вычисления гиперболического синуса и косинуса по методу цифра за цифрой предусматривает повторные итерационные шаги, т.е. значения i задаются

0 следующим образом: ,1,2,2,3.3.4.4п1.П-1, на втором такте ввода значения напряжения в аналоговой части преобразователя используется в качестве эталонной константы значение Arth Это

5 обеспечивается тем, что данная эталонная константа, как и все остальные эталонные константы, записана в постоянном запоминающем устройстве дважды. Результат второго такта фиксируется в триггере 31, выбор

0 которого осуществляется по сигналу дешифратора 2.

После того, как заполнены значениями Јi все триггеры - 30.31, 323N, осуществляется запуск конвейера по сигналу н.у. 2.

5 Режим сложение/вычитание в сумматорах 40, 41, 424N, 50, 51, 525N к этому моменту уже установлен и в регистрах конвейера 10, 11, 12, 131N, 20, 21, 22, 232N

формируются последовательные приближе0 ния х и у к искомым значениям гиперболического синуса и косинуса. Вычисления в конвейере обеспечиваются соединением элементов между собой. При этом особенно важно, что перекрестные связи между стол5 бцами конвейера осуществляются со сдвигом разрядов, что позволяет выполнить умножение на 2 без каких-либо аппаратурных затрат. Сдвиг на один разряд, т.е. при означает, что первый разряд выхода со0 единяется со вторым разрядом входа и т.д., сдвиг при (2 означает, что первый разряд выхода соединяется с третьим разрядом входа и т.д. сдвиг при означает, что первый разряд выхода соединяется с четвер5 тым разрядом входа и т.д. Таким образом обеспечивается аппаратный (монтажный, схемный) сдвиг. Количество ярусов в конвейере определяется метрологическими ха- рактеристиками компаратора 7, т.е.

0 количеством достоверных значений, которые можно получить в аналоговой части схемы. Избыточные разряды не повлияют на работоспособность схемы и могут быть использованы для алгоритмической очистки

5 результата от аппаратных погрешностей. Формула изобретения Аналого-цифровой преобразователь, содержащий сумматор, цифроаналоговый преобразователь, блок вычислений, вымолненный в виде посЯе дбватёлъйо со ёдинен- ных счетных ячеек на первом регистре, первом сумматоре, первом сумматоре и триггере каждая, а такжесчетчик, вход сброса которого соединен с входом сброса регистра и является первой шиной начальной установки, вход счета соединен с входом регистра и является тактирующей шиной, а выход соединен с входами дешифратора и постоянного запоминающего уст- ройст ва, выход которого соединён с первым информационным входом сумматора, второй информационный вход которого соединен с выходом регистра, а выход соединен с инфо рмацйонным входом регистра выход цифроаналогового преобразователя соединен с первым входом компаратора, второй вход которого является входной шиной, выход компаратора соединен с входом управления сумматора и с информационными входами триггеров счетных ячеек, входы синхронизации которых соединены с соответствующими выходами дешифратора, а выход триггера в каждой счетной ячейки соединен с входом установки режима слрженйё-вычита- нйе первого сумматора данной счетной ячейки/первый информационный вход которого соединен с первым выходом соответствую

щёго первого регистра, входы начальной установки первых регистров всех счетных ячеек объединены и являются второй шиной начальной установки, выход первого сумма fb plлпоследней счетной ячейки является первой выходной шиной, отличаю щ- и й- rd я тем, что, с целью расширения области применения за счет большей информативности выходных функций, в каждую счетную ячейку введены вторые регистр и сумматор, причем вход начальной установки второго регистра объединен с входом начальной установки первого регистра данной счетной ячейки, вход установки режима сложение- вычитание второго сумматора объединен с одноимённым входом первого сумматора данной счетной ячейки, второй информационный вход которого соединен с первым выходом соответствующего второго регистра, второй выход которого соединен с первым информационным входом второго сумматора данной счетной ячейки, второй информационный вход которого соединен с вторым -выходом первого регистра данной счетной ячейки, а выход - с входом второго регистра последующей счетной ячейки, выход второго сумматора последней счетной ячейки является второй выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1989 |

|

SU1686697A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809531A1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809532A1 |

| Тригонометрический конвейерный преобразователь | 1989 |

|

SU1651300A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1520659A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

Аналого-цифровой преобразователь предназначен для использования в качестве функционального преобразователя для ввода аналогового сигнала в измерительно- вычислительный комплекс. Устройство может найти применение в приборостроении, управляющих и информационно-измерительных системах. В устройстве решается задача расширения области применения функциональных преобразователей. Для решения поставленной задачи в устройство, содержащее счетчик, дешифратор, сумматор, цифроаналоговый преобразователь, постоянное запоминающее устройство, регистр, компаратор и блок вычисления, выполненный в виде счетных ячеек на первом регистре, первом сумматоре и триггере каждая, в каждую счетную ячейку введены вторые регистр и сумматор и организованы соответствующие связи между элементами устройства. Совокупность введенных элементов и связей, построенных по принципу последовательной декомпозиции и конвейерной композиции, позволяет осуществить наряду с аналого-цифровым преобразованием вычисление гиперболического синуса и косинуса 1 ил. (Л С

| Анисимов А.В | |||

| и др | |||

| Аналоговые и гибридные вычислительные машины | |||

| М.: Высшая школа, 1984, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1686697A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-30—Публикация

1990-11-26—Подача