1

Изобретение относится к электросвязи, а именно, к передаче данных методоц амплитудно-фазовой модуляции.

Известно устройство синхронизации по циклам содержащие объединенные по входу приемный регистр и регистр сдвига, выходы которого подключены ко входам блока дешифратора, а также распределитель импульсов flj .

Однако при использовании укороченных кодов и при высокоскоростной передаче информации с применением амплитудно-фазовой модуляции, в случае j 6ратной работы известное устройство оказывается малоэффективным и характеризуется большим временем вхождения в синхронизм.

Цель изобретения - уменьшение времени вхождения в синхронизм.

Это достигается тем, что в устройство синхронизации по циклам, содержащее объединенные по входу приемный регистр и регистр сдвига, выходы которого подключены ко входам блока дешифратоjpa, а распределитель импульсов, введены последовательно соединенные блок зашиты от ошибок, блок сброса, триггер и элемент И, другой вход которого соединен с выходом приемного регистра, а выход - со вторым входом регистра сдвига, причем, другие выходы блока сброса соединены соответственно с другим входом приемного регистра, с третьим входом регистра сдвига и входом распределителя импульсов, выход которого подключен к другому входу блока защиты от ошибок, при этом на угие входы триггера и блока сброса подан сигнал начало фазировки,

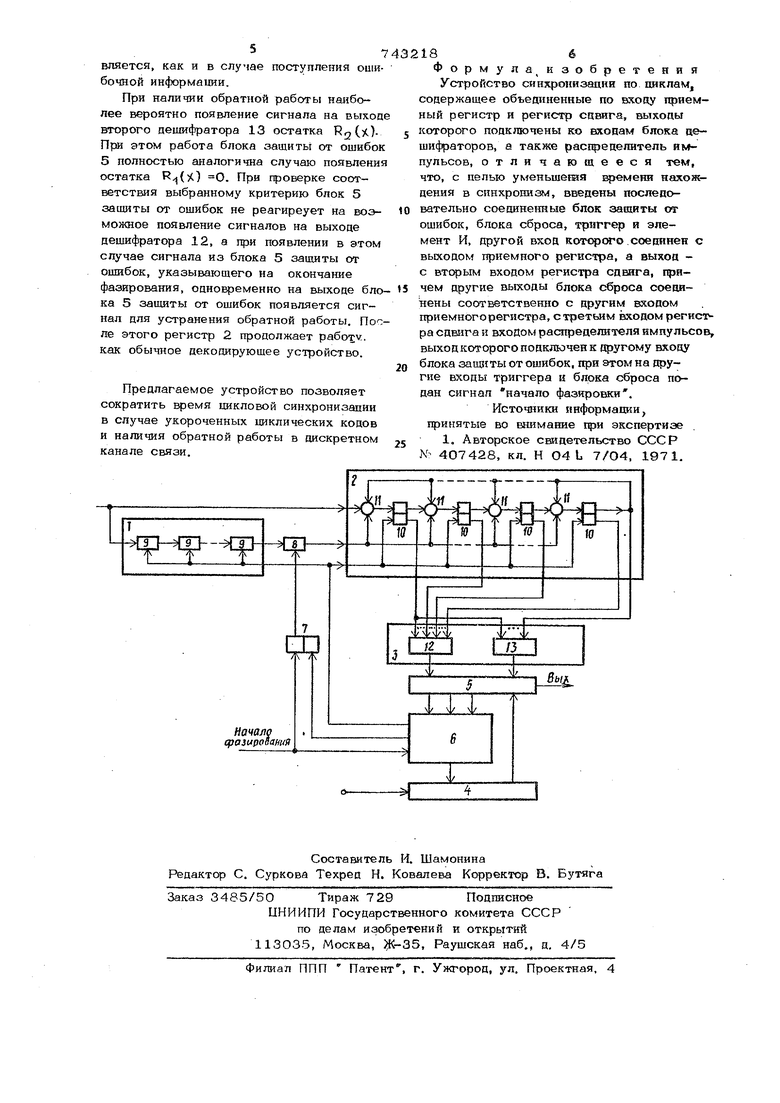

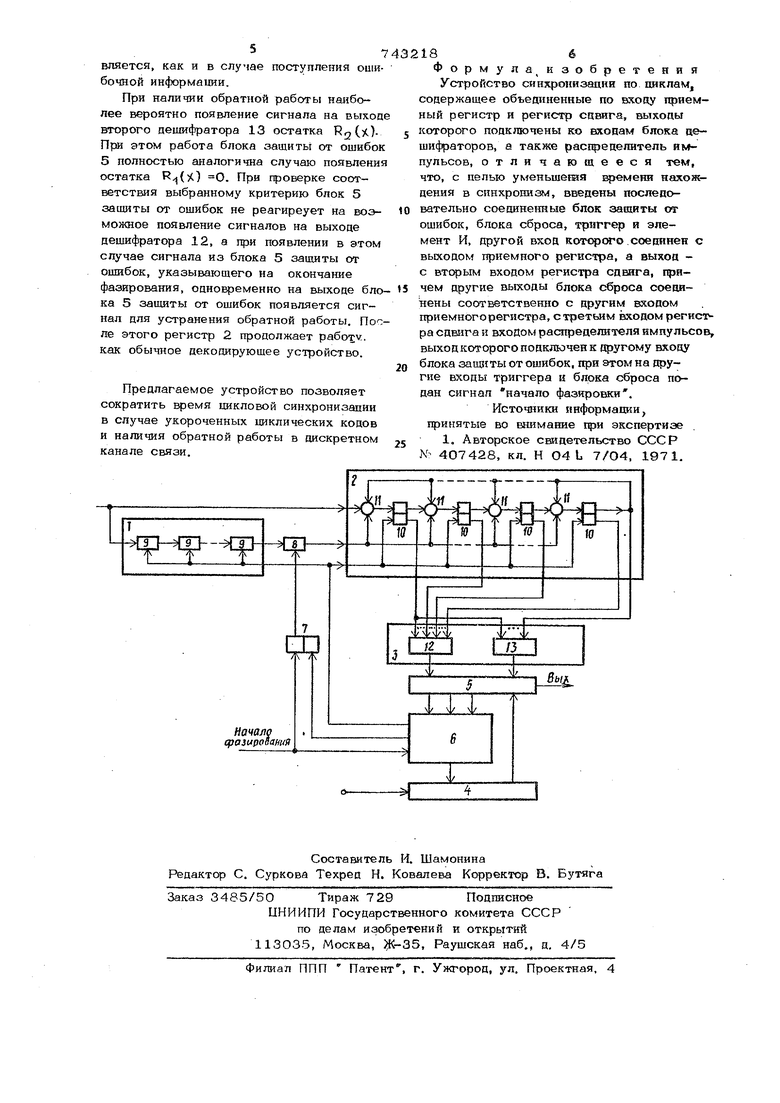

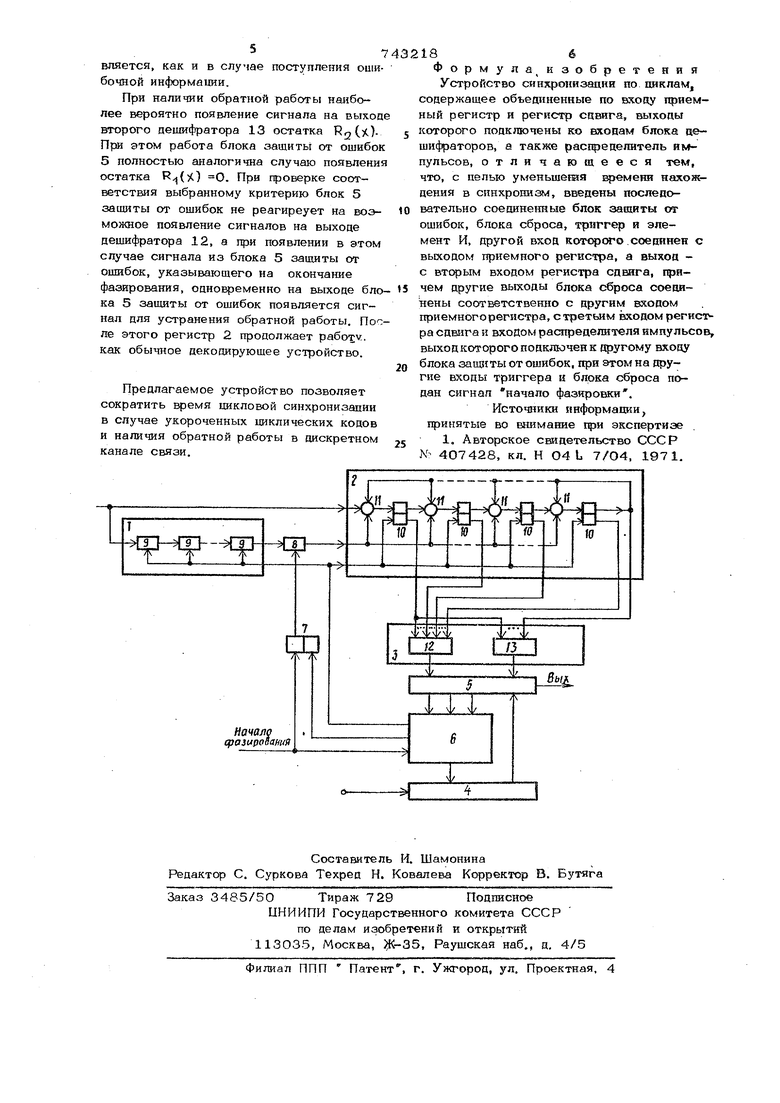

На чертеже представлена блок-схема устройства синхронизации по циклам.

Устройство содержит объединенные по входу приемный регистр 1 и регистр 2 сдвига, Ьлок с дешифраторов и распределителей 4 импульсов. Выходы регистра 2 сдвига кодключены ко входам блока 3 дешифраторов. Устройство содержит, также последовательно соединенные блок 5 защиты от ошибок, блок 6 сброса, тригг ер 7 и ваемент И 8. Другой вход элемента И 8 соепинен с выходом приемного регистра 1, а выход - со вторым входом регистра 2 сдвига. Другие выходы блока 6 сброса соединены соответственно с другим входом приемного регистра 1, с тр тьим входом регистра 2 сдвига и входом распределителя 4 импульсов. Выход распределителя 4 импульсов подк лючен к другому входу блока 5 защиты, причем на другие входы триггера 7 и бл ка 6 сброса подан сигнал начало фазировки. Приемный регистр 1 состоит из яче ек 9 памяти, число которых равно длине кодовой комбинаююи. -; Регистр 2 состоит из последовательно соединенных ячеек 10 памяти по шслу проверочных разрядов кода и сумматоров 11 по модулю 2. Количество сумматоров зависит от числа о ратных связей в регистре 2 сдвига и шcлa связей с шиной вычитания от вы- .ходной ячейки приемного регистра 1 через элемент И 8 с ячейками 10 памяти регистра 2 сдвига. Нулевые выходы всех ячеек 10 памяти регистра 2 сдвига сбязаны со входами первого дешифратора 12 блока 3 дешифраторов. Нулевые или единичные выходы всех ячеек 10 памяти регистр а 2 сдвига связаны со входами второго дешифратора 13. Ха эактер связей с дешифратором 13 определяется в соответствии с результатом дво ичного деления комбинации Y (х), состоящей из одних единиц, на образующий многочлен Р(х). Выходы дешифраторов 12 и 13 через блок 5 защиты связаны с блоком 6 сбро который связан с установочными входами ячеек 9 и 1О памяти регистров 1 и 2 с установочным входом расппеде-. лителя 4 импульсов и нулевым установочным входом триггера 7. Входная шина сигнала начало фазирования подключена к блоку 6 сброса и единичному установочному входу триггера 7, еди шчный выход которого связан со вторым входом элемента И 8. Входная шина тактовых импульсов подключена к распределителю импульсов 4. Устройство работает следующим образом. При потере синхронизации устройство переходит в режим фазирования и сигнал начало фазировки через блок 6 сброса устанавливает в исходное состоя ние распределитель 4 импульсов и ячейки 9 и 10 памяти, регистров 1 и 2. Этим же сигналом включается триггер 7, и выход приемного регистра 1 через элв-- мент И 8 подключается к шине вычитания регистра 2. После л -го такта в приемном регистре 1 накапливается hразрядная комбинация, а блок 5 защиты от ошибок подготавливается к восприятию сигналов с дешифраторов 12 и 13. Начиная с (h+1) такта в каждом такте происходит следующее. Очередной разряд поступает в регистры 1 и 2. В регистре 2 производится сдвиг хранящегося в Ячейках 1О памяти остатка от деле- ., ния комбинации, находящейся в ячейках 9 памяти приемного регистра 1. В регистр 2 добавляется принятый разряд и осуществляется деление на образующий многочлен. В приемном регистре 1 производится сдвиг, стирание разряда последней ячейки 9 и вычитание из содеряшмого регистра 2 остатка от деления стираемого разряда на образующий многочлен. Таким образом, после каждого . такта в сдвигающем регистре 2 находит ся остаток от деления нового содержимого гфиемного регистра 1 на образующий многочлен Р(х). При отсутствии ошибок в поступающей информации синхронное положение должно быть найдено не более чем за (2h-l) такта. Если это время будет превышено, сигнал из блока 5 заишты от ошибок через блок 6 сброса устанавливает приемный и сдвигающий регистры 1, 2 и распределитель 4 импульсов в исходное состояние и поиск синхронного положения возобновляется. Если обратной работы нет, то при первом появлении сигнала на выходе дешифратора 12 сигнал из блока 5 зацщты от ошибок по соответствующей цепи через блок 6 сброса устанавливает в исходное положение распределитель 4 импульсов. После этого блок 5 защиты от ошибок реагирует только на сигналы с дешифратора 12, появляющиеся через h тактов. Если частота появления остатка RJ (х) 0 соответствует выбранному критерию, то сигнал из блока 5 защиты от ошибок через блок 6 сброса формирует сигнал конец фазировки, по которому триггер 7 выключается и связь приемного регистра 1 с шиной вычитания сдвигающего регистра 2 прерывается, после чего регистр 2 продолжает работу как обычное декодирующее устройство. Если выбранный критерий защиты не удовлетворяется, тг поиск синхронного положения возобновляется, как и в случае поступления оши бочной информации. При наличии обратной работы наиболее вероятно появление сигнала на выход второго дешифратора 13 остатка Rg ()(.) При этом работа блока защиты от ошибок 5 полностью аналогична случаю ноявлени остатка R()() 0. При проверке соответствия выбранному критерию блок 5 защиты от ошибок не реагиреует на воэможное появление сигналов на выходе дешифратора 12, а при появлении в этом случае сигнала из блока 5 защиты от ошибок, указывающего на окончание фазирования, одновременно на выходе бло ка 5 зашиты от ошибок появляется сигнал для устранения обратной работы. Пос ле этого регистр 2 продолжает работу, как обычное декодирующее устройство. Предлагаемое устройство позволяет сократить время цикловой синхронизации в случае укороченных циклических кодов и наличия обратной работы в дискретном канале связи. к зобретени я Устройство синхронизации по циклам, содержащее объединенные по входу приемный регистр и регистр сцвига, выходы которого подключены ко входам блока дешифраторов, а также распределитель импульсов, отличающееся тем, что, с целью уменьшешз времени HBXOSRдения в синхронизм, введены последовательно соединенные блок защиты от ошибок, блока сброса, триггер и элемент И, другой вход котсрсго соединен с вьсходом приемного регистра, а выход с вторык входом регистра сдвига, 1 ичем другие выходы блока сброса соединены соответственно с другим входом приемного регистра, с третьим входом регистра сдвига и входом распределителя импульсов, выход которого подключен к {фугому входу блока зашлты от ошибок, при этом на другие входы триггера и блока сброса подан сигнал начало фазировки. Источники информации, принятые во внимание при экспертизе 1. Авторское СЕЯдетельство СССР N. 4О7428, кл. Н О4 Ь 7/О4, 1971.

Начало (pajupoSaffua

Bbif

Ёщ.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1987 |

|

SU1515382A2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ КАНОНИЧЕСКОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, СФОРМИРОВАННОЙ МОДУЛЬНЫМ ГЕНЕРАТОРОМ | 2024 |

|

RU2831303C1 |

| Устройство определения конца блока циклического кода | 1987 |

|

SU1515381A2 |

| Устройство определения конца блока циклического кода | 1986 |

|

SU1401631A2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство синхронизации | 1988 |

|

SU1631738A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Приемное устройство цикловой синхронизации | 1976 |

|

SU578670A1 |

Авторы

Даты

1980-06-25—Публикация

1977-12-29—Подача