Изобретение относится к цифровой вычислительной технике и предназначено для использования в однородных вычислительных структурах, для реализации нечетких алгоритмов.

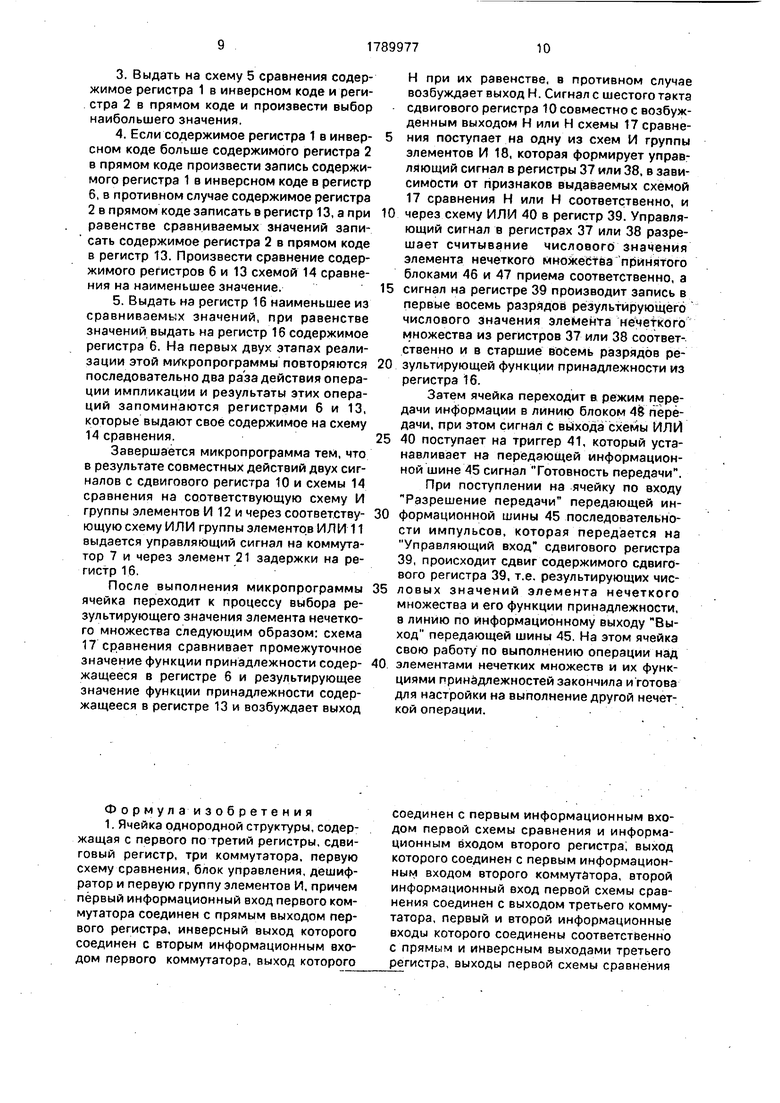

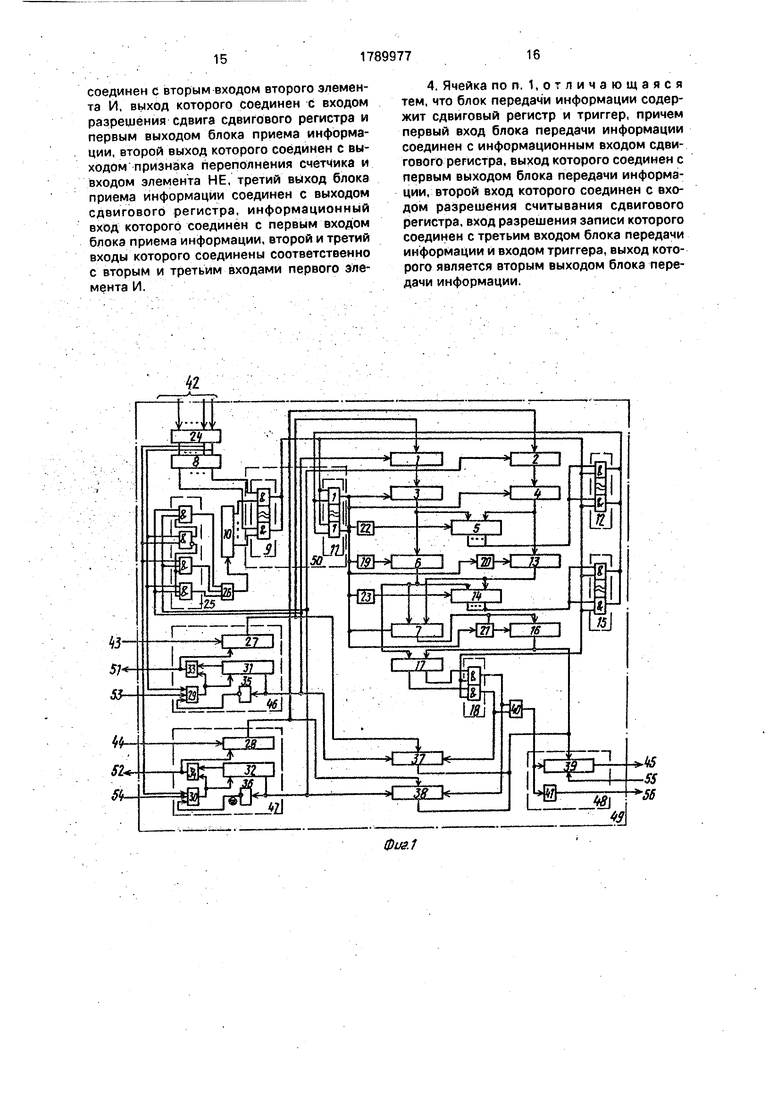

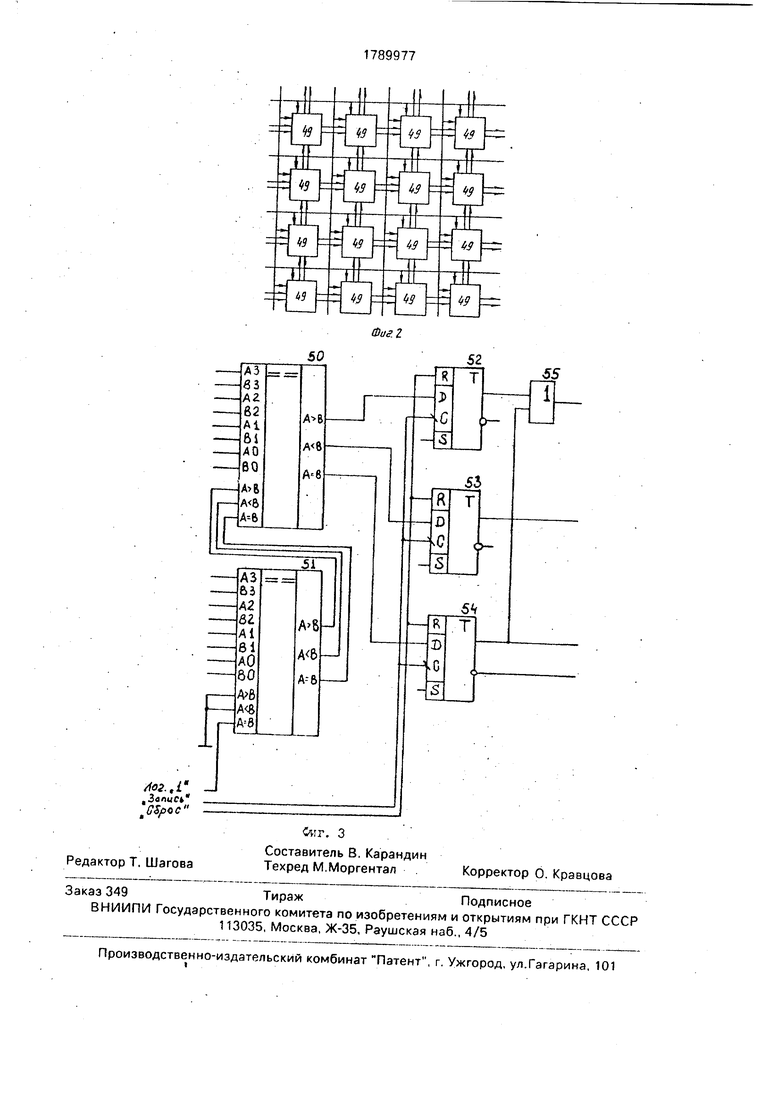

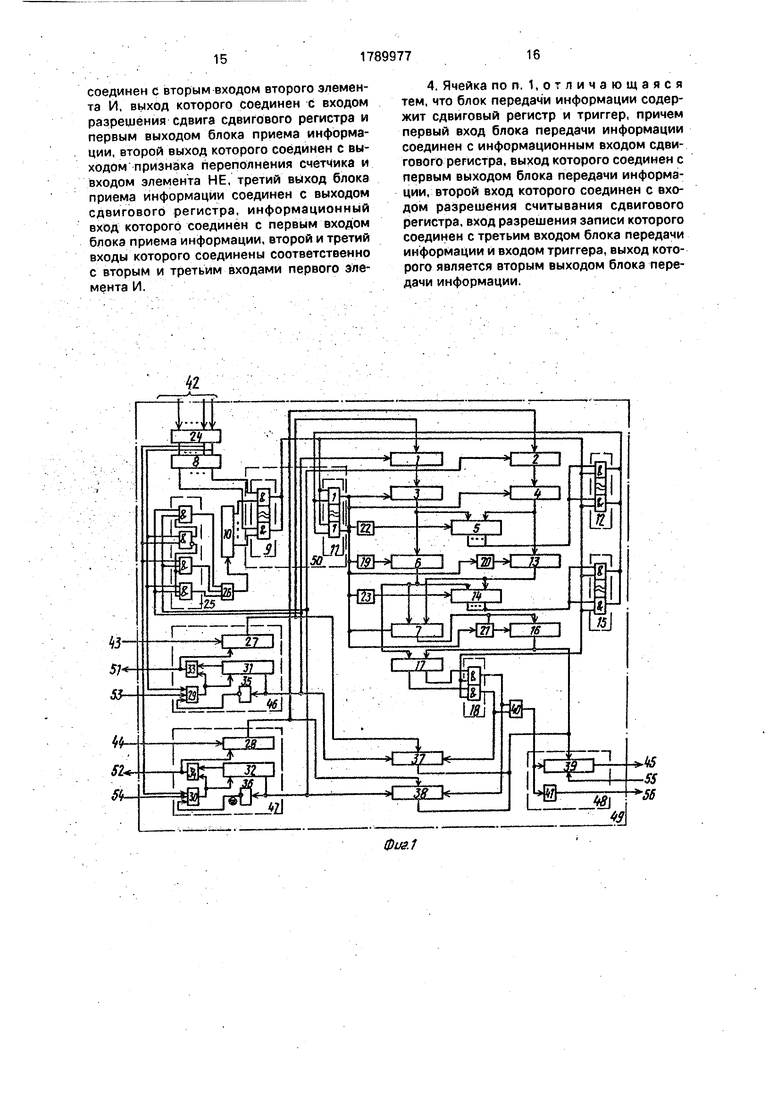

На фиг. 1 показана функциональная схема ячейки однородной структуры; на фиг. 2 - часть однородной структуры, состоящая из ячеек; на фиг. 3 - схема одного из возможных вариантов реализации схемы сравнения.

Ячейка содержит (фиг. 1) регистр 1. регистр 2. коммутатор 3, коммутатор 4, схему 5 сравнения, регистр 6, коммутатор 7, дешифратор 8, группу элементов И 9, сдвиговый регистр 10, группу элементов ИЛИ 11, группу элементов И 12, регистр 13, схему 14 сравнения, группу элементов И 15, регистр

16, схему 17 сравнения, группу элементов И 18, элемент 19 задержки, элемент 20 задержки, элемент 21 задержки, элемент 22 задержки, элемент 23 задержки, регистр 24, группу элементов И 25. элемент ИЛИ 26, сдвиговый регистр 27, сдвиговый регистр 28, элемент И 29. элемент И 30, счетчик 31, счетчик 32. элемент И 33, элемент И 34, инвертор 35, инвертор 36, регистр 37 с тремя состояниями на выходе, регистр 38 с тремя состояниями на выходе, сдвиговый регистр 39, элемент ИЛИ 40, триггер 41, управляющие входы 42, информационные входы 43, информационные входы 44, информационные выходы 45, блок 46 приема, блок 47 приема, блок 48 передачи. Ячейки объединяются в однородную структуру, как показано на фиг. 2..

VI 00

чэ о VI VI

Выходы прямого кода регистров 1 и 2 соединены с первыми группами информационных входов коммутаторов 3 и А, выходы инверсного кода регистров 1 и 2 соединены с вторыми группами информационных входов коммутаторов 3 и 4 соответственно. Выходы коммутатора 3 соединены с первой группой входов схемы 5 сравнения и с информационными входами регистра б соот- ветственнр,7 выходы коммутатора 4 соединены с, второй группой входов схемы 5 сравненйя оответственно, выходы регистра 6 соединены с первой группой входов коммутатора 7 соответственно, выходы дешифратора 8 соединены с соответствующими первыми входами элементов И группы элементов И 9, вторые входы которых соединены с соответствующими выходами сдвигового регистра 10, выходы элементов И группы элементов И 9 соединены с соответствующими входами элементов ИЛИ. группы элементов ИЛИ 11, выходы схемы 5 сравнения соединены с соответствующими первыми входами элементов И группы элементов И 12. Причем информационные входы регистра 13 соединены с выходами коммутатора 4 соответственно, выходы регистра 13 соединены с второй группой информационных входов коммутатора 7 и с второй группой входов схемы 14 сравнения соответственно, первая группа входов которой соединена с выходами регистра б соответственно, выходы схемы 14 сравнения соединены с соответствующими первыми входами элементов И группы элементов И 15, выходы коммутатора 7 соединены с информационными входами регистра 16 соответственно, выходы регистра 16 соединены с второй группой входов схемы 17 сравнения соответственно, первая группа входов которой соединена с выходами регистра б соответственно, выходы схемы 17 сравнения соединены с соответствующими первыми входами элементов И группы элементов И 18, вторые входы элементов И которой соединены с соответствующими выходами элементов И группы элементов И 9, выходы элементов И групп элементов И 12 и 15, вторые входы которых соединены с выходами соответствующих элементов И группы элементов И 9, соединены с соответствующими вторыми входами элементов ИЛИ группы элементов ИЛИ 11, выходы соответствующих элементов ИЛИ которой соединены с управляющими входами коммутаторов 3, 4 и 7 и через элементы 19, 20 и 21 задержки с регистрами б, 13 и 16 соответственно. Кроме того выходы соответствующих элементов ИЛИ группы элементов ИЛИ 11 соединены через элементы 22 и 23 задержки с

управляющими входами схем 5 и 14 сравнения соответственно. Выходы регистра 24 соединены с входами дешифратора 8 соответственно, кроме того первый выход регистра 24 соединен с первыми входами второго и четвертого элементов И, а второй выход регистра 24 соединен с вторым входом второго элемента И и с первым входом третьего элемента И группы элементов И 25,

0 Кроме того прямой выход второго элемента И группы элементов И 25 соединен с третьим входом первого элемента И, инверсный выход второго элемента И соединен с третьими входами третьего и четвертого элемен5 тов И соответственно, выходы первого, третьего и четвертого элементов И группы элементов И 25 соединены с входами элемента ИЛИ 26 соответственно, выход которого соединен с управляющим входом

0 регистра сдвига 10. Восемь старших разрядов группы выходов регистров сдвига 27 и 28 соединены с информационными входами регистров 1 и 2 соответственно, первые входы элементов И 29 и 30 соединены с первым

5 и вторым выходами регистра 24 соответственно, выходы элементов И 29 и 30 соединены с управляющими входами счетчикой 31 и 32 соответственно и с вторыми входам элементов И 33 и 34 соответственно, первый

0 входы которых соединены с счетными входами счетчиков 31 и 32 соответственно, выходы элементов И 33 и 34 соединены с управляющими входами сдвиговых регистров 27 и 28 соответственно, третьи входи

5 элементов И 29 и 30 соединены через инверторы 35 и 36 соответственно с выходами счетчиков 31 и 32 соответственно, причем выход счетчика 31 соединен с первым входом первого элемента И и с вторым входбМ

0 четвертого элемента И группы элементов И 25, с управляющим входом регистра 1 и с первым управляющим входом регистра 37 с тремя состояниями на выходе, выход счетчика 32 соединен с вторым входом первого

5 элемента И и с вторым входом третьего.элемента И группы элементов И 25, с управляющим входом регистра 2 и с первым управляющим i -входом регистра 38 с тремя состояниями на выходе. Информационные

0 входы регистра 37 соединены с младшими

восемью разрядами группы выходов регист. ра сдвига 27 соответственно, информационные входы регистра 38 соединены с

младшими восемью разрядами группы вы.5 ходов регистра сдвига 28 соответственно Причем выходы регистров 37 и 38 соединены с восемью младшими разрядами группы информационных входов сдвигового регистра 39 соответственно, старшие восемь разрядов группы информационных входов

которого соединеныс выходами регистра 16 соответственно, выходы элементов И группы элементов И 18 соединены с вторыми управляющими входами регистров 37 и 38 соответственно и с соответствующими входами элемента ИЛИ 40, выход элемента ИЛИ 40 соединен с первым управляющим входом сдвигового регистра 39 и с входом триггера 41. Кроме того информационные и управляющие входы регистра 24 соединены с управляющими входами 42 ячейки. Информационный вход регистра сдвига 27 соединен с информационным входом Вход, второй вход элемента И 29 соединен с управляющим входом Готовность передачи, а выход элемента И 33 соединен с управляющим выходом Разрешение передачи приемной информационной шины 43 ячейки. Информационный вход регистра сдвига 28 соединен с информационным входом Вход, второй вход элемента И 30 соединен с управляющим входом Готовность передачи, а выход элемента И 34 соединен с управляющим выходом Разрешение передачи приемной информационной шины 44 ячейки. Информационный выход сдвигового регистра 37 соединен с информационным выходом Выход, выход триггера 41 соединен с управляющим выходом Готовность передачи, а второй управляющий .вход сдвигового регистра 39 соединен с управляющим входом Разрешение передачи передающей информационной шины 45, Кроме того сдвиговый регистр 27, элемент И 29, счетчик 31, элемент И 33 и инвертор 35 объединены в блок 46 приема, входы которого соединены с приемной информационной шиной 43. Сдвиговый регистр 28, элемент И 30, счетчик 32, элемент И 34 и инвертор 36 объединены в блок 47 приема. входы которого соединены с приемной информационной шиной 44. Сдвиговый регистр 39 и триггер 41 объединены в блок 48 передачи, выходы которого соединены с передающей информационной шиной 45 ячейки.

Ячейка предназначена для реализации микропрограмм обработки числовых значений элементов нечетких множеств и их функций принадлежностей и для образования однородной структуры, позволяющей реализовать полные нечеткие алгоритмы.

Ячейка однородной структуры работает следующим образом.

В начале работы необходимо установить в нулевое состояние все регистры, счетчики и триггеры, что осуществляется с помощью единичного потенциала; который формирует дешифратор 8 (фиг. 1), по коду сброса, поступающего по шине настройки

42 в регистр 24 и далее на вход дешифратора 8.

Настройка ячейки на выполнение конкретной операции производится по коду, по- 5 ступающему по шине настройки 42 в регистр 24, а затем на дешифратор 8 и кроме того сигналы с первого и второго выходов регистра 24 поступают на схемы И 29 и 30 блоков 46 и 47 приема соответственно, ко10 торые подключают в зависимости от выполняемой операции необходимые приемные информационные шины к ячейке. Кроме того, сигналы с первого и второго выходов регистра 24 поступают на схемы И группы

5 элементов И 25, которая, совместно с схемой ИЛИ 26, осуществляет синхронный запуск сдвигового регистра 10 по получении сигналов управления с заданных блоков приема, сообщающих о приеме необходи0 мой информации для выполнения операции. По окончании настройки ячейка переходит в режим приема, который состоит как из ожидания приема информации, так и из самого приема информации по приемным ин5 формационным шинам блоками приема. Во время режима приема происходит прием числовых значений элементов нечетких множеств А и В и их функций принадлежно- стей т(а) и т(о) по приемным информацион0 ным шинам 43 и 44 в сдвиговые регистры 27 и 28 блоков 46 и 47 приема соответственно. Прием информации, например блоком 46 приема, происходит следующим образом: с первого разряда регистра 24 на схему

5 И 29 поступает сигнал подключения приемной информационной шины 43 на вход блока 46 приема ячейки, одновременно на схему И 29 поступает сигнал с выхода счетчика 31 через инвертор 35, который сообща0 ет, что регистр сдвига 27 свободен для получения информации. Блок 46 приема готов к приему информации.

При подаче на приемную информационную шину 43 сигнала Готовность переда5 чии, он поступает на вход схемы И 29, которая выдает сигнал на второй вход схемы И 33 и одновременно производит запуск счетчика 31, причем на первый вход схемы И 33 подается счетный сигнал со входа счет0 чика 31. На выходе схемы И 33 получаем последовательность тактовых сигналов,.которая подается на сдвиговый регистр 27 и выход Разрешение передачи приемной шины 43. Тактовые сигналы производят

5 сдвиг информации поступающей по информационному входу Вход приемной шины 43 в сдвиговый регистр 27.

При заполнении всех шестнадцати разрядов сдвигового регистра 27 счетчик 31 на выходе выдает сигнал, который через инвертор 35 поступает на схему И 29, на выходе которой снимается сигнал управления с счетчика 31 и с второго входа схемы И 33, в результате чего прекращается выдача тактовых сигналов сдвига на сдвиговый ре- гистр 27 и на выход Разрешение передачи приемной шины 43, на этом прием информации блоком 46 приема прекращается.

Кроме того сигнал с выхода счетчика 31 поступает на управляющие входы Запись регистров 1 и 37, по которому происходит запись содержимого первых восьми разрядов регистра сдвига 27, содержащих числовое значение элемента нечеткого множества А, в регистр 37 с тремя состояниями на выходе и запись содержимого восьми старших разрядов, содержащих числовое значение функции принадлежности т(а) элемента нечеткого множества А, в регистр

1. Выход счетчика 31 также соединен с со- ответствующими входами схем И группы элементов И 25.

Прием информации блоком 47 приема, блок 47 приема по составу и функционированию аналогичен блоку 46 приема, проис- ходит аналогично: информация поступает по информационному входу Вход приемной шины 44 в сдвиговый регистр 28, в по сигналу с выхода счетчика 32 происходит запись содержимого первых восьми разря- дов сдвигового регистра 28, содержащих .числовое значение элемента нечеткого множества В, в регистр 38 с тремя состояниями на выходе и запись содержимого восьми старших разрядов, содержащих числовое значение функции принадлежности m(b) элемента нечеткого множества В, в регистр

2. Выход счетчика 32 также соединен с соответствующими входами схем И группы элементов И 25,

При поступлении на соответствующие входы схем И группы элементов И 25 сигналов как с выхода счетчика 31 блока 46 приема, так и с выхода счетчика 32, блока 47 приема, соответствующая схема И выдает сигнал на один из входов схемы ИЛИ 26, При поступлении этого сигнала схема ИЛИ 26 выдает сигнал управления на сдвиговый регистр 10, по которому сдвиговый регистр 10 начинает формировать тактовые сигналы для синхронизации работы элементов ячейки.

: При этом в ячейке начинается процесс реализации микропрограмм.

Микропрограммы операции чтения и инверсии наиболее простые и завершаются выдачей на сдвиговый регистр 39 в прямом и инверсном коде соответственно содержимого регистров 1 или 2 и в прямом коде содержимого регистров 37 или 38 соответственно в зависимости от задействованного блока приема информации,

Микропрограммы операций конъюнкции, дизъюнкции, импликации и ассоциативного поиска очень близки между собой и выполняются за одинаковое количество микротактов..

Микропрограмма операции дизъюнкции (конъюнкции).

1. Выдать на регистры 6 и 13 содержимого регистров 1 и 2 соответственно и произвести сравнение содержимого регистров 6 и 13.

2. Выдать на регистр 16 наибольшее (наименьшее) из сравниваемых значений, при равенстве значений выдать, на регистр 16 содержимое регистра 6.

Микропрограмма операции импликации.

1. Выдать на регистр 6 содержимого регистра 1 в прямом или инверсном коде, а на регистр 13 содержимого регистра 2 в инверсном или прямом коде соответственно и произвести сравнение содержимого регистров 6 и 13.

2. Выдать на регистр 16 наибольшее из сравниваемых значений, при равенстве значений выдать на регистр 16 содержимое регистра 6.

При реализации этих микропрограмм на первом такте сдвигового регистра 10 с помрщью коммутаторов 3 и 4 осуществляется выдача на регистры 6 и 13 и на схему 14 сравнения содержимого регистров 1 и 2 в прямом, инверсном, прямом и инверсном или инверсном и прямом кодах соответственно.

Следующий такт сдвигового регистра 10 совместно с выходными сигналами схемы 14 сравнения формирует управляющий сигнал, по которому осуществляется подключение выходов регистров 6 или 13 через коммутатор 7 к входам регистра 16 и запись содержимого регистров 6 или 13 соответственно в регистр 16.л

Микропрограмма операции эквивалентность.

1. Выдать на схему 5 сравнений содержимое регистра 1 в прямом коде и регистра 2 в инверсном коде и произвести выбор наибольшего значения.

2. Если содержимое регистра 1 в прямом коде больше содержимого регистра 2 в инверсном коде произвести запись содержимого регистра 1 в прямом коде в регистр 6, в противном случае содержимое регистра 2 в инверсном коде записать в регистр 13, а при равенстве сравниваемых значений записать содержимое регистра 1 в прямом коде в регистр 6.

3. Выдать на схему 5 сравнения содержимое регистра 1 в инверсном коде и регистра 2 в прямом коде и произвести выбор наибольшего значения.

4. Если содержимое регистра 1 в инверсном коде больше содержимого регистра 2 в прямом коде произвести запись содержимого регистра 1 в инверсном коде в регистр 6, в противном случае содержимое регистра 2 в прямом коде записать в регистр 13, а при равенстве сравниваемых значений записать содержимое регистра 2 в прямом коде в регистр 13. Произвести сравнение содержимого регистров 6 и 13 схемой 14 сравнения на наименьшее значение.

5. Выдать на регистр 16 наименьшее из сравниваемых значений, при равенстве значений выдать на регистр 16 содержимое регистра 6. На первых двух этапах реализации этой микропрограммы повторяются последовательно два раза действия операции импликации и результаты этих операций запоминаются регистрами 6 и 13, которые выдают свое содержимое на схему 14 сравнения.

Завершается микропрограмма тем, что в результате совместных действий двух сигналов с сдвигового регистра 10 и схемы 14 сравнения на соответствующую схему И группы элементов И 12 и через соответствующую схему ИЛИ группы элементов ИЛИ 11 выдается управляющий сигнал на коммутатор 7 и через элемент 21 задержки на регистр 16.

После выполнения микропрограммы ячейка переходит к процессу выбора результирующего значения элемента нечеткого множества следующим образом: схема 17 сравнения сравнивает промежуточное значение функции принадлежности содержащееся в регистре 6 и результирующее значение функции принадлежности содержащееся в регистре 13 и возбуждает выход

Н при их равенстве, в противном случае возбуждает выход Н. Сигнал с шестого такта сдвигового регистра 10 совместно с возбужденным выходом Н или Н схемы 17 сравне- 5 ния поступает на одну из схем И группы элементов И 18, которая формирует управляющий сигнал в регистры 37 или 38, в зависимости от признаков выдаваемых схемой 17 сравнения Н или Н соответственно, и

0 через схему ИЛИ 40 в регистр 39. Управляющий сигнал в регистрах 37 или 38 разрешает считывание числового значения элемента нечеткого множества принятого блоками 46 и 47 приема соответственно, а

5 сигнал на регистре 39 производит запись в первые восемь разрядов результирующего числового значения элемента нечеткого множества из регистров 37 или 38 соответственно и в старшие восемь разрядов ре0 зультирующей функции принадлежности из регистра 16.

Затем ячейка переходит в режим передачи информации в линию блоком 48 передачи, при этом сигнал с выхода схемы ИЛИ

5 40 поступает на триггер 41, который устанавливает на передающей информационной шине 45 сигнал Готовность передачи. При поступлении на ячейку по входу Разрешение передачи передающей ин0 формационной шины 45 последовательности импульсов, которая передается на Управляющий вход сдвигового регистра 39, происходит сдвиг содержимого сдвигового регистра 39, т.е. результирующих чис5 ловых значений элемента нечеткого множества и его функции принадлежности, в линию по Информационному выходу Выход передающей шины 45. На этом ячейка свою работу по выполнению операции над

0 элементами нечетких множеств и их функциями принадлежностей закончила и готова для настройки на выполнение другой нечеткой операции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1990 |

|

SU1805473A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1993 |

|

RU2040038C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для определения граничных точек хроматографического пика | 1986 |

|

SU1456973A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1619252A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в однородных вычислительных структурах, для реализации нечетких алгоритмов. Целью изобретения является расширение функциональных возможностей за счет обработки числовых зна- чений элементов нечетких множеств. Ячейка однородной структуры содержит три коммутатора, сдвиговый регистр, четыре группы элементов И, два блока приема информации, блок передачи информации, шесть регистров, два регистра с тремя состояниями на выходе, три схемы сравнения, блок управления, дешифратор, два элемента ИЛИ и пять элементов задержки. В зависимости от кода настройки ячейка позволяет реализовать операции чтения, отрицания, конъюнкции, дизъюнкции, илигликации, эквивалентности, поиска над числовыми значениями элементов нечетких множеств. 3 з.п. ф-лы, 3 ил.

Формула-изобретения 1. Ячейка однородной структуры, содержащая с первого по третий регистры, сдвиговый регистр, три коммутатора, первую схему сравнения, блок управления, дешифратор и первую группу элементов И, причем первый информационный вход первого коммутатора соединен с прямым выходом первого регистра, инверсный выход которого соединен с вторым информационным входом первого коммутатора, выход которого

соединен с первым информационным входом первой схемы сравнения и информационным входом второго регистра; выход которого соединен с первым информационным входом второго коммутатора, второй информационный вход первой схемы сравнения соединен с выходом третьего коммутатора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходами третьего регистра, выходы первой схемы сравнения

соединены с первыми входами соответствующих элементов И первой группы, k-й выход дешифратора (k 1, п, где п 10 - число выполняемых операций в ячейке) соединен с k-м входом блока управления, m-й выход сдвигового регистра (т 1, р, где р п 4) соединен с п + т-м входом блока управления, отличающаяся тем, что, с целью расширения функциональных возможностей путем обработки числовых значений элементов нечетких множеств и соответствующих им функций принадлежностей, она содержит вторую, третью и четвертую группы элементов И, два блока приема информации, блок передачи информации, четвертый, пятый и шестой регистры, вторую и третью схемы сравнения, два регистра с тремя состояниями на выходе, два элемента ИЛИ и пять элементов задержки, причем выход третьего коммутатора соединен с информационным входом четвертого регистра, выход которого соединен с первым информационным входом второй схемы сравнения и вторым информационным входам второго коммутатора, выход которого соединен с информационным входом пятого регистра, выход которого соединен с первым информационным входом третьей схемы сравнения и первым входом блока передачи информации, второй вход которого соединен со входом разрешения считывания ячейки, первый и второй информационные входы ячейки соединены с первыми входами соответственно первого и второго блоков приема информации, вторые входы которых соединены соответственно с первым и вторым входами признака готовности передачи ячейки, первый и второй выходы разрешения передачи которой соединены с первым выходом соответственно первого и второго блоков приема информации/вторые выходы которых соединены соответственно с входами разрешения записи первого и третьего регистров, управляющие входы первого и третьего коммутаторов соединены соответственно с первым и вторым выходами блока управления, третий и четвертый выходы которого соединены со входами первого и второго элементов задержки, выходы которых соединены соответственно с входом разрешения приема первой схемы сравнения и входом разрешения записи второго регистра, выход последнего из которых соединен с вторыми информационными входами второй и третьей схем сравнения, первый и второй выходы третьей схемы сравнения соединены с первыми входами соответственно первого и второго элементов И второй группы, выходы первого и второго элементов И которой соединены соответственно с входами разрешения включения первого и второго регистров с тремя состояниями на выходе, входы разрешения записи которых соединены соответственно с вторыми выходами первого и второго блоков приема информации, третьи выходы которых соединены с информационными входами соответственно первого и второго регистров с тремя состояниями на выходе, выходы которых соединены с первым входом блока передачи информации, первый выход которого является информационным выходом ячейки, выход признака готовности передачи которой соединен с вторым выходом блока передачи информации, третий вход которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И второй группы, выходы с пятого по восьмой блока управления соединены соответственно с входами третьего и четвертого элементов задержки, управляющим входом второго коммутатора и входом пятого элемента задержки, выход последнего из которых соединен с входом разрешения записи пятого регистра, первый и второй входы первого элемента И третьей группы соединены с входами разрешения записи соответственно первого и третьего регистров, информационные входы которых соединены с третьими выходами соответственно первого и второго блоков приема информации, третьи входы которых соединены с первым и вторым разрядами входа дешифратора, второй разряд входа которого .соединен с первыми входами второго и третьего элементов И третьей группы, второй вход второго элемента И и первый вход четвертого элемента И которой соединены с первым разрядом входа дешифратора, настроечные входы ячейки, соединены с информационным входом шестого регистра, вход разрешения записи и выход которого соединены соответственно с входом разрешения записи настройки ячейки и входом дешифратора, второй и третий входы четвертого элемента И третьей группы соединены соответственно с первым входом первого элемента И и вторым входом третьего элемента И третьей группы, третий вход третьего элемента И которой соединен с вторым входом первого элемента И, третий вход первого элемента И третьей группы соединен с прямым выходом второго элемента И третьей группы, инверсный выход второго элемента И которой соединен с третьим входом четвертого элемента И третьей группы, выходы первого, третьего и четвертого элементов И

третьей группы соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ, выход которого соединен с входом разрешения сдвига сдвигового регистра , выходы третьего и четвертого элементов задержки соединены соответственно с входом разрешения записи четвертого регистра и входом разрешения приема второй схемы сравнения, выходы с девятого по четырнадцатый блока управления соединены с вторыми входами элементов И второй группы, с объединенными первыми входами первого и второго, третьего и четвертого, пятого и шестого, седьмого и восьмого, девятого и десятого элементов И четвертой группы, вторые входы первого, третьего, пятого и седьмого элементов И которой соединены с первым выходом второй схемы сравнения, второй выход которой соедин.ен с вторыми входами второго, четвертого, шестого и восьмого элементов И четвертой группы, вторые входы девятого и десятого элементов которой соединены соответственно с третьим и четвертым выходами второй схемы сравнения, пятнадцатый и шестнадцатый выходы блока управления соединены с вторыми объединенными входами соответственно первого, второго и третьего, четвертого элементов И первой группы, S-й выход которой (S - 1, t, где t n - 6) соединен с (п + р + 5}-м входом блока управления, (п + р + t + к)-й вход которого соединен с выходом k-ro элемента И четвертой группы.

третьего, девятого, четвертого,, пятнадцатого и второго элементов И, вторые входы W-ro элемента ИЛИ соединены соответственно с выходами тринадцатого, семнадцатого, пятого, седьмого, одиннадцатого, восьмого, семнадцатого и четвертого элементов И, третьи входы первого, третьего, четвертого, пятого и восьмого элементов ИЛИ соединены с выходами соответственно пятнадцатого, девятого, одиннадцатого, тринадцатого и шестого элементов И, семнадцатый вход блока управления соединен с четвертыми входами первого, третьего и четвертого элементов ИЛИ и третьим входом второго элемента ИЛИ, восемнадцатый вход блока управления соединен с пятым входом четвертого элемента ИЛИ, пятый вход третьего элемента ИЛИ и четвертый вход пятого элемента ИЛИ соединены с девятнадцатым входом блока управления, двадцатый вход которого соединен с шестым входом четвертого элемента ИЛИ и пятым входом пятого элемента ИЛИ, двадцать первый вход блока управления соединен с пятым входом первого элемента ИЛИ, с четвертым входом второго элемента ИЛИ, третьим входом седьмого элемента ИЛИ и четвертым входом восьмого элемента ИЛИ, шестой и седьмой входы третьего элемента ИЛИ соединены с выходами соответственно одиннадцатого и тринадцатого элементов И, седьмой, восьмой и девятый входы четвертого элемента ИЛИ соединены с выходами девятого, тринадцатого и двадцатого элементов И, шестой вход пятого элемента ИЛИ соединен с выходом двадцатого элемента И, пятый вход восьмого элемента ИЛИ соединен с выходом восьмого элемента И, выходы с шестого по четырнадцатый которого соединены с входами соответственно с двадцать второго по тридцатый блока управления, входы с третьего по седьмой шестого элемента ИЛИ соединены соответственно с двадцать вторым, двадцать Треть- им, двадцать пятым, двадцать восьмым и тридцатым блока управления, выходы с девятого по шестнадцатый блока управления соединены с выходами сбОт ветственно двадцать второго, десятого, двенадцатого, четырнадцатого, девятнадцатого, двадцать первого, шестнадцатого и восемнадцатого элементов И.

соединен с вторым входом второго элемента И, выход которого соединен с входом разрешения сдвига сдвигового регистра и первым выходом блока приема информации, второй выход которого соединен с выходом признака переполнения счетчика и входом элемента НЕ, третий выход блока приема информации соединен с выходом сдвигового регистра, информационный вход которого соединен с первым входом блока приема информации, второй и третий входы которого соединены соответственно с вторым и третьим входами первого элемента И.

SO

52

| Элемент ассоциативной матрицы | 1973 |

|

SU478297A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-04-13—Подача