Изобретение может быть использовано для построения вычиСЛИтельных маплин и дискретных устройств автоматики.

Известна логическая схема «ИЛИ-И- НЕ, содержащая туннельно-транзисторный триггер, дополнительный триггер па туппельном диоде и резисторе, диод с накоплением заряда, один вывод которого соединен с выходом двухступенчатой диодной схемы «ИЛИ-И, а другой вывод через .разделительный диод подключен к источнику синхронизирующих импульсов.

с целью поэыщенмя быстродействия, надежности работы и экономичности в предлагаемую логическую схему «ИЛИ-И-НЕ дополнительно введен второй диод с накоплением заряда, причем выход двухступенчатой диодпой схемы «ИЛИ-И подключен ко входу туннельно-транзисторного триггера через туппельпый диод дополнительного триггера, а второй диод с накоплением заряда подключен одноименным полюсом к общей точке (первого диода с накоплением заряда и разделительного диода, а вторым полюсом - к общей шине.

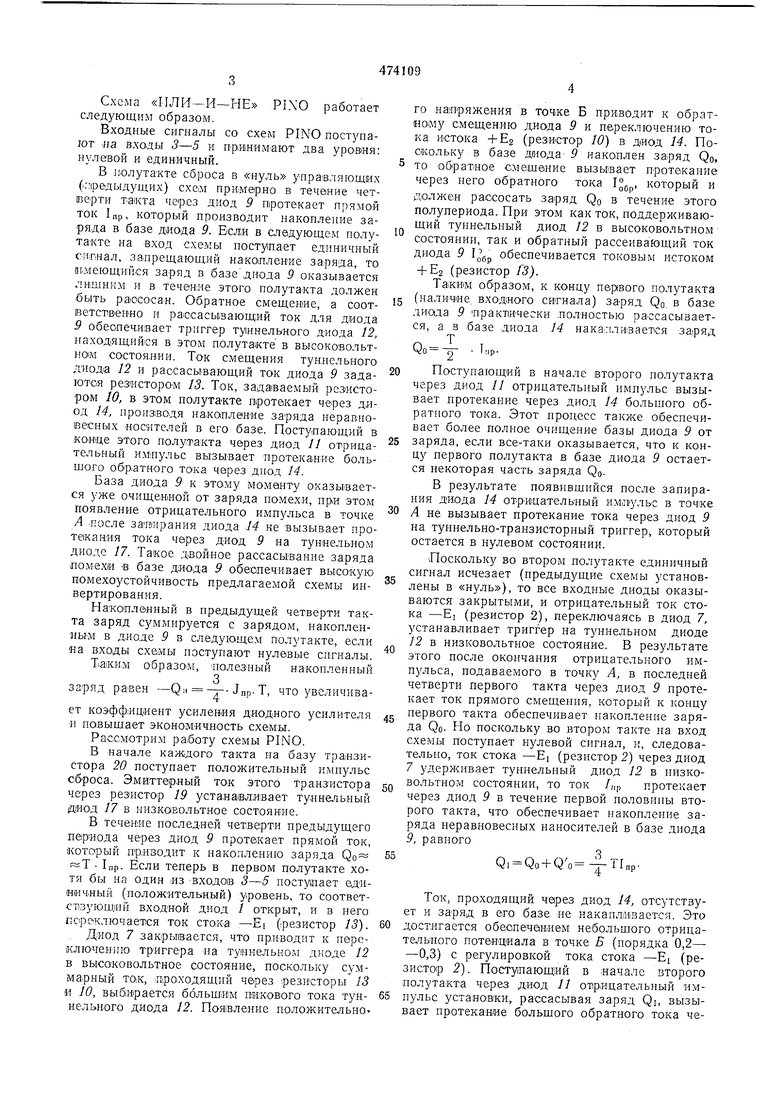

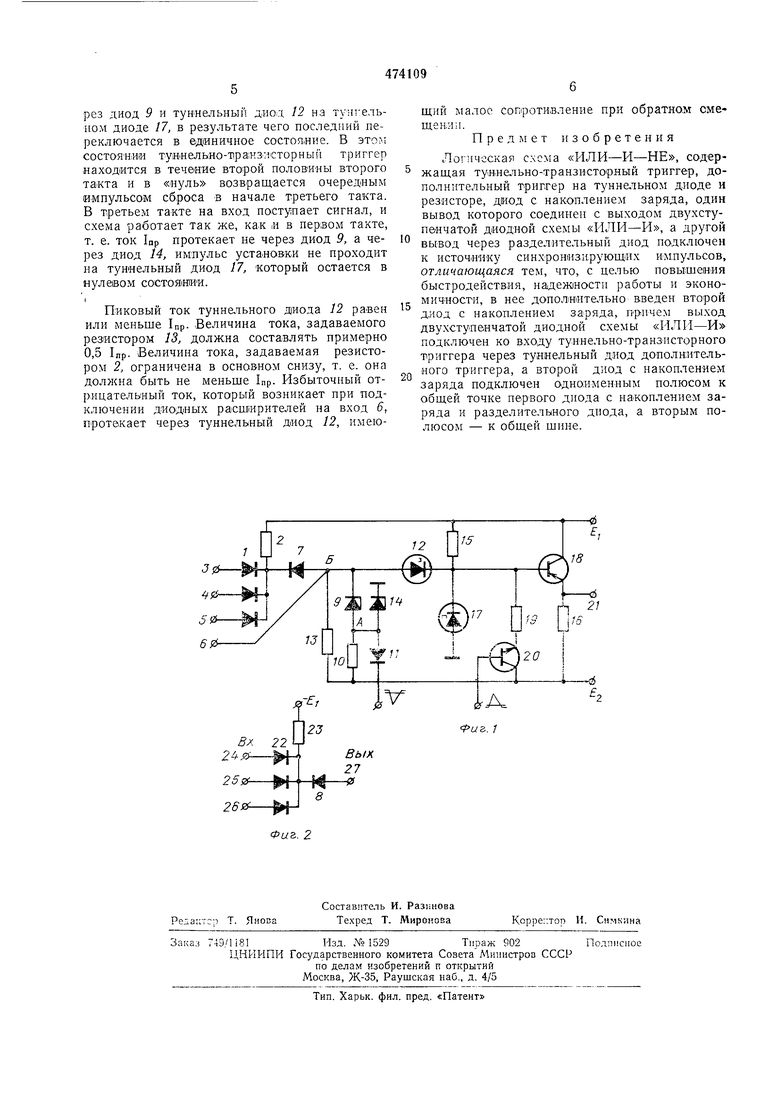

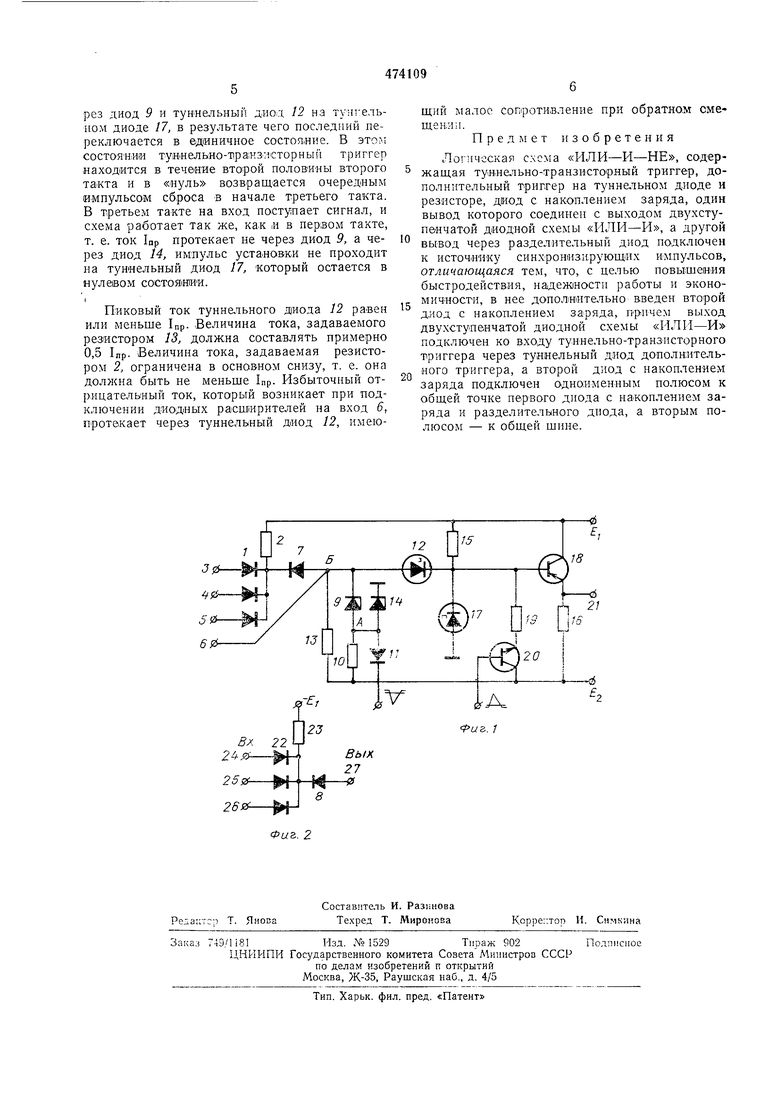

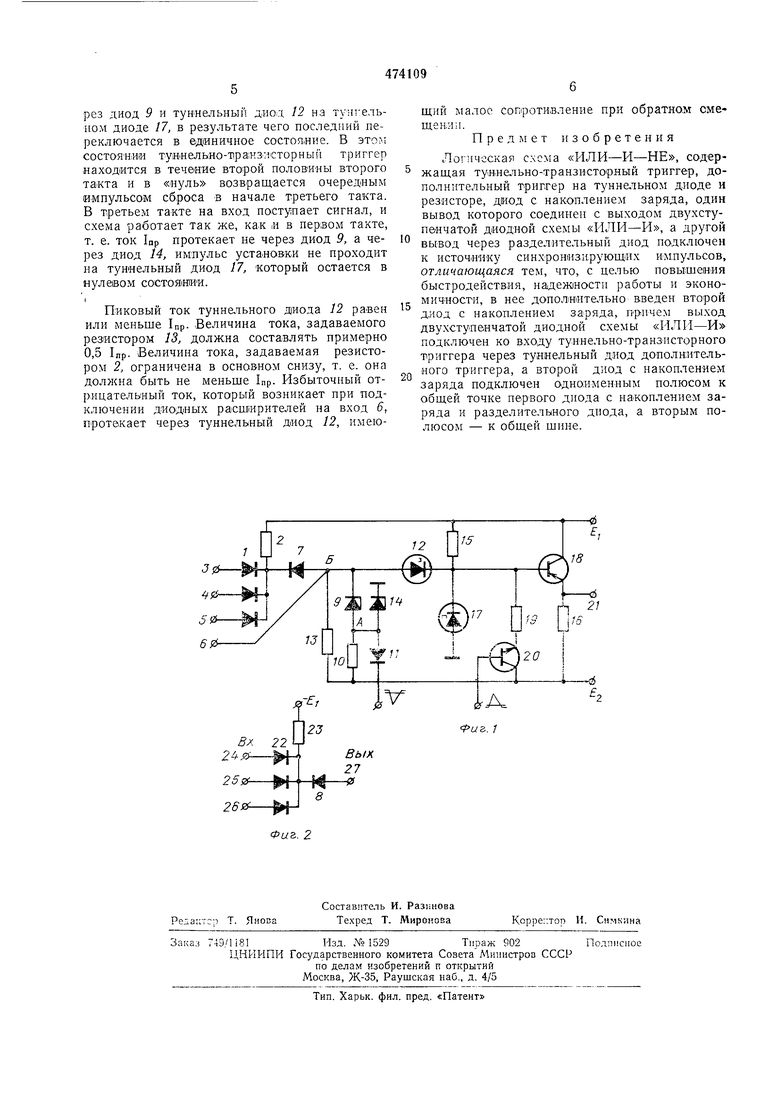

На фиг. 1 показана схема «ИЛИ-И-НЕ PINO; на фиг. 2 показана диодная схема, которая подключается на вход основной схемы «ИЛИ-И-НЕ для расщирения ее логических возможностей.

Входные диоды , резистор 2 и источник -EI образуют схему сборки единичных (положительных) сигналов, которые поступают на входы 3, 4, 5 схемы. При подключеНИИ на вход 6 расщирителя диод 7 схемы PINO и диод 8 (фиг. 2) расщирителя образуют схему сотаиадения для положительных .

Диод 9 с накоплением заряда, резистор 10, обеспечивающий ток прямого смещен я ДНЗ, и разделительный диод 11, через который подаются отрицательные импульсы установки, образуют диодный усилитель тока.

Триггер на туннельном дшоде 12 и резисторе 13, а также диод 14 с накоплением заряда служат для повыщения помехозащищенности надежности работы схемы.

Резисторы 15 и 16, туннельный диод 17 и транзистор 18 составляют бистабильный туннельно-транзисторный трлггор логической схемы.

Резистор 19 и транаистор 20 обеспечивают сброс этого триггера в «нуль. Выход 21 тупнельно-транаисторного триггера является выходом логической схемы.

На фиг. 2 приведена схема диодного расширителя, построенного на диодах 22, 8, резисторе 23. На выходы 24, 25 и 26 подаются входные сигналы, выход 27 подключается ко входу 4 схемы PINO

Схема «или-И-НЕ

PiXO работает следующим образом.

Входные сигналы со схем PINO поступают На входы 3-5 и принимают два уровия: нулевой и единичный.

В иолутакте сброса в «нуль управляющих (предыдущих) схем примерно в течение четверти такта через диод 9 протекает прямой ток Inp, который производит накопление заряда в базе диода 9. Бсди в следующем полутакте на вход схемы поступает един:ичный си.пнал, за прещающлй наколление за;ряда, то имеющийся заряд в базе диода 9 оказывается . И:Шнкм и в течен.ие этого полутакта должен быть paiococaH. Обратное смещение, а соответственно и рассасывающий ток для диода 9 обеспечивает триггер туннельного диода 12, наход.ящ.ийся в этом полутакте в высоковольтной состоя-нии. Ток смещения туннельного диода 12 и рассасывающий ток диода 9 задаются резистором 13. Ток, зада ваемый рсз-истором 10, в этом полутакте протекает через диод 14, ироиз.водя накопление заряда неравновесных носителей в его базе. Поступающий в конце этого полутакта через диод // отрицательный им нульс вызывает протекание большого обратного тока через диод 14.

База диода 9 к это,му моменту оказывается уже очищенной от заряда помехи, при этом появление отрицательного импульса в точке А .после затирания диода :14 не вызывает протакааия тока через диод 9 на туннельном диоде 17. Такое двойное рассасывание заряда помехи В базе диода 9 обеслечивает высокую помехоустойчивость предлагаемой схемы инвертирования.

Накопленный в предыдущей четверти такта заряд суммируется с зарядом, накопленНЫМ в диоде 9 в следующем полутакте, если на входы схемы поступают нулевые сигналы.

Т|а1ким образоМ, полезный накопленный

заряд равен -QH -;- JnoТ, что увеличива4ет коэффициент усиления диодного усилителя и повышает экономичность схемы.

Рассмотрим pai6oTy схемы PINO.

В начале каждого такта на базу транзистора 20 поступает положительный импульс сброса. Эмиттерный ток этого транзистора через резистор 19 устанавливает туннельный диод 17 в низковольтное состояние.

В течение последней четверти предыдущего периода через диод 9 протекает прямой ток, атотсрый приводит к накоплению заряда Qo «Т Inp. Если теперь в первом полутакте хотя бы на один из ВХОД01В 3-5 поступает единичный (положительный) :уровень, то соответСБзуюш,ий входной диод / открыт, и в него переключается ток стока -EI (резистор 13).

Диод 7 закрьнвается, что нриводит к перезслючению триггера на тз ннельком диоде 12 в высоковольтное состояние, поскольку суммарный ток, .проходящий через резисторы 13 и 10, выбирается б6льши м пикового тока туннельного диода 12. Поя1вление положительно

ГО напряжения в точке Б приводит к обратному смещению диода 9 и переключению тока истока +Е2 (резистор 10) в диод 14. Поскольку в базе двioдa 9 накоплен заряд Qo, то обратное смешение вызывает протекание через него обратного тока 1°, который и должен рассосать заряд Qo в течение этого полупериода. При этом как ток, поддерживающий туннельный диод 12 в высоковольтном состоянии, так и обратный рассеивающий ток диода 9 1. обеспечивается токовым истоком -f Е2 (резистор f3).

Таким образом, к концу первого полутакта (наличие входного сигнала) заряд Qo, в базе диада 9 практически полностью рассасывается, а в базе диода 14 накаплввается заряд

Т Qo -2 ipПоступающий в начале второго полутакта через диод // отрицательный импульс вызывает протекание через диод 14 большого обратного тока. Этот процесс также обеспечивает более полное очищение базы диода 9 от заряда, если все-таки оказывается, что к концу первого полутакта в базе диода 9 остается некоторая часть заряда QQ.

В результате появившийся после запирания диода 14 отрицательный импульс в точке А не вызывает протекание тока через диод 9 на туннельно-транзисторный триггер, который остается в нулевом состоянии.

Поскольку во втором полутакте единичный сигнал исчезает (предыдущие схемы установлены в «нуль), то все входные диоды оказываются закрытыми, и отрицательный ток стока -EI (резистор 2), переключаясь в диод 7, устанавливает триггер на туннельном диоде 12 в низковольтное состояние. В результате этого после окончания отрицательного импульса, подаваемого в точку А, в последней четверти первого такта через диод 9 протекает ток прямого смещения, который к концу первого такта обеспечивает Егакопление заряда QO. По поскольку во втором такте на вход схемы поступает нулевой сигнал, и, следовательно, ток стока -EI (резистор 2) через диод 7 удерлсивает туннельный диод 12 в низковольтном состоянии, то ток /пр протекает через диод 9 в течение первой половины второго такта, что обеспечивает накопление заряда неравновесных наносителей в базе диода 9, равного

3 Qi Qo + Qo -pTlnp.

Ток, проходящий чарез диод 14, отсутствует и заряд в его базе не накапливается. Это достигается обеспечением небольшого отрицательного потенциала в точке Б (порядка 0,2- -0,3) с регулировкой тока стока -EI (резистор 2). Поступающий в начале второго полутакта через диод // отрицательный импульс установки, рассасывая заряд Qi, вызывает протекание большого обратного тока через диод 9 и туинельный диоа 12 на туягельUOM диоде 17, в результате чего последний переключается в единичное состояние. В этод; состояиирл ту нельно-т1ра;кЗИ1Сторный триггер находится в течение второй половины второго такта и в «нуль возвращается очередным импульсом сброса в начале третьего такта. В третьем такте на вход поступает сигнал, и схема работает так же, ка.к ,и в пер,вом такте, т. е. ток 1пр протекает не через диод 9, а через диод 14, импульс устаНовки не проходит на туннельный диод 17, который остается в нулевом состояиии.

Пиковый ток туннельного диода 12 равен или меньше 1пр. Величина тока, задаваемого резистором 13, должна составлять примерно 0,5 1пр. Величина тока, задаваемая резистором 2, ограничена в основном снизу, т. е. она должна быть не меньше Lp. Избыточный отрицательный ток, который возникает при подключении диодных расш1ирителей на вход 6, протекает через туннельный диод 12, имеюш,ий малое сопротивление при обратном омещен;И;1.

Предмет изобретения

Логическая схема «ИЛИ-И-НЕ, содержащая тувнельно-транзисторный триггер, дополнительный триггер на тунне,11ьном диоде и резисторе, диод с накоплением заряда, один вывод которого соединен с выходом двухступенчатой диодной схемы «ИЛИ-И, а другой вывод через разделительный диод подключен к источнику синхронизируюшнх и мпульсов, отличающаяся тем, что, с целью повышения быстродействия, надеж1ности работы и экономичности, в нее допол1Н1Ите чьно введен второй диод с накоплением заряда, причем выход двухступенчатой диодной схемы «ИЛИ-И подключен ко входу туннельно-транзисторного триггера через туннельный диод дополнительного триггера, а второй диод с накоплением заряда подключен одноименным полюсом к общей точке первого диода с накоплением заряда и разделительного диода, а вторым полюсом - к общей шпне.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий логический элемент или-и-не | 1973 |

|

SU478441A1 |

| Логический элемент | 1974 |

|

SU572930A2 |

| ОЗНАЯ ПАТЕНТШ-г^АН^Г'Е^ИАЯ | 1971 |

|

SU304700A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| ВСЕСОЮЗНАЯ ПАТГ..,.Ч?СКАЙбиблиотека wsBAВ. Е. Мельник | 1972 |

|

SU336812A1 |

| ПАТ?Ш'Ш-[1ХСГ'Е^:чДП | 1973 |

|

SU362487A1 |

| Однотактный регистр сдвига | 1972 |

|

SU447761A1 |

| Управляемый триггер | 1974 |

|

SU541290A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ | 1972 |

|

SU345600A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU235817A1 |

Авторы

Даты

1975-06-15—Публикация

1973-05-15—Подача