1

Изобретение относится к области цифровой вычислительной техники и дискретной автоматики.

Известен регистр сдвига, выполненный на логических элементах И - НЕ (ИЛИ - НЕ), каждый разряд которого содержит три триггера с раздельным запуском - один памяти и два коммутационных, причем единичный выход первого коммутационного триггера соединен с единичным входом второго, нулевой - с единичным входом триггера памяти, нулевой выход второго коммутационного триггера соединен с нулевым входом триггера памяти и со вторым нулевым входом первого коммутационного триггера, а первые нулевые входы коммутационных триггеров - со входом тактовых импульсов, нулевой выход триггера памяти соединен с единичным входом коммутационного триггера последующего разряда регистра. Однако эта схема может иметь логические состязания.

В предлагаемом изобретепии с целью устранепия состязаний логических элементов единичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, второй пулевой вход первого коммутационного триггера - с единичным выходом второго коммутационного триггера предыдущего разрялда; между разрядами включен дополнительный логический элемент, выход которого соединен со вторым нулевым входом второго коммутационного триггера, а вход - единичным выходом второго коммутационного триггера предыдущего разряда.

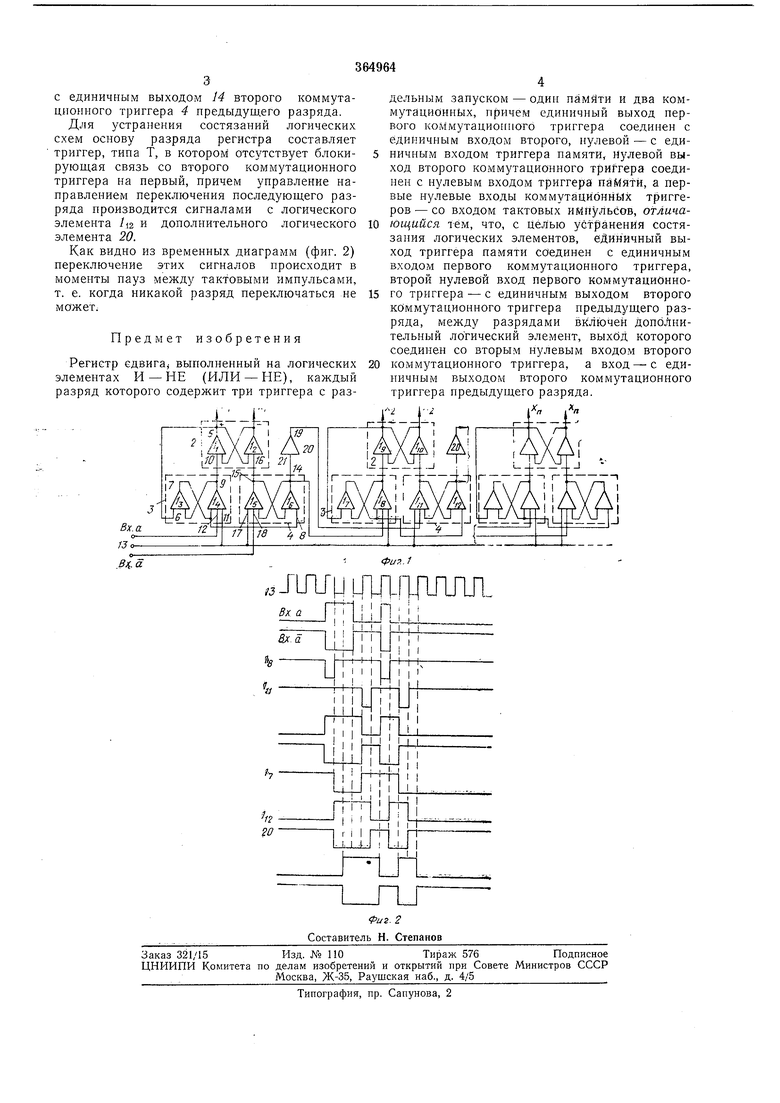

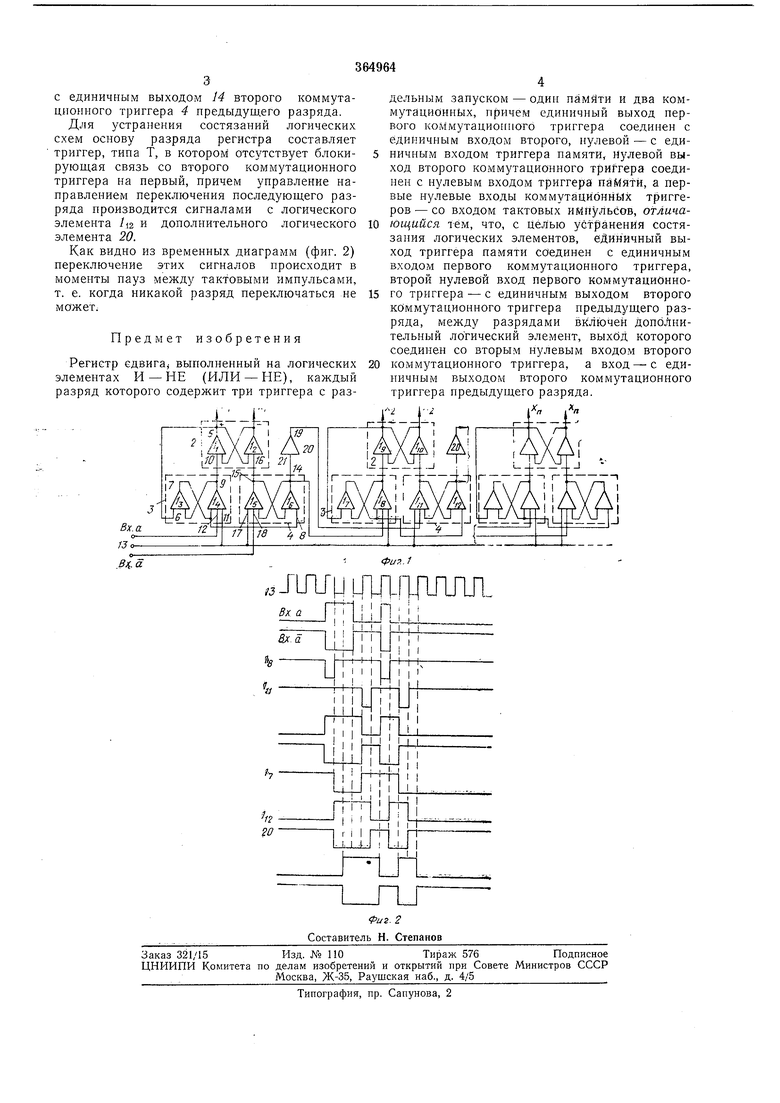

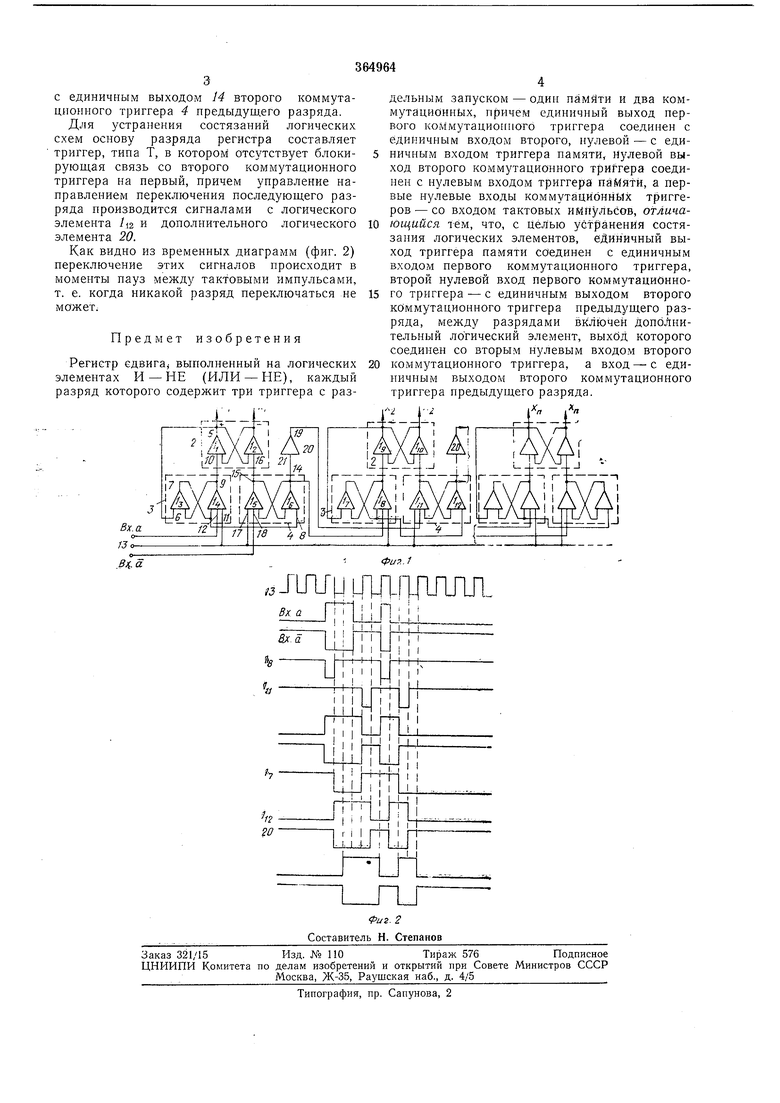

На фиг. 1 приведена схема регистра сдвига; на фиг. 2 - его временные диаграммы.

Разряд регистра сдвига, построепного на логических элементах /п И - НЕ (ИЛИ -

НЕ), содержит три триггера с раздельным запуском - триггер 2 памяти и два коммутационных триггера 3, 4. Единичный выход 5 триггера 2 памяти соединен с единичным выходом 6 первого коммутационного триггера 3,

единичный выход 7 которого соединен с единичным входом 8 другого коммутационного триггера 4, а нулевой выход 9 - с единичным входом 10 триггера 2 памяти. Два нулевых входа 11, 12 первого коммутационного триггера 3 соединены попарно с шипой 13 тактовых импульсов и единичным выходом 14 второго коммутационного триггера 4 предыдущего разряда.

Нулевой выход 15 второго коммутационпого

триггера 4 соединен с нулевым входом 16 триггера 2 памяти, а два пулевых входа 17, 18 второго коммутационного триггера 4 соединены попарпо с шиной 13 тактовых импульсов и с выходом 19 дополнительного логического элемента 20, вход 21 которого соединен

с единичным выходом 14 второго коммутационного триггера 4 нредыдущего разряда.

Для устранения состязаний логических схем основу разряда регистра составляет триггер, тина Т, в котором отсутствует блокирующая связь со второго коммутационного триггера на первый, причем управление направлением переключения последующего разряда производится сигналами с логического элемента /i2 и дополнительного логического элемента 20.

Как видно из временных диаграмм (фиг. 2) переключение этих сигналов происходит в моменты пауз между тактовыми импульсами, т. е. когда никакой разряд переключаться не может.

Предмет изобретения

Регистр сдвига выполненный на логических элементах И - НЕ (ИЛИ - НЕ), каждый разряд которого содержит три триггера с раздельным запуском - один памяти и два коммутационных, причем единичный выход первого коммутационного триггера соединен с единичным входом второго, нулевой - с единичным входом триггера памяти, нулевой выход второго коммутационного триггера соединен с нулевым входом триггера памяти, а первые нулевые входы коммутационных триггеров - со входом тактовых импульсов, отличающийся тем, что, с целью устранения состязания логических элементов, еДиМичный выход триггера памяти соединен с единичным входом первого коммутационного триггера, второй нулевой вход первого коммутационного триггера - с единичным выходом второго коммутационного триггера нредыдущего разряда, между разрядами включен дополнительный логический элемент, выход которого соединен со вторым нулевым входом второго

коммутационного триггера, а вход - с единичным выходом второго коммутационного триггера предыдущего разряда.

jmjg MmiWUin13

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕШИФРАТОР КОДОВЫХ ИНТЕРВАЛОВ ВРЕМЕНИ | 1973 |

|

SU365039A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ГРУППОВЫМ ПЕРЕНОСОМ | 1970 |

|

SU287121A1 |

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| Реверсивный регистр сдвига | 1974 |

|

SU593317A1 |

| Счетчик | 1981 |

|

SU961154A1 |

| -Разрядный регистр сдвига | 1977 |

|

SU746734A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU396719A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU285054A1 |

| РЕГИСТР СДВИГА | 1972 |

|

SU432602A1 |

Авторы

Даты

1973-01-01—Публикация