(5) СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик | 1977 |

|

SU705688A1 |

| Реверсивный счетчик | 1981 |

|

SU1003356A1 |

| Счетчик | 1985 |

|

SU1267614A1 |

| Параллельный счетчик | 1981 |

|

SU999168A1 |

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| ВСЕСОЮЗНАЯ ПАТ?111110-1ШЯП?! | 1973 |

|

SU364964A1 |

| ДЕШИФРАТОР КОДОВЫХ ИНТЕРВАЛОВ ВРЕМЕНИ | 1973 |

|

SU365039A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ГРУППОВЫМ ПЕРЕНОСОМ | 1970 |

|

SU287121A1 |

| Устройство для программного управления | 1984 |

|

SU1238035A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

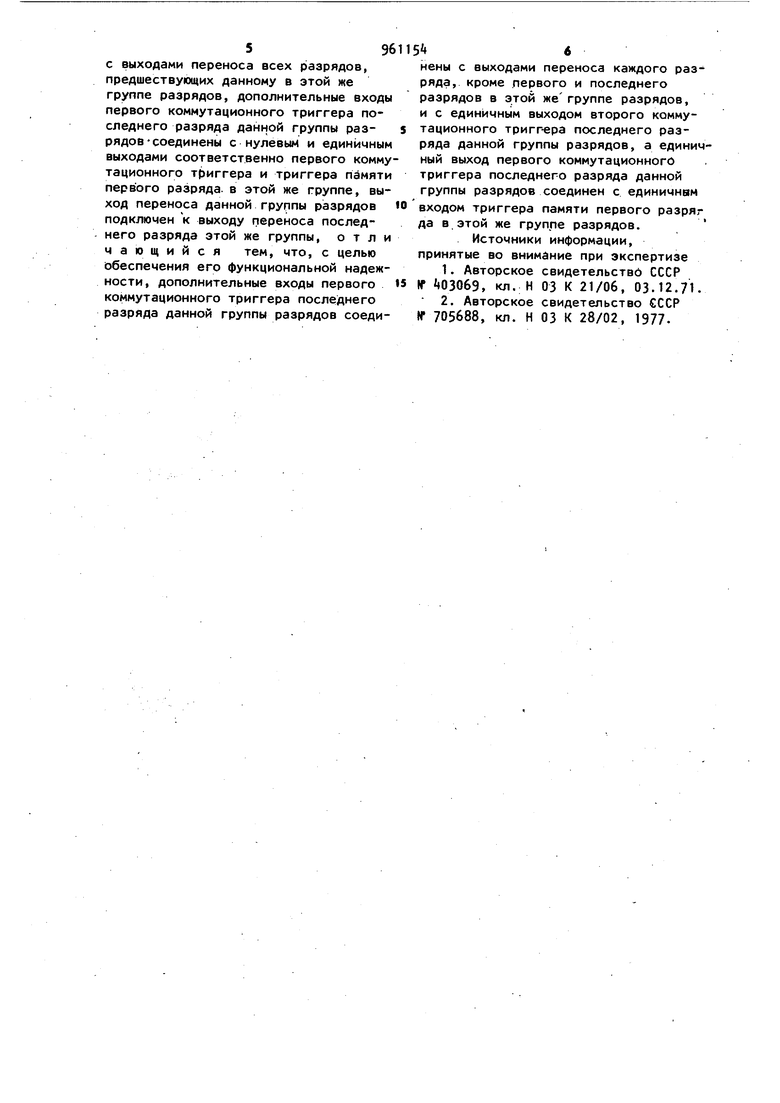

Изобретение относится к вычислительной технике и автоматике и может быть использовано для счета импульсо Известен счетчик, содержащий группы разрядов, каждый из которых содер(КИТ первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соединены с входом счетчика и выходами переноса предыдущих групп, разрешающие входы всех коммутационных триг геров разрядов данной группы разрядов, кроме последнего разряда этой же группы, и разрешающие входы первого коммутационного триггера послед него разряда данной группы разрядов соединены с выходами переноса каждого разряда, предшествующего данному в этой же группе разрядов t1 . Недостатками известного счетчика являются относительно низкое быстродействие и недостаточная надежность. Наиболее близким к изобретению по технической сущности является счетчик, содержащий Труппы разрядов, каждый из которых содержит первый и коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соединены с входом счетчика и выходами переноса предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разрядбв, кроме последнего разряда этой же группы, и разрешающие входы первого коммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса всех разрядов, предшествующих данному в этой же группе разрядов, дополнительные входы первого коммутационного триггера последнего разг ряда данной труппы разрядов соединены с нулевым и единичным выходами соответственно первого Коммутационного триггера и триггера памяти первого разряда в этой же группе, а выход переноса данной группы разрядов подключен к выходу переноса последнего разряда этой же группы 2, Недостатком известного устройства является низкая функциональная надеж ность из-за наличия в каждой группе счетчика опасных состояний, вызываемых разбросом задержек логических элементов. . Цель изобретения - обеспечение функциональной надежности счетчика. Указанная цель достигается тем, что в счетчике, содержащем группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, причем тактовые входы всех коммутационных тригге ров соединены с входом счетчика и вы ходами переноса предыдущих групп, а разрешающие входы всех коммутационны триггеров разрядов данной группы раз рядов, кроме последнего разряда этой же группы, и разрешающие входы первого коммутационного триггера послед него разряда данной группы разрядов соединены с выходами переноса всех разрядов, предшествующих данному в этой же группе разрядов, дополнитель ные входы первого коммутационного триггера последнего разряда данной группы разрядов соединены с нулевым и единичным выходами соответственно первого коммутационного триггера и триггера памяти первого разряда в этой же группе, выход переноса данно группы разрядов подключен к выходу переноса последнего разряда этой же группы, дополнительные входы первого коммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса .каждого разряда, кроме первого и последнего, разрядов в этой же группе разрядов, и с единичным выходом второго коммут ционного триггера последнего разряда данной группы разрядов, а единичный выход первого коммутационного три1 гера последнего разряда данной групп разрядов соединен с единичным входом триггера памяти первого разряда в этой же группе. На чертеже изображена функциональ ная схема счетчика. Счетчик содержит группу разрядов 1, каждый из разрядов 2-1r2 k в груп пе содержит первый и второй коммутационные триггеры выполненные соответственно на парах элементов И-НЕ 3 и , и триггер памяти, выполненный на паре элементов И-НЕ 7-8, выходы 9 переноса групп и вход 10 счетчика. Каждая группа разрядов счетчика работает следующим образом. Изменение состояния триггеров памяти группы происходит по импульсам, подаваемым на вход 10 счетчика при условии, что сигналы с выходов 9 переноса предыдущих групп равны логической 1. При выполнении этого условия с приходом очередного тактового импульса срабатывает элемент И-НЕ Первого разряда 2-1, и триггер памяти этого разряда переключается, в единичное логическое состояние, если перед этим все триггеры памяти группы находились в нулевом состоянии. По ближайшей паузе между тактовыми импульсами на выходе элемента И-НЕ 6 разряда 2-1 появляется логическая 1. При следующем выполнении услония срабатывания для этой группы разрядов происходит переключение триггеров памяти разрядов , и т. д. 2 М-ый тактовый импульс (где М коэффициент пересчета предыдущих групп разрядов счетчика) производит переключение всех триггеров памяти данной группы разрядов и формирует сигнал переноса на выходе этой группы. Опасные состязания в этом такте отсутствуют, так как логический О на выходе элемента И-НЕ 7 первого разряда появится лишь тогда, когда сработает, элемент И-НЕ 15 разряда 2ak этой группы и установит логическую 1 на выходе элемента И-НЕ 3 разряда 2ak этой же группы. Таким образом, предлагаемый счетчик не содержит опасных состязаний и является функционально надежным. Формула изобретения Счетчик, содержащий группы разрядов, каждый VI3 которых содержит первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соединены с входом счетчика и выходайи переноса предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разрядов, кроме последнего разряда этой же группы, и разрешающие входы первого коммутационного триггера последнего разряда данной группы разрядов соединены

59611

с выходами переноса всех разрядов, предшествующих данному в этой же группе разрядов, дополнительные входы первого коммутационного триггера последнего разряда данной группы раз- s рядовсоединены с нулевым и единичным выходами соответственно первого коммутационного триггера и триггера памяти первого разряда, в этой же группе, выход переноса данной группы разрядов «О подключен к выходу переноса последнего разряда этой же группы, о т л и чающийся тем, что, с целью обеспечения его функциональной надежности, дополнительные входы первого (5 коммутационного триггера последнего разряда данной группы разрядов соеди «

нены с выходами переноса каждого разряда, кроме первого и последнего разрядов в этой же группе разрядов, и с единичным выходом второго коммутационного тригг-ера последнего разряда данной группы разрядов, а единичный выход первого коммутационного триггера последнего разряда данной группы разрядов соединен с единичном входом триггера памяти первого разряг да в этой же группе разрядов.

Источники информации, принятые во внимание при экспертизе

ff ijoaoes, кл. н оз к 2i/o6, 03.12.71.

Авторы

Даты

1982-09-23—Публикация

1981-02-06—Подача