(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

1

Изобретение относится к импульсной технике.

Известен делитель частоты с програм.мным управлением, содержащий коммутатор входных импульсов, три счетчика имнульсов и три логических элемента ИЛИ, осуществляющих коммутацию поступления импульсов на счетчики 1. СоелТ.инения счетчиков выполнены так, что первый счетчик осуществляет деление на целые числа, а коммутация осуществляется двумя другими счетчиками и логическими элементами.

Недостатком этого делителя является его сложность.

Наиболее близким по технической сущности к предлагаемому является делитель частоты, содержащий трехразрядный распределитель, каждый разряд которого состоит из триггера памяти, коммутационного триггера, причем нулевой выход триггера памяти данного разряда соединен с единичным входом коммутационного триггера последующего разряда, а нулевой выход коммутационного триггера данного разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационного триггера последующего разряда и триггера памяти предыдущего разряда, N-разрядный распределитель, каждый разряд которого содержит триггер памяти, коммутационный триггер п логический элемент И-НЕ, а последний разряд - также дополнительный триггер, причем нулевой выход триггера памяти последнего разряда соединен с единичным входом дополнительного три1тера, нулевой выход которого соединен с нулевым входом этого триггера памяти, нулевой выход коммутационного триггера пос10леднего разряда соединен с нулевым входом дополнительного триггера и с входами логических элементов И-НЕ всех разрядов, единичный выход дополнительного триггера также соединен с входами логических элементов И-НЕ всех разрядов 2.

Этот делитель характеризуется недостаточной надежностью.

Цель изобретения - повыщение надежности.

20 Поставленная цель достигается тем, что в делитель частоты, содержащий трехразрядный распределитель, каждый разряд которых состоит из триггера памяти, коммутационного триггера, причем нулевой выход

триггера памяти данного разряда соединен с единичным входом коммутационного триггера последующего разряда, а нулевой коммутационного триггера данного разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационного триггера последующего разряда и триггера памяти предыдущего разряда, N-разрядный распределитель, каждый разряд которого содержит триггер памяти, коммутационный триггер и логический элемент И-НЕ, а последний разряд - также дополнительный триггер, причем нулевой выход триггера памяти последнего разряда соединен с единичным входом дополнительного триггера, нулевой выход которого соединен с нулевым входом триггера памяти, нулевой выход коммутационного триггера последнего разряда соединен с нулевым входом дополнительного триггера и с входами логических элементов И-НЕ всех разрядов, единичный выход дополиигельного триггера также соединен с входами логических элемен тон И-НЕ всех рязрндов, введены дополнительных логических элемента И-НЕ и логический элемент НЕ, гфичем пулевой выход коммутационного триггера ;ервого разряда трехразрядного распреде;1;-ггеля соединен с входами первого и BTOpoi-o дополнительных логических элементов И-НЕ, единичный выход коммутационно Х) триггер второго разряда трехразрядно;ч) распредели1еля соединен с входом первого дополнительного логического элеме1гга И-НЕ, выход которого соединен с нулевым входом л.очолпительного триггера и с входами ,1О1ическ1-гх элементов И-НЕ N-разрядпо1-о распреде.п-1теля, единичные выходь тригге юв памяти первого разряда трехразрядного распределителя и последнего разряда N-разрядного распределителя соединены с входами второго дополнительного логического э.лем(нта Hi-HE, нулевой выход комму1ациопного риггера последнего разряда К-разрядного распре/делителя соединен с входом второго дополнительного логического элемента И-НЕ и через логический элемент НЕ -- с входом третьего дополнительного логического элеме 1та И-НЕ. нулевой выход коммутацио}и1ого триггера иоследне1о разряда и единичный выход дополнительного триггера N-разрядного распределителя соединены с нулевыми входами коммутационных триггеров трехразрядного распределителя, единичный выход коммутационного тригтера первого разряда трехразрядного распределителя соединен с входом третьего дополнительного логического элемента И-НЕ, выход которого, а также выход второго дополнительного логического элемента И-НЕ соединены с входами четвертого доиолнительного логического элемента И-НЕ.

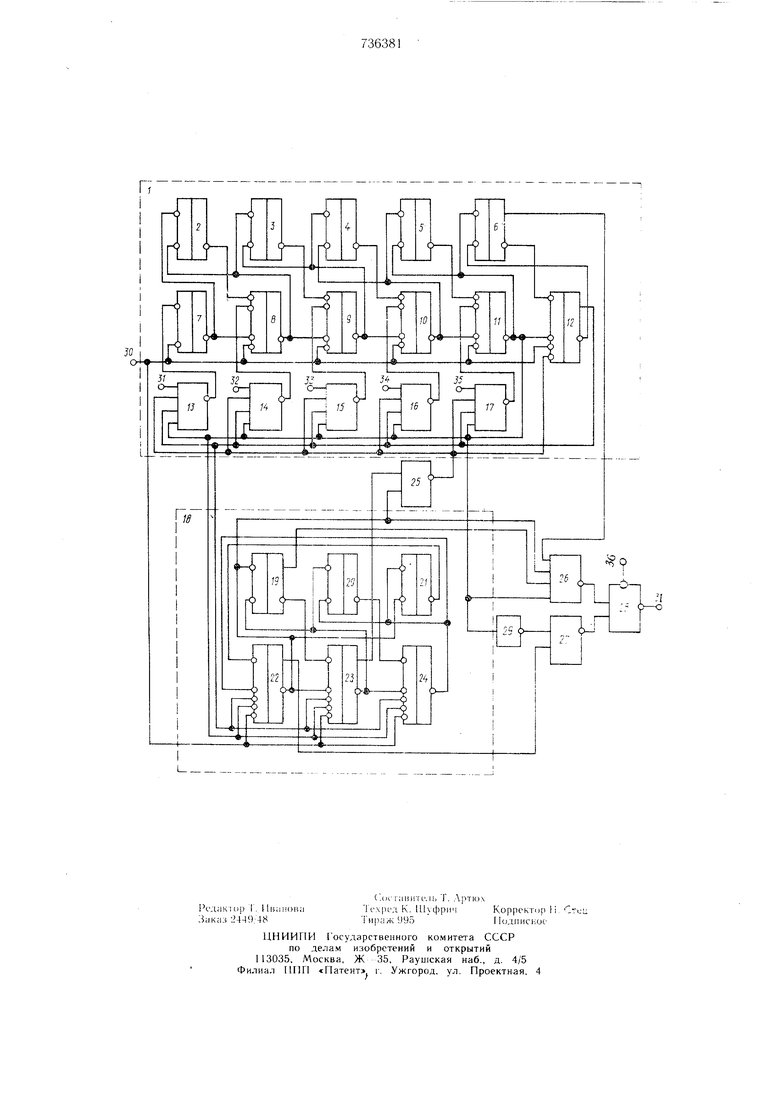

На чертеже приведена структурная электрическая схема предлагаемого делителя частоты.

Делитель содержит N-разрядный распределитель 1, состоящий из триггеров памяти 2-6, коммутационных триггеров 7-И, дополнительного триггера 12, логических элементов И-НЕ 13-17, трехразрядный распределитель 18, состоящий из триггеров памяти 19-21 коммутационных триггеров 22-24, логические элементы И-НЕ 25-28, логический элемент НЕ 29. Входной сигнал подан на входную щину 30; на щины 31-35 поданы сигналы управления. Выходной сигнал снижается с выхода 36.

Делитель работает следующим образом.

В исходном состоянии триггеры памяти 6 и 21 распределителей находятся в единичном состоянии; остальные триггеры памяти обоих распределителей находятся в нулевом состоянии; сигнал на входной щине 30 отсутствует (равен логическому нулю).

Нусть необходимо осуществить деление входной последовательности импульсов на 4,5. Для этого на щину 32 подается сигнал, равный логической единице. На остальные п.ины 31, 33, 34, 35 поступают сигналы, равные логическому нулю. С приходом на щину 30 первого тактового импульса на нулевом выходе триггера 12 появляется сигнал, равный логическому нулю, который устанавливает триггер 6 в нулевое состояние. Одновременно сигналы, равные логическому нулю, появляются на нулевых выходах триггеров 8 и 22, которые устанавливают триггеры 3 и 19 в единичное состояние, а триггер 21 - в нулевое.

Иосле окончания действия тактового импу.чьса на единичном выходе- триггера 12 появляется сигнал, равный логическому нулю, который закрывает логические элементы И-НЕ: 13-17 и блокирует сдвиг единицы в трехразрядном распределителе. Ноэтому с приходом второго тактового импульса сдвиг единицы происходит только в N-разрядном распределителе (триггер 4 устанавливается в единичное состояние, а триггер 3 возвращается в нулевое состояние}, .Аналогично с приходом третьего тактового импульса единица из триггера 4 переписывается в триггер 5, а с приходом четвертого импульса единицы из триггера 5 переписываются в триггер 6. Носле окончания четвертого тактового импульса на выходе логического элемента И-НЕ: 26 формируется сигнал, равный логическому нулю, который через логический элемент И-НЁ 28 поступает на выход 36 устройства.

Носкольку на единичном выходе триггера 12 появляется сигнал, равный логической единице, блокировка сдвига единицы в трехразрядном распределителе снимается, но логические элементы И-НЕ 13-17 остаются закрытыми сигналом, равным логическому нулю, с выхода логического элемента И-НЕ 25. Ноэтому с приходо.м пятого тактового импульса сдвиг единицы происходит только в трехразрядном распределителе (триггер

19 устанавливается в нулевое состояние, а триггер 20 - в единичное). При этом на единичном выходе триггера 19 появляется сигнал, равный логическому нулю, который закрывает логический элемент И-НЕ 26, и формирование выходного сигнала прекращается. После окончания действия входного импульса на выходе логического элемента И-НЕ 25 появляется сигнал, равный логической единице. Следовательно, с приходом шестого тактового импульса в единичное состояние устанавливаются триггеры 3 и 21, а триггеры 6 и 20 возвращаются в нулевое состояние. При этом опять сигнал, равный логическому нулю, с единичного выхода триггера 12 закрывает логические эл менты И-НЕ 13-17 и блокирует сдвиг единицы в трехразрядном распределителе. Далее с приходом седьмого тактового импульса триггер 3 устанавливается в нулевое состояние, а триггер 4 - в единичное. С приходом восьмого тактового импульса триггер 4 возвращается в нулевое состояние, а триггер 5 устанавливается в единичное. С приходом девятого тактового импульса на нулевом выходе триггера 11 появляется сигнал, равный логическому нулю, который устанавливает триггер 6 в единичное состояние, а триггер 5 - в нулевое и который через логический элемент НЕ 29 поступает на вход логического элемента И-НЕ 27.

Поскольку на единичном выходе триггера 22 - логическая единица, на выходе логического элемента И-НЕ 27 формируется сигнал, равный логическому нулю, который через логический элемент И-НЕ 28 поступает на выход 36 устройства.-После окончания действия тактового импульса устройство возвращается в исходное состояние.

Для осуществления деления частоты на 5,5 управляющий сигнал, равный логической единице, подается на шину 31, для деления частоты на 3,5 сигнал, равный логической единице подается на щину 33. Аналогичным образом может быть осуществлено деление частоты на другое число.

Формула изобретения

Управляемый делитель частоты импуль сов содержащий трехразрядный распределитель, каждый разряд которого состоит из триггера памяти, коммутационного триггера, причем нулевой выход триггера памяти данного разряда соединен с единичным входом коммутационного триггера последующего разряда, а нулевой выход коммутационного триггера данного разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами коммутационного триггера последующего разряда и триггера памяти предыдущего разряда, N-разрядный распределитель, каждый разряд которого содержит триггер памяти, коммутационный триггер и логический элемент И-НЕ, а последний разряд - (также дополнительный триггер)/при5 чем нулевой выход триггера памяти последнего разряда соединен с единичным входом дополнительноготриггера, нулевой выход которого соединен с нулевым входом этого триггера памяти, нулевой выход коммутационного триггера последнего разряда соединен с 10 нулевым входом дополнительного триггера и с входами логических элементов И-НЕ всех разрядов, единичный выход дополнительного триггера соединен с входами логических элементов И-НЕ всех разрядов, отличающийся тем, что, с целью повыщения надежности работы устройства, в него введены четыре дополнительных логических элемента И-НЕ и логический элемент НЕ, причем нулевой выход коммутационного триггера первого разряда трехразрядного распределителя сое0 динен с входами первого и второго дополнительных логических элементов И-НЕ, единичнь й выход коммутационного триггера второго разряда трехразрядного распределителя соединен с входом первого дополнительного логического элемента И-НЕ, выход которого соединен с нулевым входом дополнительного триггера и с входами логических элементов И-НЕ N-разрядного распределителя, единичные выходы триггеров памяти первого разряда трехразрядного распредели0 теля и последнего разряда N-разрядного распределителя соединены с входами второго дополнительного логического элемента И-НЕ, нулевой выход коммутационного триггера последнего разряда N-разрядного распределителя соединен с входом второго дополи нительного логического эле.мента И-НЕ и через логический элемент НЕ с входом третьего дополнительного логического элемента И-НЕ, нулевый выход коммутационного триггера последнего разряда и единичный д ВЫХОД дополнительного триггера N-разрядного распределителя соединены с нулевыми входами коммутационных триггеров трехразрядного распределителя, единичный выход коммутационного триггера первого разряда трехразрядного распределителя соедиJ нен с входом третьего дополнительного логического элемента И-НЕ, выход которого, а также выход второго дополнительного логического элемента И-НЕ соединены с входами четвертого дополнительного логического элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

(прототип)

Авторы

Даты

1980-05-25—Публикация

1977-10-03—Подача