1

Изобретение относится к области вычислительной техники и автоматики и может быть использовано в адаптивных системах классификации, опознавания, диагностики, идентификации, прогнозирования и управления.

Известны устройства для классификации входных сигналов, содержащие блок пороговых элементов (рецепторов), блок функциональных преобразователей (ассоциативных элементов), блок взвешивания (умножение на константу), настройка которого осуществляется в режиме адаптации, сумматор и рещающий элемент. Примерами таких устройств являются перцептрон и его модификации.

Недостатком известных устройств является необходимость выбора и настройки структуры функциональных преобразователей с учетом специфики рещаемой задачи, что требует, как правило, вмещательства конструктора (человека-оператора), приводит к громоздким техническим рещениям, снижает быстродействие, автономность и универсальность этих устройств.

Другим недостатком известных устройств является то, что в них не заложены требование безошибочности классификации обучающих сигналов и требование целочисленности весов, приводящие к увеличению точности классификации и упрощению устройства. Целью изобретения является построение

устройства, обеспечивающего автоматическое формирование полиномиальных преобразователей и целочисленных весов по многомерным обучающим сигналам и безощибочную классификацию этих сигналов, что позволяет повысить точность классификации, автономность и быстродействие устройства при пониженных требованиях к объему памяти и сложности реализации. Эта цель достигается с помощью

блока полиномиальных преобразователей, формирующего полиномы из п входных двоичных сигналов непосредственно по т обучающим п - мерным сигналам, подаваемым из блока упорядочивания обучаюи1их сигналов, и

блока формирования целочисленных весов, осуществляющего в режиме адаптации вычисление и настройку т целочисленных весов.

Конструктивно это выражается в том, что устройство содержит блок полиномиальных

преобразователей, одни входы которого подключены к выходам блока пороговых элементов, а выходы - ко входа.м блока взвещивания, блок упорядочивания обучающих сигналов, входы которого подключены к выходам

блока пороговых элементов, а выходы - к другим входам блока полиномиальных преобразователей. Входы блока формирования целочисленных весов связаны с выходом сумматора и соответствующими выходами блока

упорядочивания обучающих сигналов, а выходы - с управляющими входами олока взвеши;;ання.

rli входы блока полиномиальных преобразователей подаются п двоичных сигналов с выходов блока входных пороговых элементов и п значений компонент т обучающих многомерных сигналов, поступающих из блока упорядочивания обучающих сигналов, выдающего эти сигналы в порядке возрастания числа ненулевых компонент, а т выходов подключены к входам специального блока целочисленного взвешивания, на входы которого также поступают сигналы принадлежности обучающих сигналов с выходов блока упорядочивания, и сигнал обратной связи с выхода сумматора, т входов которого подключены к т выходам блока целочисленного взвешивания.

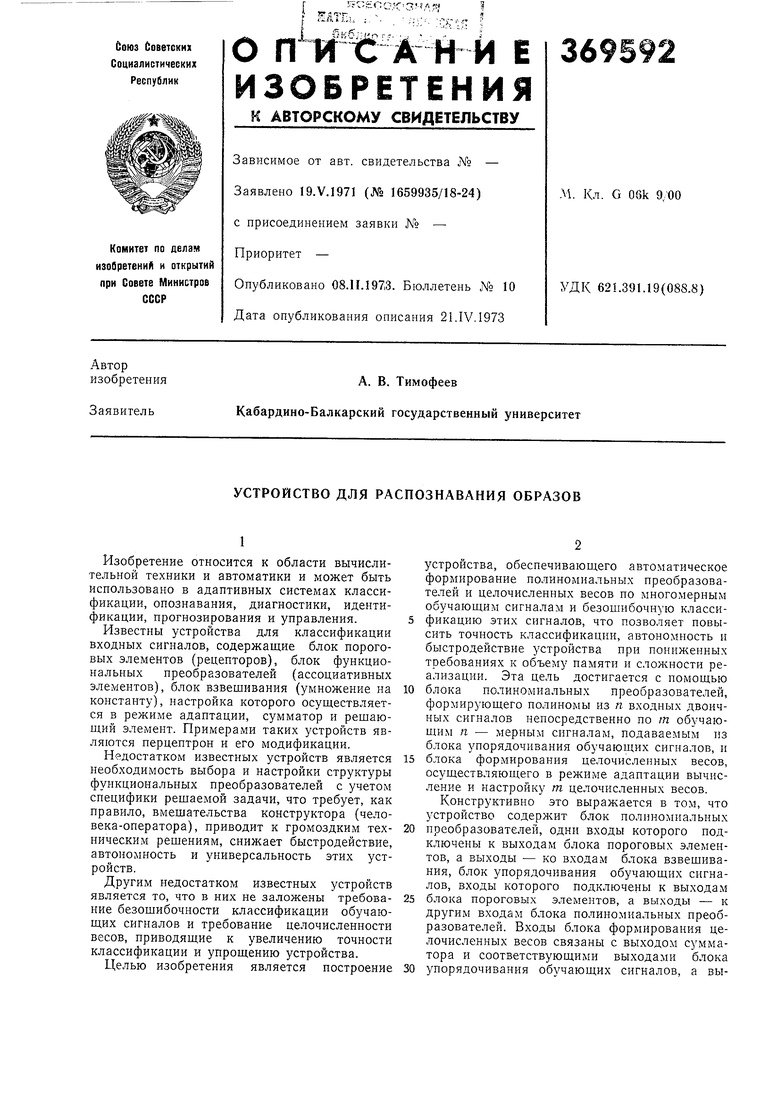

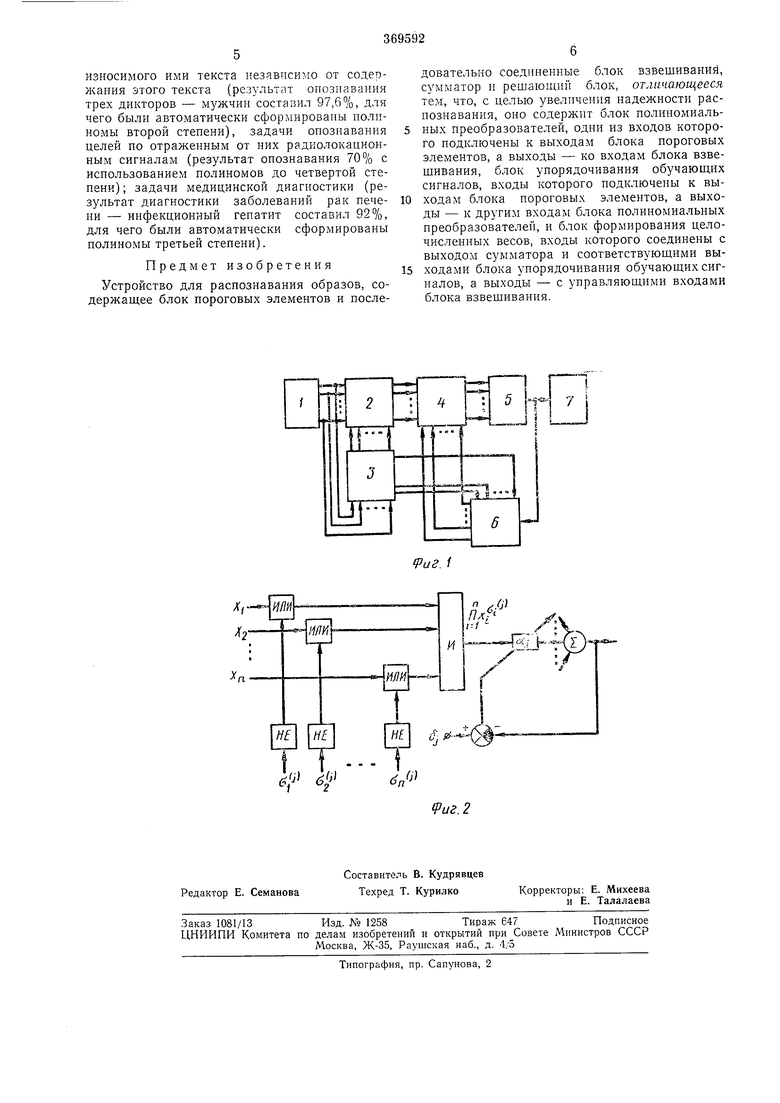

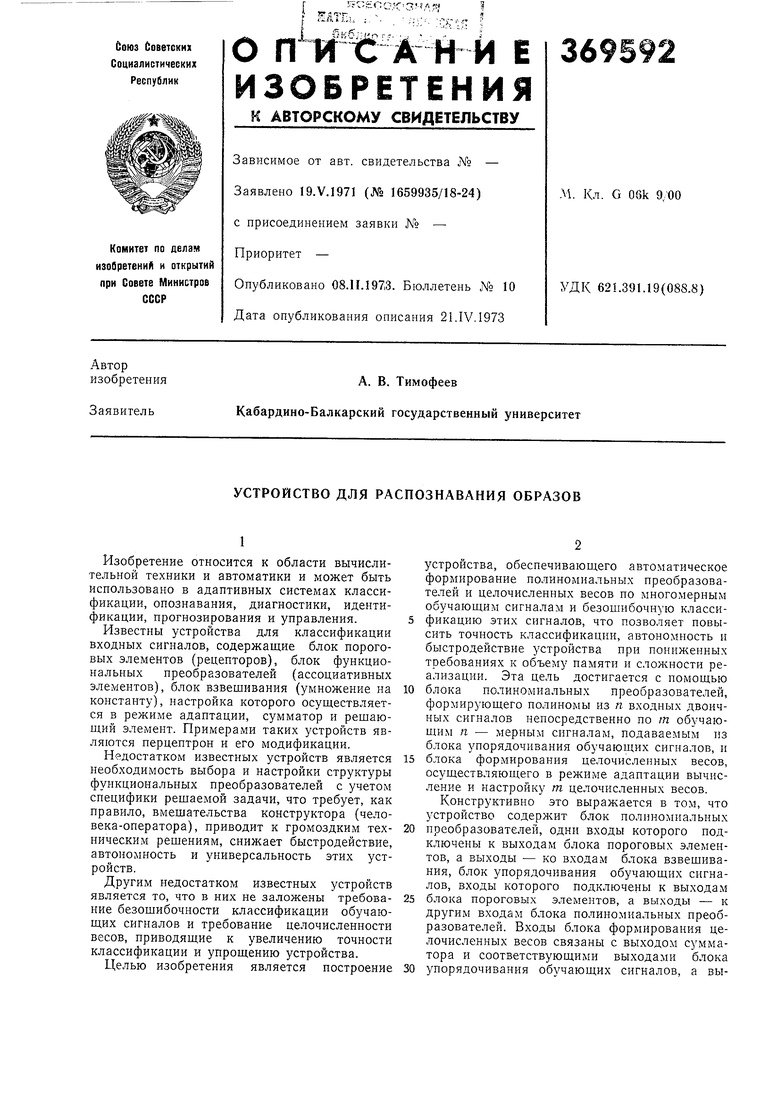

На фиг. 1 показана блок-схема устройства для распознавания образов; на фиг. 2 показан вариант реализации /-го (/ 1,2..., т) канала устройства.

Устройство содержит блок пороговых элементов, блок 2 полиномиальных преобразователей, блок 3 упорядочивания обучающих сигналов, блок 4 взвешивания, сумматор 5, блок 6 формирования целочисленных весов и решающий блок 7.

Блок 1 пороговых элементов соединен с п входами блока 2 полиномиальных преобразователей, пХт остальных входов которого подключены к выходам блока 3 упорядочивания обучающих сигналов, п входов которого соединены с п выходами блока 1, а т выходов блока 2 подключены на т входов блока 4 взвещивания (умножение на константу), т других входов которого соединены с m выходами блока 6 формирования целочисленных весов, (/п+1) входов которого подключены к т выходам блока 5, и к выходу сумматора 5, т выходов которого соединены с т выходами блока 4, а выход подключен ко входу решающего блока 7.

Устройство работает в двух режимах: режим адаптации и рабочий режим.

В режиме адаптации на п входов блока 2 последовательно подаются значения компонент обучающих векторов в порядке возрастания числа ненулевых компонент, пХт остальных входов которого соединены с пХт выходами блока 3, где обучающие векторы хранятся в регистрах, упорядоченных в порядке возрастания числа ненулевых разрядов. Двоичные сигналы с т выходов блока 2 подаются на т входов блока 4, состоящего из т элементов памяти (например, мемисторов, сопротивлений), реализующих значения весов, которые вначале все равны нулю, а в процессе адаптации последовательно настраиваются с помощью блока 6, формирующего на каждом шаге целочисленные значения этих весов по сигналу принадлежности обучающего вектора, поданного на данном шаге на вход блока 2, и но сигналу обратной связи с выхода сумматора 5.

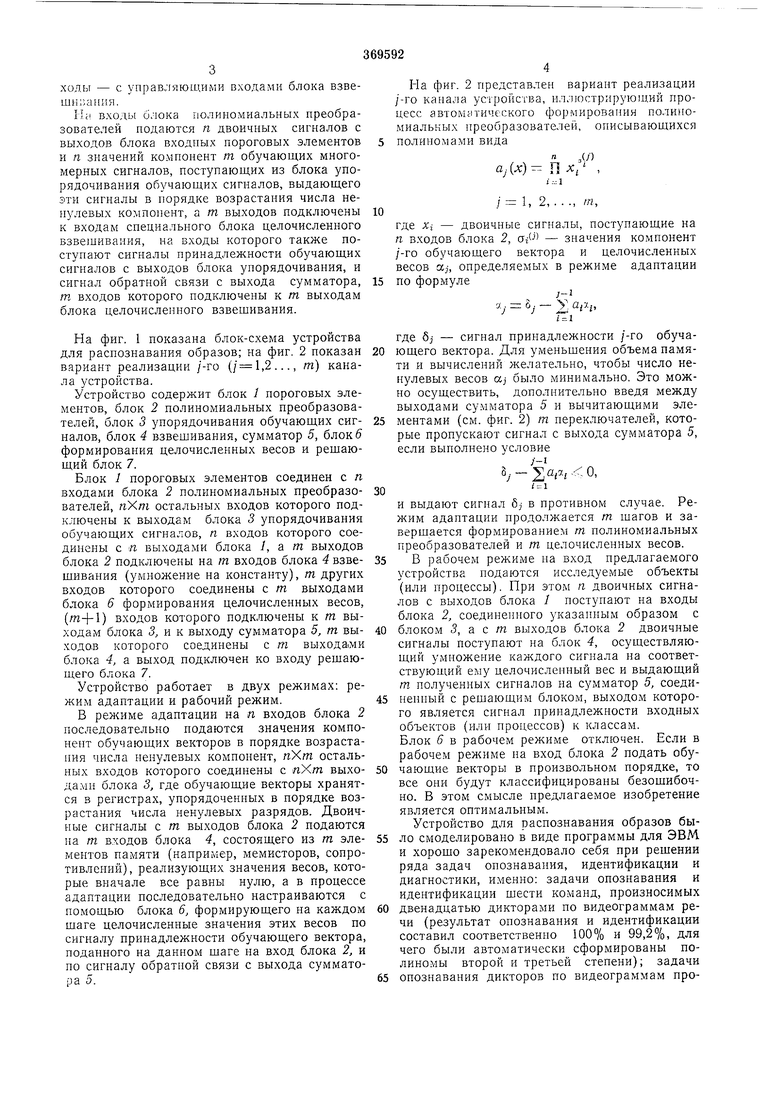

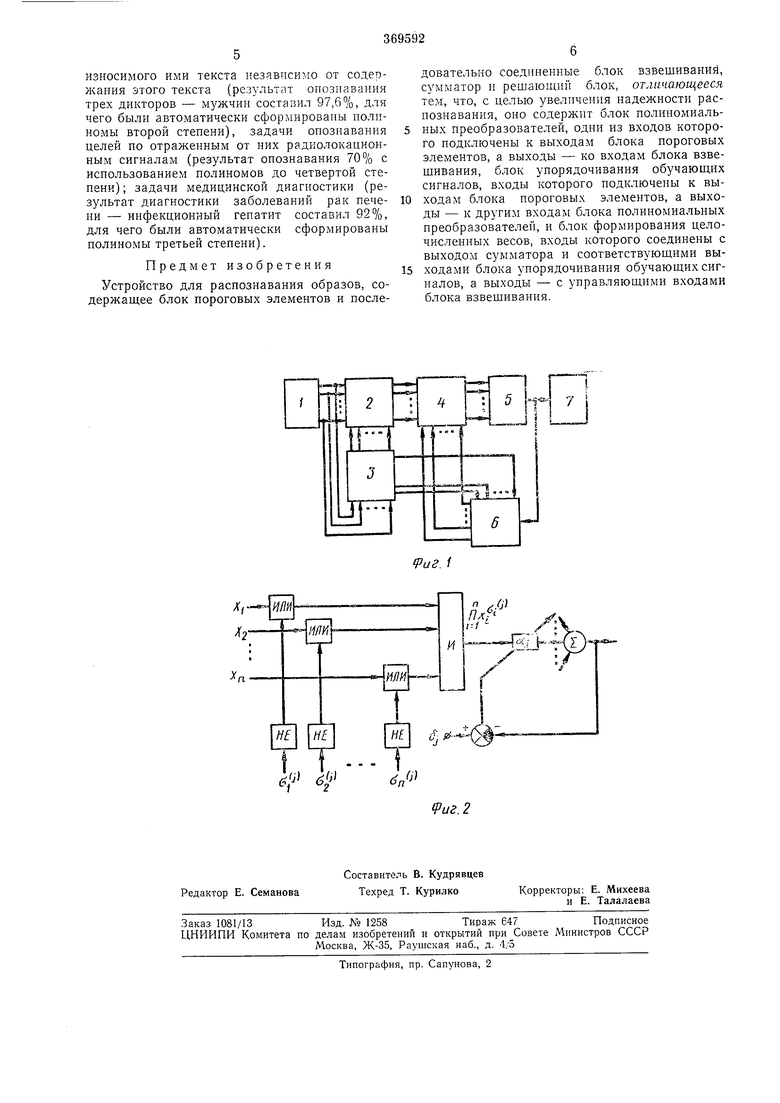

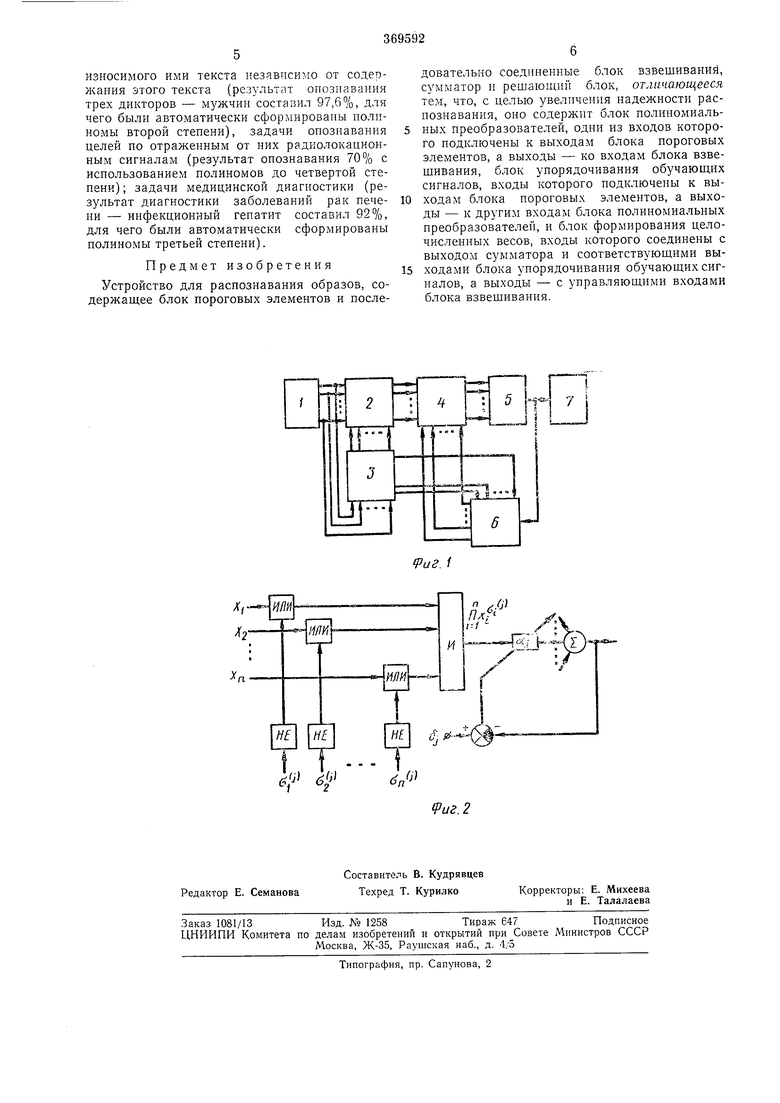

На фиг. 2 представлен вариант реализации /-ГО канала устройства, иллюстрируюш.ий процесс автоматического формирования полиномиальных преобразователей, описывающихся полиномами вида

и ,{/)

uj (х)- и X , 1 1

/ 1, 2, . . ., т,

где Xi - двоичные сигналы, поступающие на п входов блока 2, а/- - значения компонент /-ГО обучающего вектора и целочисленных весов Kj, определяемых в режиме адаптации по формуле

у-1

V / i

где 8 - сигнал принадлежности /-го обучающего вектора. Для уменьшения объема памяти и вычислений желательно, чтобы число ненулевых весов ct,j было минимально. Это можно осуществить, дополнительно введя между выходами сумматора 5 и вычитающими элементами (см. фиг. 2) т переключателей, которые пропускают сигнал с выхода сумматора 5, если выполнено условие

;-2;W - o,

1

и выдают сигнал в противном случае. Режим адаптации продолжается т шагов и завершается формированием m полиномиальных преобразователей и т целочисленных весов.

В рабочем режиме на вход предлагаемого устройства подаются исследуемые объекты (или процессы). Нри этом п двоичных сигналов с выходов блока / поступают на входы блока 2, соединенного указанным образом с

блоком 5, а с m выходов блока 2 двоичные сигналы поступают на блок 4, осуществляющий умножение каждого сигнала на соответствующий ему целочисленный вес и выдающий m полученных сигналов на сумматор 5, соединепный с решающим блоком, выходом которого является сигнал принадлежности входных объектов (или процессов) к классам. Блок 6 в рабочем режиме отключен. Если в рабочем режиме на вход блока 2 подать обучающие векторы в произвольном порядке, то все они будут классифицированы безошибочно. В этом смысле предлагаемое изобретение является оптимальным. Устройство для распознавания образов было смоделировано в виде программы для ЭВМ. и хорошо зарекомендовало себя при решении ряда задач опознавания, идентификации и диагностики, именно: задачи опознавания и идентификации шести команд, произносимых

двенадцатью дикторами по видеограммам речи (результат опознавания и идентификации составил соответственно 100% и 99,2%, для чего были автоматически сформированы полиномы второй и третьей степени); задачи

опознавания дикторов по видеограммам произносимого ими текста независимо от содержания этого текста (результат опознавания трех дикторов - мужчин составил 97,6%, для чего были автоматически сформированы иолиномы второй степени), задачи опознавания целей по отраженным от них радиолокационным сигналам (результат опознавания 70% с использованием цолиномов до четвертой степени); задачи медицинской диагностики (результат диагностики заболеваний рак печени - инфекционный гепатит составил 92%, для чего были автоматически сформированы полиномы третьей степени).

Предмет изобретения

Устройство для распознавания образов, содержащее блок пороговых элементов и последовательно соединенные блок взвешивания, сумматор и решающий блок, отличающееся тем, что, с целью увеличения надежности распознавания, оно содержит блок полиномиальных преобразователей, одни из входов которого подключены к выходам блока пороговых элементов, а выходы - ко входам блока взвешивапия, блок упорядочивания обучающих сигналов, входы которого подключены к выходам блока пороговых элементов, а выходы - к другим входам блока полиномиальных преобразователей, и блок формирования целочисленных весов, входы которого соединены с выходом сумматора и соответствующими выходами блока упорядочивания обучающих сигналов, а выходы - с управляющими входами блока взвешивания.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ГОЛОСОВОЙ ИДЕНТИФИКАЦИИ ДИКТОРА | 2009 |

|

RU2385272C1 |

| СИСТЕМА ИСКАЖЕНИЯ ГОЛОСА ДИКТОРА | 2009 |

|

RU2403627C1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| СПОСОБ ВЕКТОРНОГО КВАНТОВАНИЯ ПАРАМЕТРОВ ЛИНЕЙНОГО ПРЕДСКАЗАНИЯ | 2009 |

|

RU2408088C2 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Адаптивное пороговое устройство | 1979 |

|

SU864525A2 |

| Способ транскрибирования речи по цифровым сигналам с низкоскоростным кодированием | 2023 |

|

RU2801621C1 |

| КОДЕР ДЛЯ КОДИРОВАНИЯ АУДИОСИГНАЛА, СИСТЕМА ПЕРЕДАЧИ АУДИО И СПОСОБ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ КОРРЕКЦИИ | 2014 |

|

RU2643646C2 |

| СПОСОБ ГИБРИДНОЙ ГЕНЕРАТИВНО-ДИСКРИМИНАТИВНОЙ СЕГМЕНТАЦИИ ДИКТОРОВ В АУДИО-ПОТОКЕ | 2013 |

|

RU2530314C1 |

| СПОСОБ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2014 |

|

RU2541905C1 |

k /

| 7

Авторы

Даты

1973-01-01—Публикация