Изобретение относится к автоматике и вычислительной технике и может быть применено в управляющих системах и гибридных вычислительных устройствах для вычисления в следящем режиме полиномиальной функции от аналогового аргумента с представлением результата в цифровой форме.

Известно устройство для вычисления полиномиальной функции от аналогового непрерывно-изменяющегося сигнала, содержащее п сумматоров, регистр, элементы И положительного и отрицательного приращений, вычитающей узел, пороговый элемент, нуль-орган и распределитель импульсов.

Недостатком этого устройства является низкое быстродействие и ограниченный частотный диапазон обрабатываемых сигналов.

Известен также электронный функциональный генераторе цифровым управлением, содержащий блок памяти, интерполятор, компаратор и блок управления.

Недостатками этого устройства являются сложность блока интерполяции и низкое быстродействие.

Известно также устройство для вычисления полиномиальной функции, содержащее п сумматоров, регистр, п групп элементов И-ИЛИ и распределитель им- пульсоь, которое совместно со следящим аналого-цифровым преобразователем, имеющим в сеоем составе реверсивный счетчик, цифроаналоговый преобразователь, вычитающий узел, пороговый элемент, нуль- орган и генератор импульсов, позволяет вычислять Функцию от аналоговой величины в следящем режиме.

XI

ы

V4

Ь Јь

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому является устройство для вычисления полиномиальной функции, содержащее вычитающий узел, цифроаналоговый преобразователь, сумматор аргумента, приоритетный блок, блок пороговых элементов нуль-орган, п (где п - степень полиномиальной функции блоков сдвига), п сумматоров, п сумматоров приращений, шифратор, два коммутатора, приоритетный шифратор, дешифратор, блок памяти коэффициентов, блок сдвига когда функции, сумматор функции и блок синхронизации.

Недостатком устройства-прототипа является сложность и большие аппаратурные затраты.

Для достижения поставленной щели в устройство для вычисления полиномиальной функции от аналогового аргумента, содержащее вычитатель, цифроаналоговый преобразователь, сумматор-вычитатель аргумента, приоритетный блок, группу пороговых элементов, нуль-орган, п блоков сдвига (где п - степень полинома), п сум- маторов-вычитателей функции, шифратор и блок синхронизации, выход первой тактовой последовательности которого соединен с входом стробирования нуль-органа, выход второй тактовой последовательности блока синхронизации соединен с входами стробирования приоритетного блока, сумма- тора-вычитателя аргумента и первого сум- матора-еычитателя функции, выходы с третьей по (-п + 1 )-ю тактовых последовательностей блока синхронизации соединены с входами стробирования соответственно с второго по п-й сумматоров-вычитателей функции, аналоговый вход аргумента устройства соединен с первым входом вы- читателя, выход которого соединен с информационным входом нуль-органа и входами пороговых элементов группы, выходы которых соединены с соответствующими информационными входами приоритетного блока, выход которого соединен с входом шифратора и информационным входом суммато- ра-вычитателя аргумента, выход которого соединен с выходом кода аргумента устройства и входом цифроаналогового поеобра- зователя, выход которого соединен с вторым входом вычитателя. выход нуль-органа соединен с входами управления режимом сумматора-вычитателя аргумента и всех сумматоров-вычитателей функции, выход шифратора соединен с входами управления сдвигом всех блоков сдвига, выходы с первого по n-й блоков сдвига соединены с информационными входами соответствующих сумматоров-вычитателей функции, выходы которых соединены с информационными входами соответственно со второго по n-й блоков сдвига и выходом кода функции

устройства, дополнительно введены блок задания начальных значений и регистр, выход которого соединен с информационным входом первого блока сдвига, причем блок задания начальных значений содержит ге0 нератор импульсов, счетчик, группу элементов, счетчик, группу элементов И, регистр степени, первый и второй блоки памяти, блок умножения и коммутатор, причем вход запуска устройства соединен с первыми

5 входами элементов И группы и входом запуска генератора импульсов, выход которого соединен со входами последовательного считывания первого и второго блоков памяти, управляющим входом коммутатора и

0 счетным входом счетчика, информационный вход которого соединен с выходами элементов И группы, вторые входы которых соединены с выходами соответствующих разрядов регистра степени, выходы

5 первого и второго блоков памяти соединены с соответствующими входами блока умножения, выход которого соединен с информационным входом коммутатора, выход которого соединен с входами начальной ус0 тановки всех суммэторов-вычитателей функции и регистра, выход счетчика соединен с входом останова генератора импульсов и входом запуска блока синхронизации.

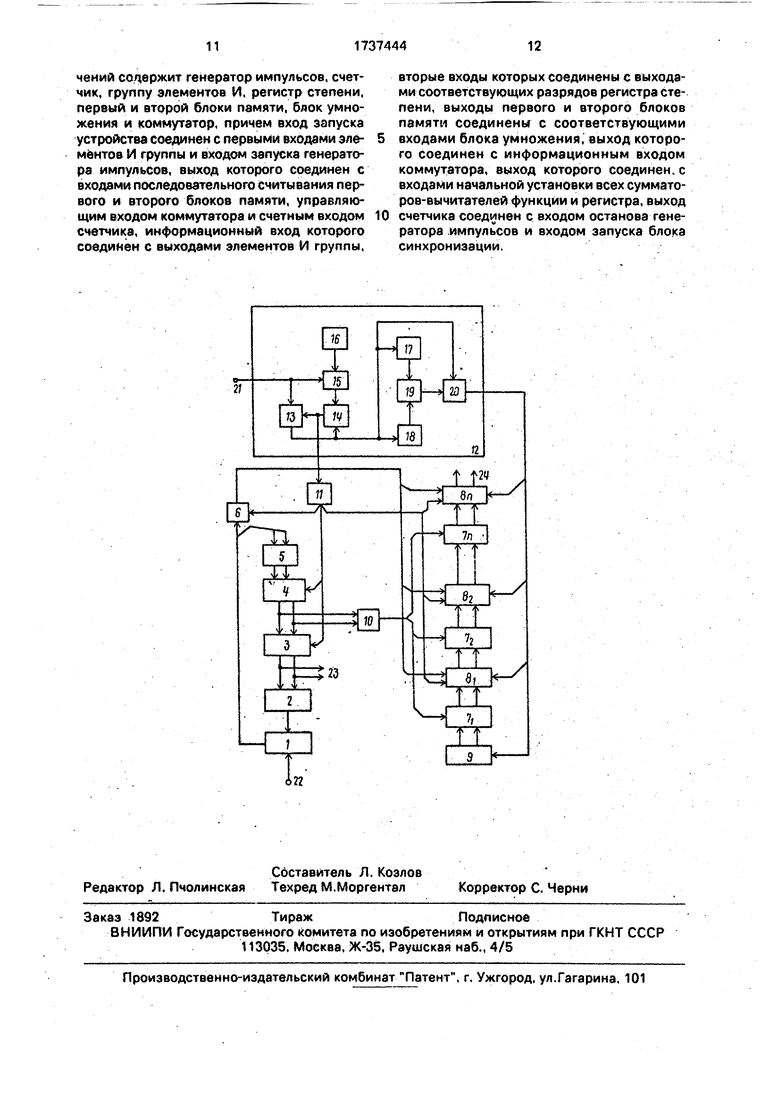

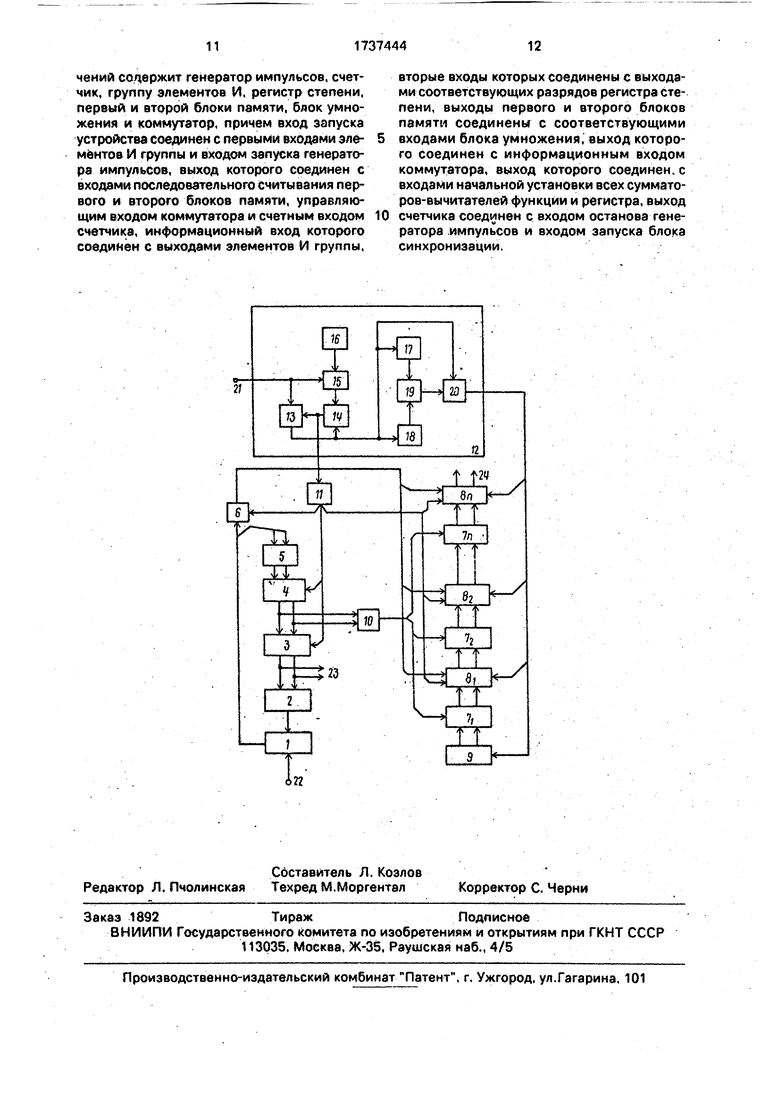

На чертеже приведена схема предлага5 емого устройства.

Устройство для вычисления полиномиальной функции от аналогового аргумента содержит вычитатель 1, цифроаналоговый преобразователь 2, суммэтор-вычитатель

0 аргумента 3, приоритетный блок 4, группу 5 пороговых элементов, нуль орган 6, п блоков сдвига 7 (где п - степень полинома), п сумматоров-вычитателей функции 8, регистр 9, шифратор 10,блок синхронизации 11 и блок

5 задания начальных значений 12.

Блок 12 задания начальных значений содержит генератор 13 импульсов, счетчик 14, группу 15 элементов И, регистр 16 степени, первый 17 и второй 18 блоки памяти,

0 блок 19 умножения и коммутатор 20.

Выход первой тактовой последовательности блока 11 синхронизации соединен с входом стробирования нуль-органа 6, выход второй тактовой последовательности блока

5 11 синхронизации соединен с входами стро бирования приоритетного блока 4 сумматора-вычитателя 3 аргумента и первого сумматора-вычитателя 8 функции, выходы с третьего по (п + 1)-ю тактовых последовательностей блока 11 синхронизации соедийены с входами стробирования соответственное второго по n-й сумматоров-вычислителей 8 функции, аналоговый вход 22 аргумента устройства соединен с первым входом вычитателя 1, выход которого соединен с информационным входом нуль-органа 6 и входами пороговых элементов 5 группы, выходы которых соединены с соответствующими информационным входами приоритетного блока 4, выход которого соединен с входом шифратора 10 и информационным входом сумматора-вычитателя 4 аргумента, выход которого соединен с выходом 23 кода аргумента устройства и входом циф- роаналогового преобразователя 2, выход которого соединен с вторым входом вычитателя 1, выход нуль-органа 6 соединен с входами управления режимом сумматора- вычитателя 3 аргумента и всех сумматоров- вычитателей 8 функции, выход шифратора 10 соединен с входами управления сдвигом всех блоков 7 сдвига, выходы с первого по n-й блоков 7 сдвига соединены с информационными входами соответствующих сум- маторов-вычитателей 8 функции, выходы которых, соединены с информационными входами соответственно с второго по п-й блоков 7 сдвига и выходом 24 кода функции устройства. Выход регистра 9 соединен с информационным входом первого блока 7 сдвига. Вход 21 запуска устройства соединен с первыми в/одами элементов И группы 15 и входом запуска генератора 13 импульсов, выход которого соединен с входами последовательного считывания первого 17 и второго 18 блоков памяти, управляющим входом коммутатора 20 и счетным входом счетчика 14, информационный вход которого соединен с выходами элементов И группы 15, вторые входы которых соединены с выходами соответствующих разрядов регистра 16 степени, выходы первого 17 и второго 18 блоков памяти соединены с соответствующими входами блока 19-умножения, выход которого соединен с информационным входом коммутатора 20, выход которого соединен со входами начальной установки всех сумматоров-вы- читателей 8 функций и регистра 9, выход счетчика 14 соединен с входом остановка генератора 13 импульсов и входом запуска блока 11 синхронизации.

Предлагаемое устройство работает следующим образом.

Для вычисления искомой полиномиальной функции у(х) ао + aix + аах2 + ... + апхл от входного аналогового сигнала х, который подается на аналоговый вход 22 аргумента устройства, перед началом работы устройство устанавливается в исходное состояние, для которого обнуляются сумматор-вычитатель аргумента 3, сумматоры-вычитатепи

функции 8i, 828ц и регистр 9 Кроме того,

в регистр степени 16 блока 12 задания на чальных значений заносится степень п полиномизльной функции, а во второй блок 18 памяти блока 12 заносятся коэффициенты ai полиномиальной функции. Первый блок 17 памяти блока 12 содержит коэффициенты ki(1 I п), предназначенные для вычисле0 ния кодов начальных значений yi(0) полиномиальной функции, задаваемых затем в сумматоры-вычислители функции 8i и регистр 9 и обеспечивающих вычисление искомой попиномиальной функции в режиме

5 слежения за аналоговым значением аргумента х. Коэффициенты ki имеют следующий вид ko 1, : для (1 I п - 1):

KI --, где Сп1 - сочетание из п элементов по

0

г1

п

I, которое определяется по формуле:

Ck

(

П (П - 1)...(П - I + 1)

I)i(i-1)...l

5

0

5

0

5

0

5

При подаче сигнала на вход 21 запуска устройства значение степени п полиномиальной функции заносится в обратном коде с выхода регистра степени 16 через группу 15 элементов И, в счетчик 14 и запускается генератор 13 импульсов, сигналы с выхода которого поступают на управляющие входы блоков первого 17 и второго 18 памяти и производят считывание попарно коэффициентов ki и ai (О S: I л), которые поступают на входы блока 19 умножения на выходе которого формируются последовательно коды произведений ki ai. которые являются начальными значениями yi(0) для заданной функции у. Эти значения yi(0) поступают на вход коммутатора 20, где они под управлением сигналов от генератора импульсов 13 выдаются на соответствующие 1-е выходы блока 12 задания начальных значений. Начальные значения функции yn-i(0) (для п I 1) поступают на входы начальной установки сумматоров-вычитателей функции 8i, а значение уп(0) - на входы регистра 9 и заносятся в эти сумматоры-вычитатели функции 8i и регистр 9 либо последовательно по времени, либо по одному стробирую- щему сигналу начальной установки (в этом случае значения yi(0) вначале записываются на выходные регистры коммутатора 20). поступающему на стробирующие входы начальной установки сумматоров-оычитате- лей функции 8i и регистра 9 (на схеме эти связи не показаны, чтобы не загромождать чертеж, при этом для занесения у(0) может использоваться сигнал с выхода счетчика

14. После вычисления всех значений yi(0) (О I п) на вход счетчика 14 поступает (п + + 1) импульс, этот счетчик 14 вырабатывает сигнал переполнения, который прекращает работу генератора импульсов 13 и поступает с выхода счетчика 14 на вход блока 11 синхронизации. На этом этап предварительных вычислений значений функции yi(0) заканчивается и начинается работа устройства в реальном времени по вычислению значений полиномиальной функции в режиме слежения за аналоговым сигналом х.

Вычитатель 1 определяет разность Ди между входным сигналом х на аналоговом устройстве 22 и напряжением обратной связи с выхода цифроаналогового преобразователя 2, в которое преобразуется код сумматора-вычитателя 3. Напряжение рассогласования прикладывается к входу нуль- органа 6, который определяет его знак, и входам группы 5 пороговых элементов, которые срабатывают при достижении напряжением разности Д и порогов, на которые настроены пороговые элементы по двоичному закону: 1, 2, 4 2 2т условные

единиц, равных весу младшего разряда (где т - количество элементов в группе 5 и количество разрядов в сумматоре-вычитате- ле аргумента 3). При подаче сигнала с выхода счетчика 14 блока 12 на вход запуска блока 11 синхронизации он формирует импульсы тактовой последовательности на своих выходах. По первому импульсу на выходе первой тактовой последовательности блока 11 синхронизации нуль-орган б фиксирует знак напряжения рассогласований, а приоритетный блок 4 выделяет старший из сработавших пороговых элементов группы 5. В следующий момент времени тактовый импульс проходит с выхода второй тактовой последовательности блока 11 синхронизации на стробирующий вход сумматора-вычитателя 3 аргумента и сумматора- вычитателя 8i функции, этот же тактовый импульс проходит также па стробирующие

входы сумматоров вычитателей 8а, 8з8п,

настраивая эти сумматоры-вычитатели на выполнение операции сложения или вычитания, в зависимости от знака напряжения рассогласования Д и. Коды с выхода приоритетного блока 4 представляют собой приращение входного сигнала Дх 2 , округленные до значения кратного степени двойки, эти коды добавляются (в соответствии со знаком на выходе нуль-органа 6, сумматор-вычитатель 3 аргумента настраивается на сложение или вычитание по входу управления режимов, В сумматоре-вычита- теле 3 аргумента формируется цифровой

код хе+1 хе + Д х входного аналогового сигнала х в режиме слежения за этим сигналом. Шифратор 10 осуществляет шифрэцию позиционного двоичного кода приращения

в код номера разряда (k), в котором находится единица. Этот код поступает на входы

блоков 7i, 27П сдвига. В этом же такте

осуществляется добавление к содержимому сумматоров-вычитателей 8i функции

(для i 2, 3, .,., п) кодов из предыдущих сумматоров-вычитателей функции 8м. умноженных на приращение Дх. Вначале, в

сумматорах-вычислителях 8i, 82,.... 818П

содержатся соответственно коды значений

Уп-1

Эп- 1 Л

-, Уп-2

Эп-2 2

п(п-1)

v . ап-г1 2...(1-1), ап-1 Уп n(n-1)...(n-l + 1) cn-iуо ао, а в регистре 9 - код значения уп ап, при этом начальные значения yi(0) для (0 I п) обозначены как yi. Начальное значение

кода аргумента хе хо О содержится в сумматоре-вычитателе 3 аргумента. В первом сумматоре-вычитателе 8i функции, в котором в дальнейшем формируется цифровой код уг 1 + уп х входного сигнала х,

к концу этого такта получается значение кода Уп-1 + Уп Хе + Уп Дх уп-1 + Уп Хе+1. Во

втором сумматоре-вычитателе 8а функции, в котором в дальнейшем формируется цифровой код уп-2 + 2уп-1Х + уп Х2, к концу этого такта получается значение кода (уп-2 + 2yn-i

Хе + уп Хе ) + Уп 1 Д X + упХе Д X, СоотВвТСТвенно в 1-м сумматоре-вычитателе функции 8|, в котором в дальнейшем формируется цифровой код yt ci°yn-i + +ci Уги-их + ci2yn-i+2x2 + ... + crW (где CiJ

TTTi-ГП1 Ci° - С1 1 - биномиальные

J Ч 1Л

коэффициенты, определяемые из так называемого треугольника Паскаля) к концу это- го такта получится код

0-1)2

(Уп-1 + iyn-i+1Xe +

Уп-Н-2Хе + ...

+ УпХе1) + (Уп-i-H + 0 - 1)Уп-1-2Хе + ... + УпХе ) Дх.

При этом умножение кодов yi на приращение Дх производится путем сдвига на блоках сдвига 7 кода yi на k разрядов , вправо. К концу этого-такта во втором сумматоре-вычитателе функции 82 формируется

коя

(Уп-2 + 2уп-1Хе + УпХ е) + Уп-1 Дх + УпХе Д X + уп-1 Д X + упД Х Д X,

т.е. новое значение кода

Уп-2 + 2уп-1Хе+1 + уп .

путем добавления из сумматора-еычитателя функции 8i кода (уп 1 + УпХе + Уп х), умноженного на приращение х на блоке сдвига 72. Аналогично в 1-ом сумматоре-вычитателе 81 к содержащемуся в нем коду

(Уп-1 + Уп-1+1 1хе + ... + УпХе1) + (уп-1-И + + Уп-1+2 (1-1) Хе + ... + УлХ(М Дх

добавляется из предыдущего сумматора- вычитателя 8и функции код

(Уп-1+1 + Уп-1+2(К1)Хе + ... + УпХе0 + (Уп-К2 + Хе +УПХРО.

умноженный с помощью блока 7i сдвига на приращение Ах, то есть формируется код

(Ул-1 + Уп-Н-1 1Хе + ... + УпХе + 2(угИ-И + + Уп-1+2(И)х2 + ... + УпХв1 1) Дх- (Уп-1+2 + Уп-НЗ(1-2)Хе + ... + упХе( 2)) Ах.

В следующем такте под управлением импульса с выхода третьей тактовой последовательности блока 11 синхронизации к содержимому сумматоров-вычитэтелей 8i функции добавляются коды из предыдущих сумматоров-вычитателей 8м функции, умноженные на приращение А х с помощью блоков сдвига 7.

Таким образом, в третьем сумматоре- вычитателе 8з функции (I 3) формируется код

Уп-З + Зуп-2Хе-И + Зуп-1Х е-И + УпХ е+1 .

Если в устройстве содержится три сумматора-вычитателя 8 функции и реализуется полиномиальная функция третьей степени, то на данном такте в сумматоре-вычитателе 8з функции получается искомая функция у(х) ао + aix + а2х2 + азх3. так как уп-з ао,

ai Уп-2 у-Уп-1

32

, УП аз.

На следующих шагах устройство работает аналогично, так что в сумматоре-вычитателе 8п функции - текущий код полинома у(х) в следящем режиме за аналоговым сигналом х, поступающим на аналоговый вход 22 устройства. При этом приращения Ах на каждом шаге могут существенно превосходить значения младшего разряда и увеличиваться вплоть до старшего разряда , такие приращения обрабатываются в предлагаемом устройстве также за (п + 1) тактов.

Максимальная частота сигналов, обрабатываемых в следящем режиме устройством, затрачивающим на каждом шаге (п + 1) такта, определяется выражением вида:

f

ITH

(Гц),

гмакс (п + 1)-2я где т™ - частота следования тактовых импульсов;

- вес старшего значащего разряда,

что при т™ Ю МГц, п - 10 составляет

с1-106-0,5 сп г

Рмакс° 11-6.28 50кГЧ- что позволяет использовать устройство в системах реального времени.

10

Формула изобретения Устройство для вычисления полиномиальной функции от аналогового аргумента, содержащее вычитатель, цифрозналоговый преобразователь, сумматор-вычитатель аргумента-, приоритетный блок, группу пороговых элементов, нуль-орган, я блоков

сдвига (где п - степень полинома), и сумматоров-вычитателей функции, шифратор и блок синхронизации, выход первой тактовой последовательности которого соединен с входом стробирования нуль-органа, выход второй тактовой последовательности блока синхронизации соединен с входами стробирования приоритетного блока, сум- матора-вычитателя аргумента и первого сумматора-вычитателя функций, выходы с

5 третьей по (п + 1)-ю тактовых последовательностей блока синхронизации соединены с входами стробирования соответственно с второго по n-й сумматоров-вычитателей функции, аналоговый вход аргумента уст ройства соединен с первым входом вычита- теля, выход которого соединен с информационным входом нуль-органа и входами пороговых элементов группы выходы которых соединены с соответствующими

5 информационными входами приоритетного блока, выход которого соединен с входом шифратора и информационным входом сумматора-вычитателя аргумента, выход которого соединен с выходом кода аргумента

устройства и входом цифроаналогового преобразователя, выход которого соединен с вторым входом вычитателя, выход нуль-органа соединен с входами управления режимом сумматора-вычитателя аргумента и всех сумматоров-вычитателей функции, выход шифратора соединен с входами управления сдвигом псех блоков сдвига, выход с первого по л-й блоков сдвига соединены с информационными входами

соответствующих сумматоров-вычитателей функции, выходы которых соединены с информационными входами соответственно со второго по n-й блоков сдвига и выходом кода функции устройства, отличающее5 с я тем, что, с целью упрощения устройства, оно содержит блок задания начяльных значений и регистр, выход которого соединен с информационным входом первого блока сдвига, причем блок задания начальных зиачений содержит генератор импульсов, счетчик, группу элементов И. регистр степени, первый и второй блоки памяти, блок умножения и коммутатор, причем вход запуска устройства соединен с первыми входами элементов И группы и входом запуска генератора импульсов, выход которого соединен с входами последовательного считывания первого и второго блоков памяти, управляющим входом коммутатора и счетным входом счетчика, информационный вход которого соединён с выходами элементов И группы,

вторые входы которых соединены с выходами соответствующих разрядов регистра степени, выходы первого и второго блоков памяти соединены с соответствующими входами блока умножения, выход которого соединен с информационным входом коммутатора, выход которого соединен, с входами начальной установки всех суммато- ров-вычитателей функции и регистра, выход счетчика соединен с входом останова генератора импульсов и входом запуска блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

Изобретение относится к вычислительной технике и может быть применено как специализированное устройство в системах обработки информации реального времени Целью изобретения является упрощение устройства. Устройство содержит вычитатель, цифроаналоговый преобразователь, сумма- тор-вычитатель аргумента, приоритетный блок, группу пороговых элементов, нуль-орган, блоки сдвига, сумматоры-вычитатели функции, регистр, шифратор, блок задания начальных значений. Упрощение устройства обеспечивается путем обработки на каждом шаге слежения за входным сигналом его двоично-кодированных приращений. 1 ил.

| Устройство для вычисления полиномов | 1975 |

|

SU556446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-05-30—Публикация

1990-01-08—Подача