1

Предлагаемое изобретение относится к запоминающим устройствам и предназначено для использования во всевозможных вычислительных управляющих системах.

Известны запоминающие устройства с совпадением сигналов, содержащие Z однотипных матриц запоминающих элементов, каждый из которых прошит /С щинами, принадлежащими одной из К. систем ортогональных прощивок.

Целью предлагаемого изобретения является увеличение отношения сигнал/помеха а- и уменьшение числа управляющих щин.

Согласно изобретению поставленная цель достигается тем, что однотипные прошивки запоминаюших матриц соединены параллельно со сдвигом от матрицы к матрице Zj на величину ,(/ - 1), где /С-номер прошивки и 1.

Рассматривается запоминающее устройство на плоских платах с , при том же количестве дещифрирующих шин объем памяти может быть XoYoZo, где .

При повторении каждой из конфигураций последовательного соединения плат т раз получается запоминающее устройство для хранения ХоУо о-т-разрядных слов.

Число прощивок /С, которое может быть взято для реализации такого запоминающего устройства пр.и , составляет /(/Стах.

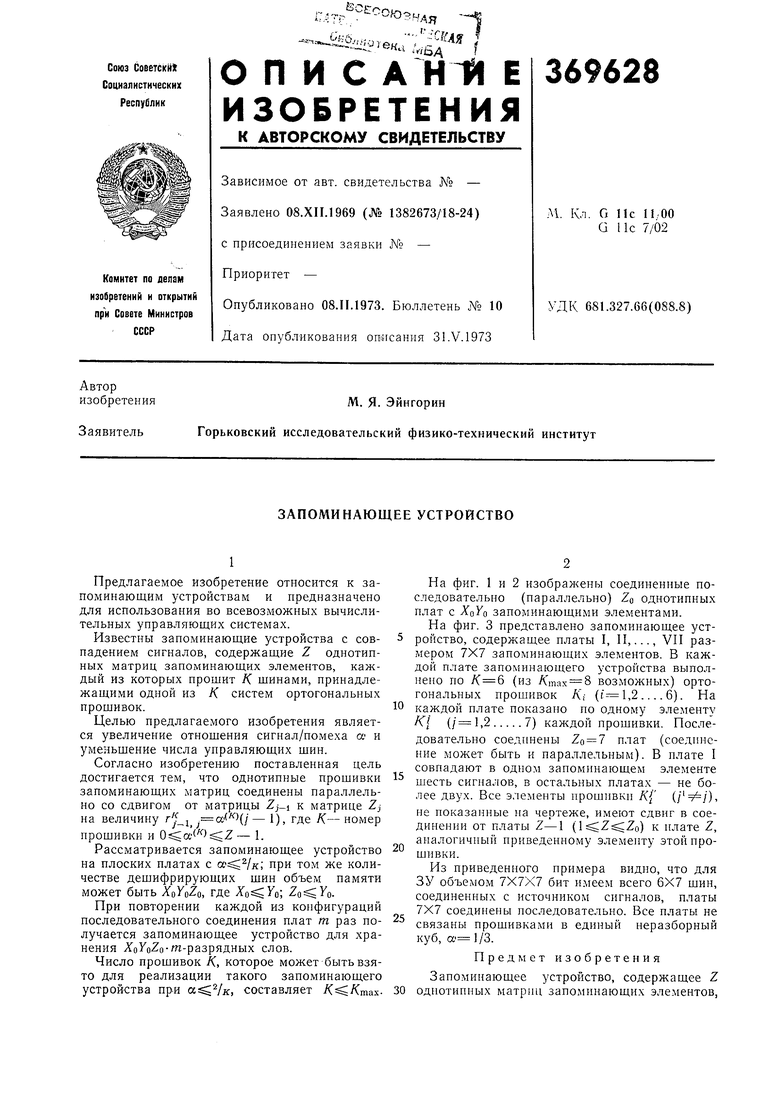

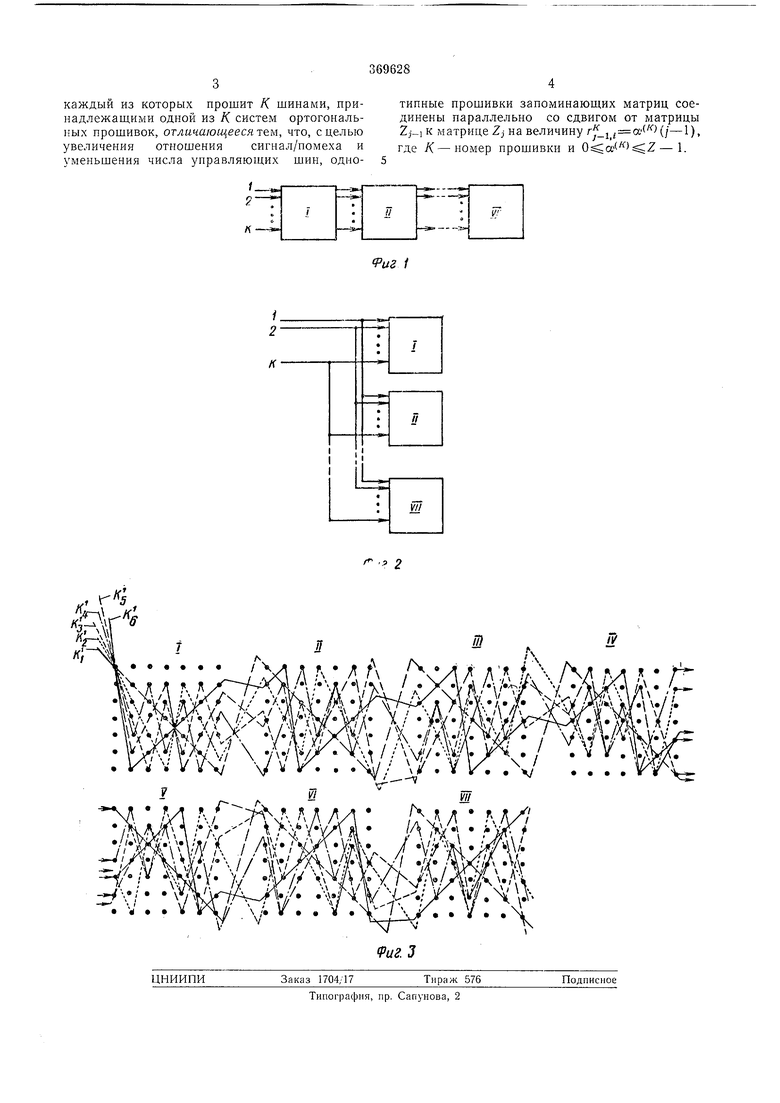

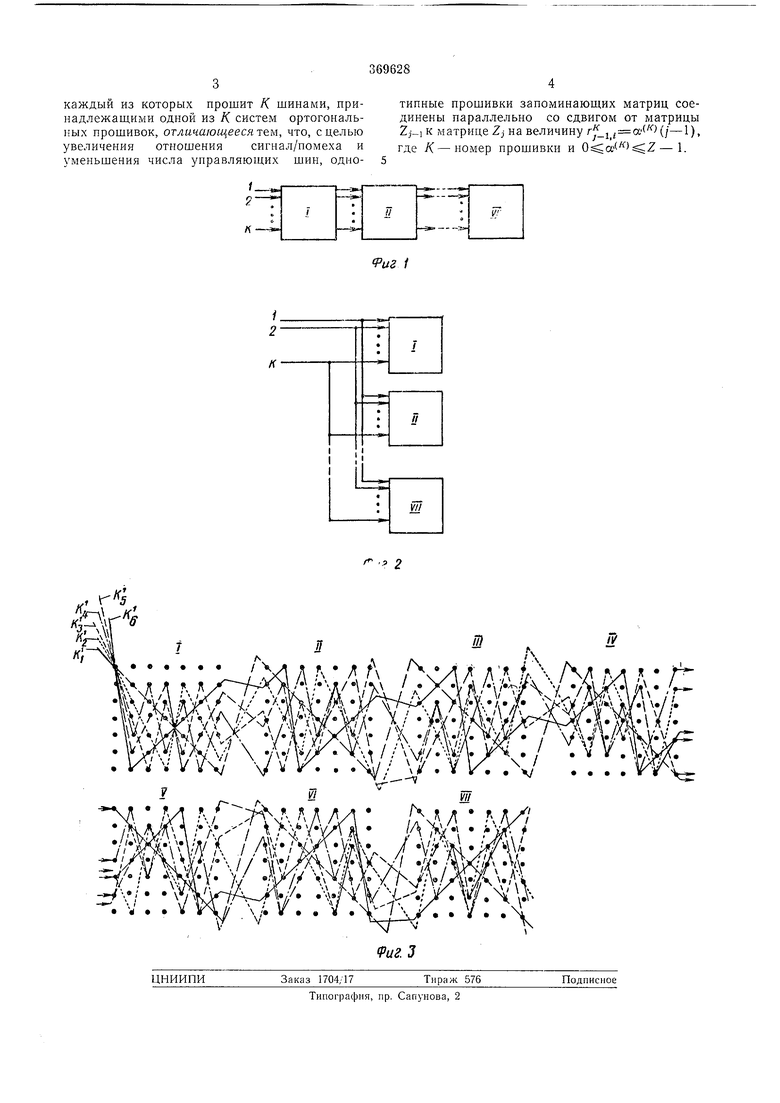

На фиг. 1 и 2 изображены соединенные последовательно (параллельно) Zo однотипных плат с X(tY(, запоминающими элементами.

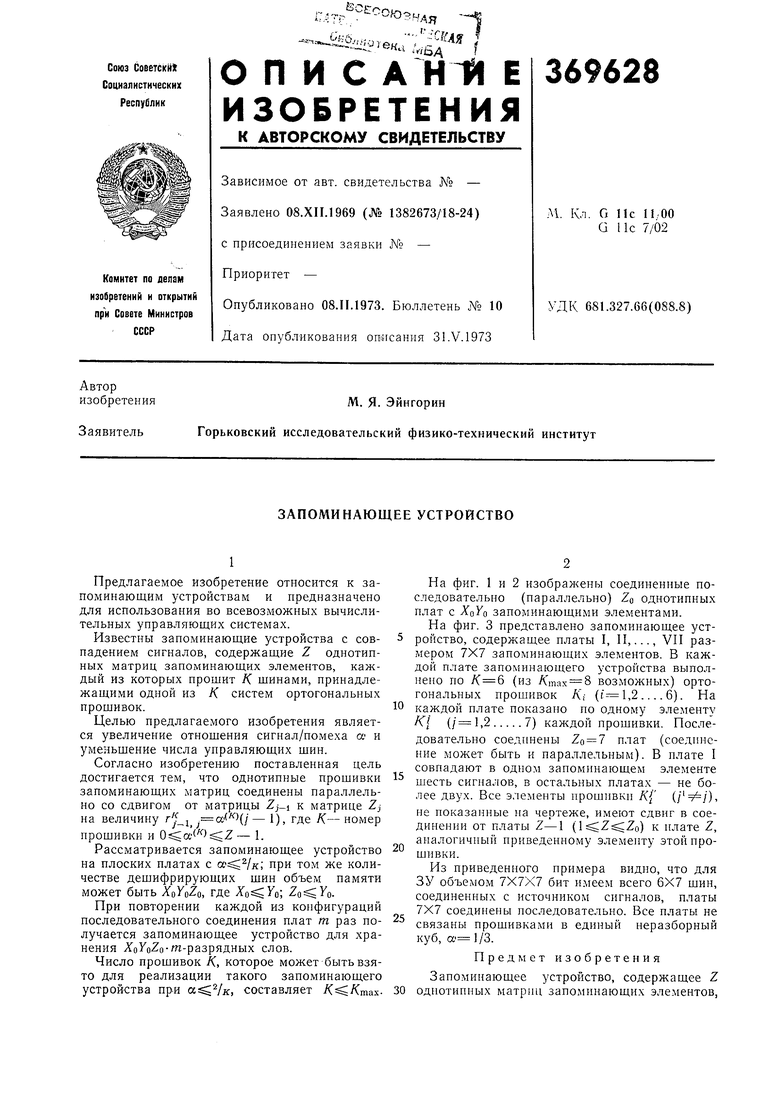

На фиг. 3 представлено запоминающее устройство, содержащее платы I, II,..., VII размером 7X7 запоминающих элементов. В каждой плате запоминающего устройства выпо.чнено но (из Дтах 8 возможных) ортогональных нрошивок Ki (i,2 ... .6). На каждой плате показано по одному элементу К- (,27) каждой прошивки. Последовательно соединены Zo 7 плат (соединение может быть и параллельным). В плате I совпадают в одном запоминающем элементе шесть сигналов, в остальных платах - не более двух. Все элементы прошивки К{ () не показанные ita чертеже, имеют сдвиг в соединении от платы Z-1 () к плате Z, аналогичный приведенному элементу этойпрощивки.

Из приведенного примера видно, что для ЗУ объемом 7X7X7 бит имеем всего 6X7 шин, соединенных с источником сигналов, платы 7X7 соединены последовательно. Все платы не связан1з прошивками в единый неразборный куб, .

Предмет изобретения

Запоминающее устройство, содержащее Z 0 однотипных матр1Н1 запоминающих элементов, 3 каждый из которых прошит К шинами, принадлежашими одной из К систем ортогональных прошивок, отличающееся тем, что, сделыо увеличения отношения сигнал/помеха и уменьшения числа управляющих шин, одно-5

4 типные прошивки запоминающих матриц соединены параллельно со сдвигом от матрицы к матрице Zj на величину (af M/-1) где Д - номер прошивки и .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многомерное матричное селектирующее устройство | 1987 |

|

SU1481853A1 |

| Многомерный дешифратор | 1987 |

|

SU1631730A1 |

| Многомерный накопитель для запоминающего устройства | 1980 |

|

SU1043740A1 |

| Многомерное устройство выборки | 1987 |

|

SU1430988A1 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Способ и устройство определения угловой ориентации летательных аппаратов | 2020 |

|

RU2740606C1 |

| МАГНИТНОЕ АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU215266A1 |

| Многоканальный коррелятор | 1978 |

|

SU752352A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Адаптивная антенная решетка | 1990 |

|

SU1732408A1 |

Авторы

Даты

1973-01-01—Публикация