Изобретение относится к вычислительной технике, а именно к устройствам преобразования кодов, и может быть использовано для селекции многомерных матричных цифровых устройств, система адресных шин которых организована по многомерному принципу.

Целью изобретения является расширение области использования многомерного дешифратора за счет осуществления функции многомерной селекции.

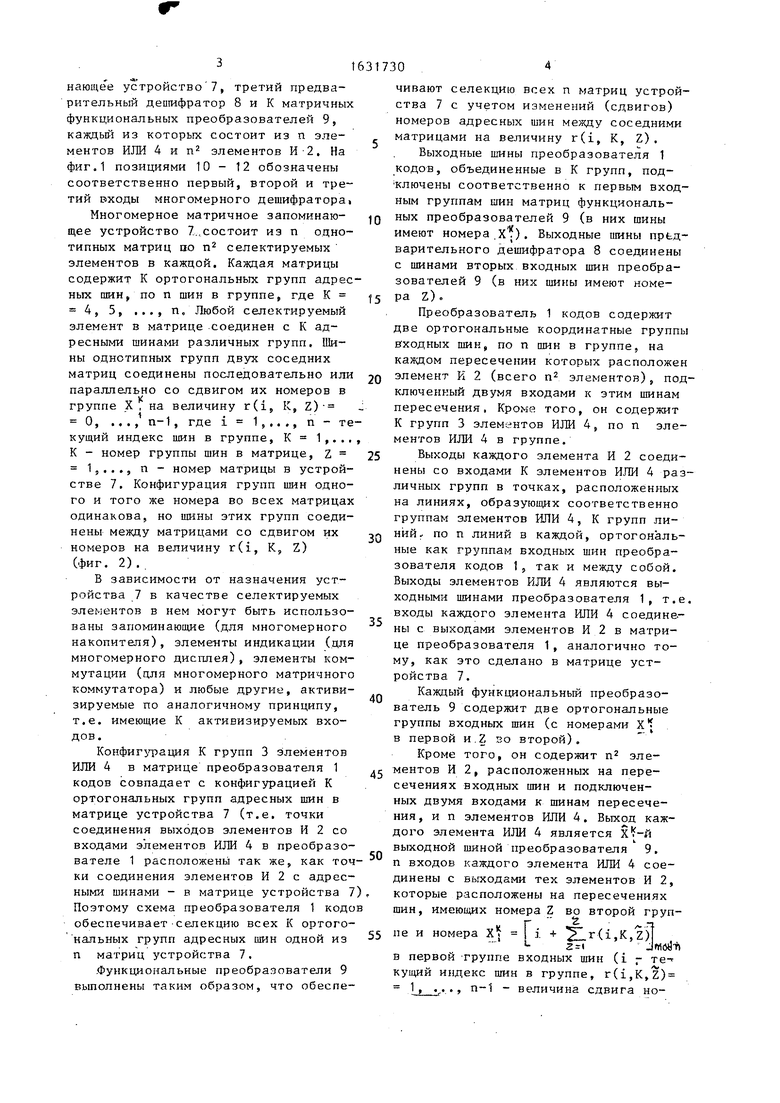

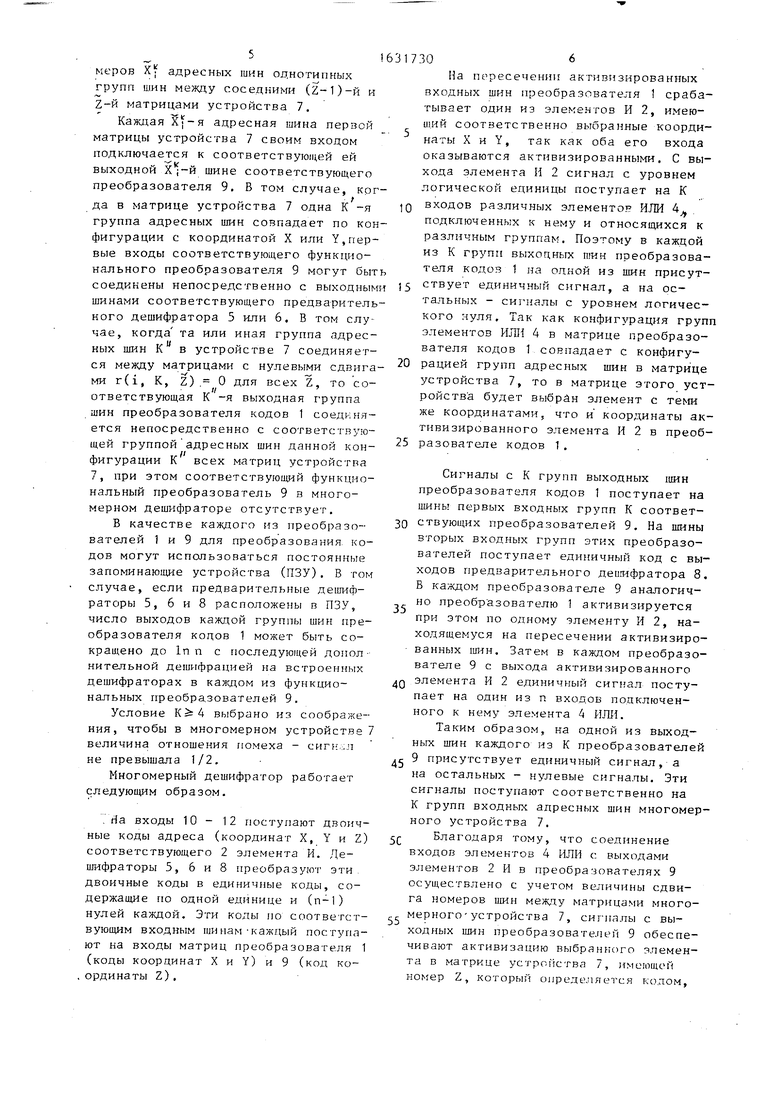

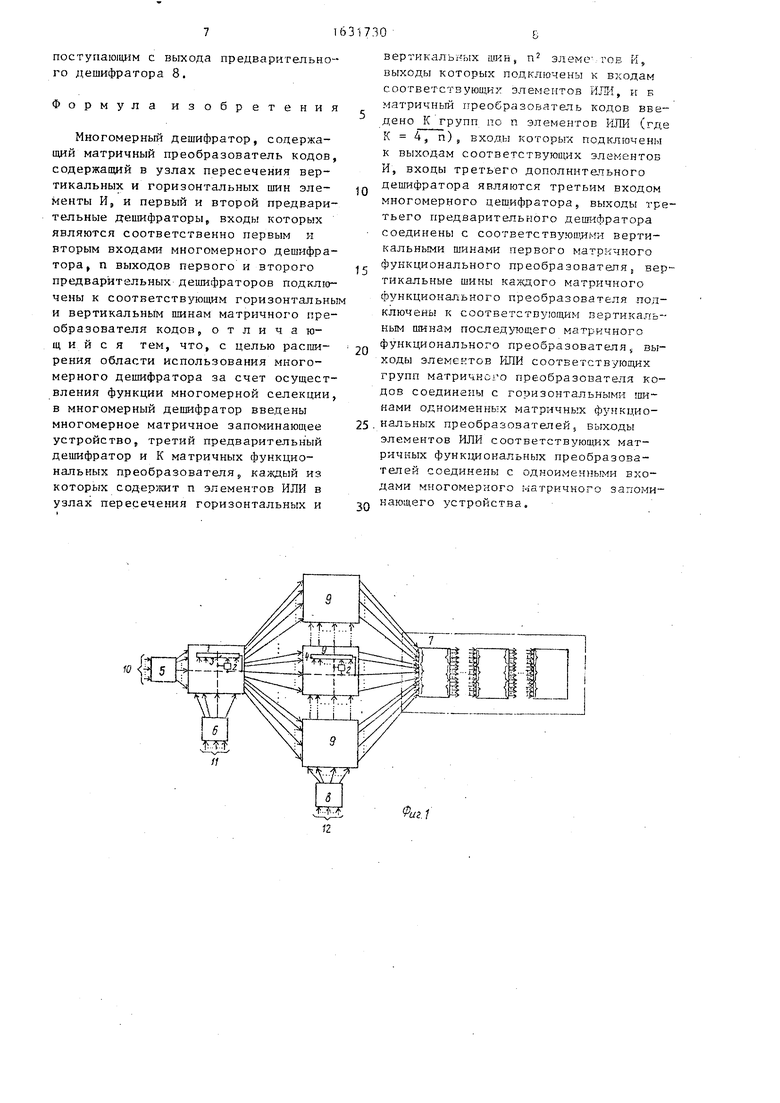

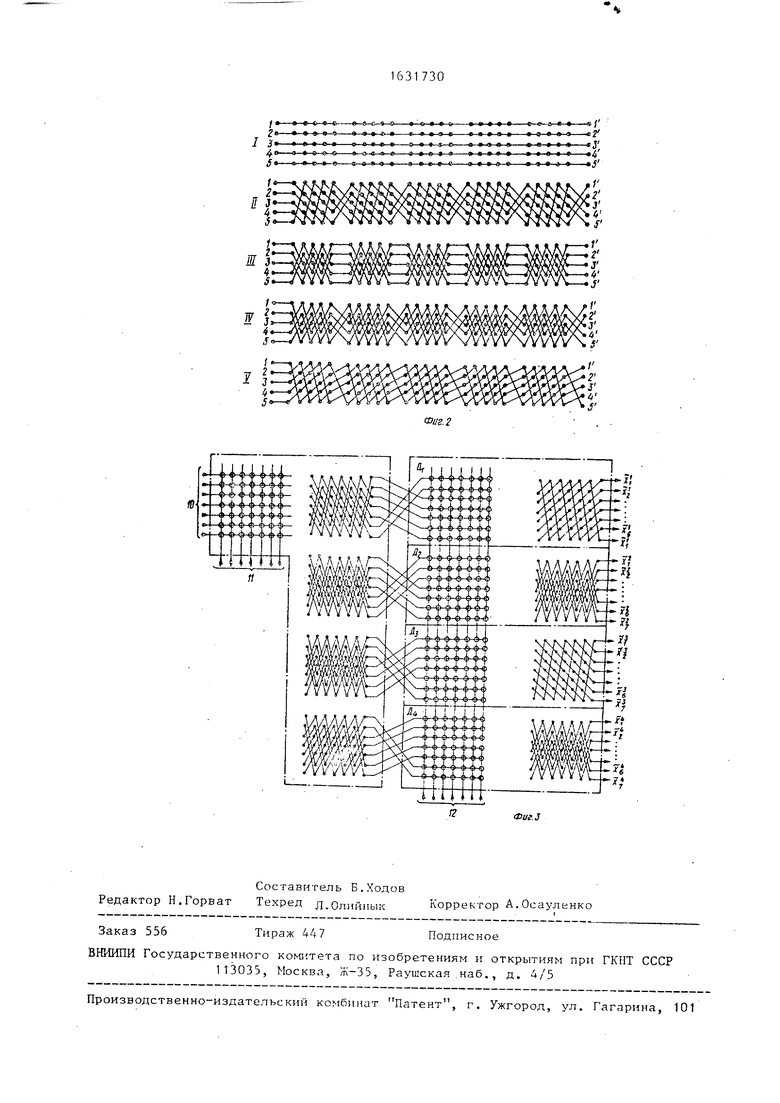

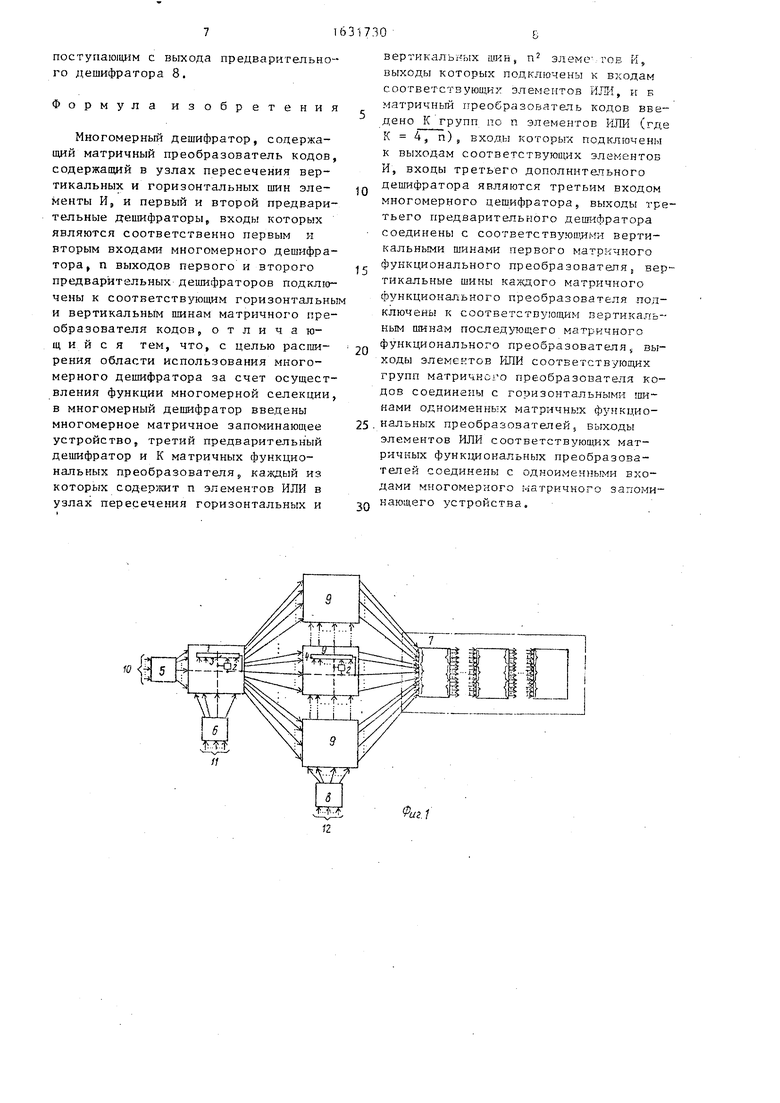

На фиг.1 приведена функциональная схема многомерного дешифратора; на фиг.2 - варианты конфигурации каждой из К групп адресных шин (К 5, ), соединенных с элементами всех п матриц многомерного матричного запоминающего устройства, на фиг.З - пример реализации многомерного дешифратора для селекции многомерного мат)ричного запоминающего устройства с параметрами п 7, К 5 и сдвигами номеров шин однотипных групп: r(i, I, Z) 1 ; r(i, 2, z) 3; r(i, 3,Z)6, r(i,4,Z)3 п r(i,4,Z)3

для , 2, . . .7, Z 1, . . .7,

Многомерный дешифратор содержит матричный преобразователь 1 кодов, состояпщй из элементов И 2 и К групп 3 по п элементов ИЛИ 4, первый и второй предварительные дешифраторы 5 и 6, многомерное матричное запоми&

го

ОЭ

нающее устройство 7, третий предварительный дешифратор 8 и К матричных функциональных преобразователей 9, каждый из которых состоит из п элементов ИЛИ 4 и п2 элементов И 2. На фиг.1 позициями 10 - 12 обозначены соответственно первый, второй и третий входы многомерного дешифратора. Многомерное матричное запоминающее устройство 7 состоит из п однотипных матриц по п2 селектируемых элементов в каждой. Каждая матрицы содержит К ортогональных групп адресных шин, по п шин в группе, где К 4, 5, ..., п„ Любой селектируемый элемент в матрице соединен с К адресными шинами различных групп. Шины однотипных групп двух соседних матриц соединены последовательно или параллельно со сдвигом их номеров в группе X , на величину r(i, К, Z) 0, ., . ,1 п-1, где i 1 , .. ., п - текущий индекс шин в группе, К 1,... К - номер группы шин в матрице, Z 1, . . ., п - номер матрицы в устройстве 7. Конфигурация групп шин одного и того же номера во всех матрицах одинакова, но шины этих групп соединены между матрицами со сдвигом их номеров на величину r(i, К, Z) (фиг. 2).

В зависимости от назначения устройства 7 в качестве селектируемых элементов в нем могут быть использованы запоминающие (цля многомерного накопителя), элементы индикации (цля многомерного дисплея), элементы коммутации (цля многомерного матричного коммутатора) и любые другие, активизируемые по аналогичному принципу, т.е. имеющие К активизируемых входов.

Конфигурация К групп 3 элементов ИЛИ 4 в матрице преобразователя 1 кодов совпадает с конфигурацией К ортогональных групп адресных шин в матрице устройства 7 (т.е. точки соединения выходов элементов И 2 со входами элементов ИЛИ 4 в преобразователе 1 расположены так же, как точки соединения элементов И 2 с адресными шинами - в матрице устройства 7 Поэтому схема преобразователя 1 кодо обеспечивает селекцию всех К ортогональных групп адресных шин одной из п матриц устройства 7.

Функциональные преобратователи 9 выполнены таким образом, что обеспе

5

0

5

0

5

0

5

0

чивают селекцию всех п матриц устройства 7 с учетом изменений (сдвигов) номеров адресных шин между соседними матрицами на величину r(i, К, Z).

Выходные шины преобразователя 1 кодов, объединенные в К групп, подключены соответственно к первым входным группам шин матриц функциональных преобразователей 9 (в них шины имеют номера X). Выходные шины предварительного дешифратора 8 соединены с шинами вторых входных шин преобразователей 9 (в них шины имеют номера Z).

Преобразователь 1 кодов содержит две ортогональные координатные группы Входных шин, по п шин в группе, на каждом пересечении которых расположен элемент К 2 (всего п2 элементов), подключенный двумя входами к этим шинам пересечения. Кроме того, он содержит К групп 3 элементов ИЛИ 4, по п элементов ИЛИ 4 в группе.

Выходы каждого элемента И 2 соединены со входами К элементов ИЛИ 4 различных групп в точках, расположенных на линиях, образующих соответственно группам элементов ИЛИ 4, К групп линий- по п линий в каждой, ортогональные как группам входных шин преобразователя кодов 1, так и между собой. Выходы элементов ИЛИ 4 являются выходными шинами преобразователя 1, т.е. входы каждого элемента ИЛИ 4 соединены с выходами элементов И 2 в матрице преобразователя 1, аналогично тому, как это сделано в матрице устройства 7.

Каждый функциональный преобразователь 9 содержит две ортогональные группы входных шин (с номерами X в первой и Z зо второй).

Кроме того, он содержит п2 элементов И 2, расположенных на пересечениях входных шин и подключенных двумя входами к шинам пересечения , и п элементов ИЛИ 4. Выход каждого элемента ИЛИ 4 является выходной шиной преобразователя 9. п входов каждого элемента ИЛИ 4 соединены с выходами тех элементов И 2, которые расположены на пересечениях шин, имеющих номера Z во второй груп5 е

и номера X М + L.r(i,K,Z)

L 2rlJl

wed-ft

в первой группе входных шин (i г те-« кущий индекс шин в группе, r(i,K,Z) 1, v. ., n-1 - величина сдвига но

5

меров X адресных шин однотипных групп шин между соседними (2-1)-й и Z-й матрицами устройства 7.

Каждая адресная шина первой матрицы устройства 7 своим входом подключается к соответствующей ей выходной шине соответствующего преобразователя 9. В том случае, когда в матрице устройства 7 одна К -я группа адресных шин совпадает по конфигурации с координатой X или Y,первые входы соответствующего функционального преобразователя 9 могут быт соединены непосредственно с выходным шинами соответствующего предварительного дешифратора 5 или 6. В том слу чае, когда та или иная группа адресных шин Ки в устройстве 7 соединяется между матрицами с нулевыми сдвига ми r(i, К, Z) 0 для всех Z, то соответствующая К -я выходная группа шин преобразователя кодов 1 соединяется непосредственно с соответствующей группой адресных шин данной конфигурации К всех матриц устройства 7, при этом соответствующий функциональный преобразователь 9 в многомерном дешифраторе отсутствует.

В качестве каждого из преобразо- вателей 1 и 9 для преобразования кодов могут использоваться постоянные запоминающие устройства (ПЗУ). В гом случае, если предварительные дешиго- раторы 5, 6 и 8 расположены в ПЗУ, число выходов каждой группы шин преобразователя кодов 1 может быть сокращено до In n с последующей допол нительной дешифрацией на встроенных дешифраторах в каждом из функцио- нальных преобразователей 9.

Условие выбрано из соображения, чтобы в многомерном устройстве 7 величина отношения помеха - сигн .л не превышала 1/2.

Многомерный дешифратор работает следующим образом.

ria входы 10 - 12 поступают двоичные коды адреса (координат X, Y и Z) соответствующего 2 элемента И. Дешифраторы 5, 6 и 8 преобразуют эти двоичные коды в единичные коды, содержащие по одной единице и (п-1) нулей каждой. Эти колы по соотвегст- вующим входным шинам-каждый поступают на входы матриц преобразователя 1 (коды координат X и Y) и 9 (код ко- .ординаты Z),

5

7

0 5

0 5 0

5

C 5

306

На пересечении активизированных входных шин преобразователя 1 срабатывает один из элементов И 2, имеющий соответственно выбранные координаты X и Y, так как оба его входа оказываются активизированными. С выхода элемента И 2 сигнал с уровнем логической единицы поступает на К входов различных элементор ИЛИ 4 подключенных к нему и относящихся к различным группам. Поэтому в кажцой из К групп выходных шин преобразователя кодов 1 на одной из шин присутствует единичный сигнал, а на остальных - сигналы с уровнем логического нуля. Так как конфигурация групп элементов ИЛИ 4 в матрице преобразователя кодов 1 совпадает с конфигурацией групп адресных шин в матрице устройства 7, то в матрице этого устройства будет выбран элемент с теми же координатами, что и координаты активизированного элемента И 2 в преобразователе кодов 1.

Сигналы с К групп выходных шин преобразователя кодов 1 поступает на шины первых входных групп К соответствующих преобразователей 9. На шины вторых входных групп этих преобразователей поступает единичный код с выходов предварительного дешифратора 8.

8каждом преобразователе 9 аналогично преобразователю 1 активизируется при этом по одному элементу И 2, находящемуся на пересечении активизированных шин. Затем в каждом преобразователе 9 с выхода активизированного элемента И 2 единичный сигнал поступает на один из n входов подключенного к нему элемента 4 ИЛИ.

Таким образом, на одной из выходных шин каждого из К преобразователей

9присутствует единичный сигнал, а на остальных - нулевые сигналы. Эти сигналы поступают соответственно на

К групп входных адресных шин многомерного устройства 7.

Благодаря тому, что соединение входов элементов 4 ИЛИ с выходами элементов 2 И в преобразователях 9 осуществлено с учетом величины сдвига номеров шин между матрицами многомерного- устройства 7, сигналы с выходных шин преобразователен 9 обеспечивают активизацию выбранного элемента в матрице устройства 7, имеющей номер Z, который определяется колом,

поступающим с выхода предварительного дешифратора 8.

Формула изобретения

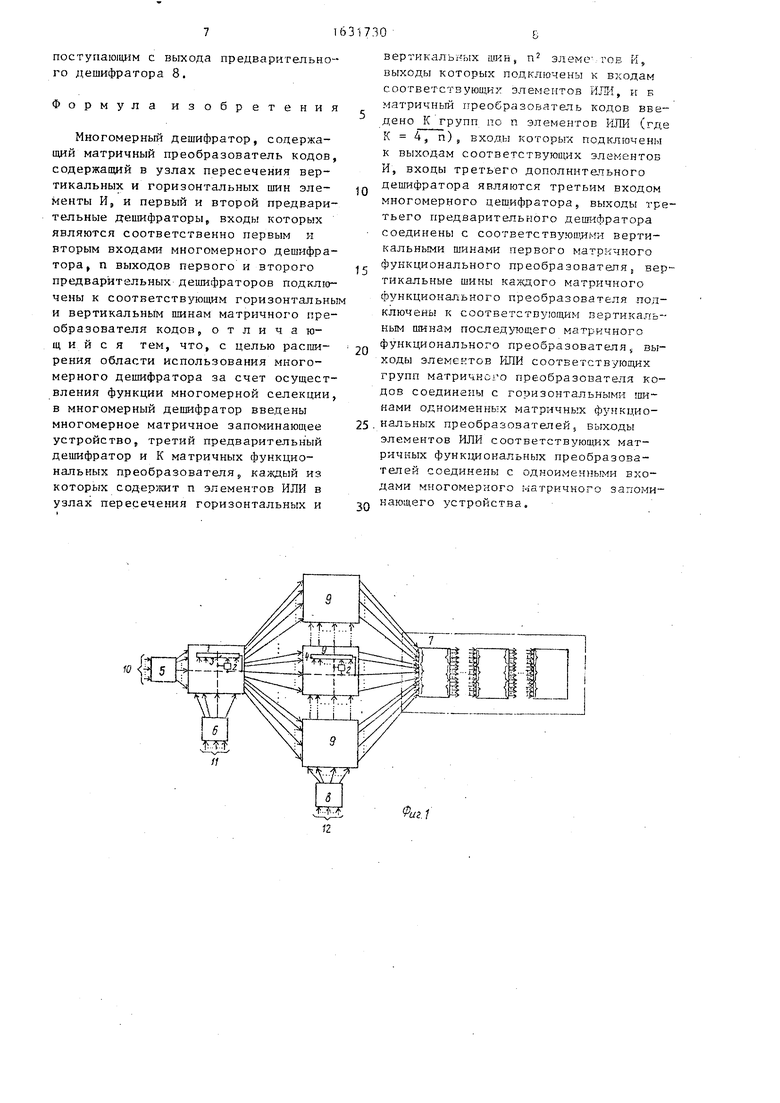

Многомерный дешифратор, содержащий матричный преобразователь кодов, содержащий в узлах пересечения вертикальных и горизонтальных шин эле- менты И, и первый и второй предварительные дешифраторы, входы которых являются соответственно первым и вторым входами многомерного дешифратора, п выходов первого и второго предварительных дешифраторов подключены к соответствующим горизонтальны и вертикальным шинам матричного преобразователя кодов, о т л и ч а ю- щ и и с я тем, что, с целью расширения области использования многомерного дешифратора за счет осуществления функции многомерной селекции, в многомерный дешифратор введены многомерное матричное запоминающее устройство, третий предварительный дешифратор и К матричных функциональных преобразователя9 каждый из которых содержит п элементов ИЛИ в узлах пересечения горизонтальных и

j 0

0

5.

вертикальных шкн, п2 эдеме ГОБ Й5 выходы которых подключены к входам соответствующих элементов ИЛИ, и Б матричный преобразователь кодов введено К групп по п элементов КЛИ (где К 4, п), входы которых подключены к выходам соответствующих элементов И, входы третьего дополнительного дешифратора являются третьим входом многомерного дешифратора, выходы третьего предварительного дешифратора соединены с соответствующими вертикальными шинами первого матричного функционального преобразователя, вертикальные шины каждого матричного функционального преобразователя подключены к соответствующим вертикальным шинам последующего матричного функционального преобразователя,, выходы элементов ИЛИ соответствующих групп матричного преобразователя кодов соединены с горизонтальными шинами одноименных матричных функциональных преобразователей, выходы элементов ИЛИ соответствующих матричных функциональных преобразователей соединены с одноименными входами многомерного матричного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многомерное матричное селектирующее устройство | 1987 |

|

SU1481853A1 |

| Запоминающее устройство | 1980 |

|

SU879648A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1983 |

|

SU1108507A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Многомерное устройство выборки | 1987 |

|

SU1430988A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Коммутатор | 1984 |

|

SU1175023A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования кодов, и может быть использовано для селекции многомерных матричных цифровых устройств, система адресных шин которых организована по многомерному принципу. Изобретение позволяет реализовать функцию многомерной селекции различных цифровых устройств, что обеспечивает расширение области применения многомерного дешифратора. Многомерный дешифратор содержит матричный преобразователь 1 кодов, состоящий из элементов И 2 и К групп 3 по п элементов ИЛИ, три предварительных дешифратора 5, 6 и 8, многомерное матричное запоминающее устройство 7,, К матричных функциональных преобразователей 9, каждый из которых состоит из п элементов ИЛИ 4 и п2 элементов И 2. 3 ил. § (Л

14wr

Составитель Б.Ходов Редактор Н.Горват Техред л.Олийнык

Заказ 556

Тираж 447

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг

Корректор А.Осауленко

Подписное

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU369628A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Шигин А.Г | |||

| и др | |||

| Цифровые вычислительные машины | |||

| М,: Энергия, 1975, с | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-02-28—Публикация

1987-03-03—Подача