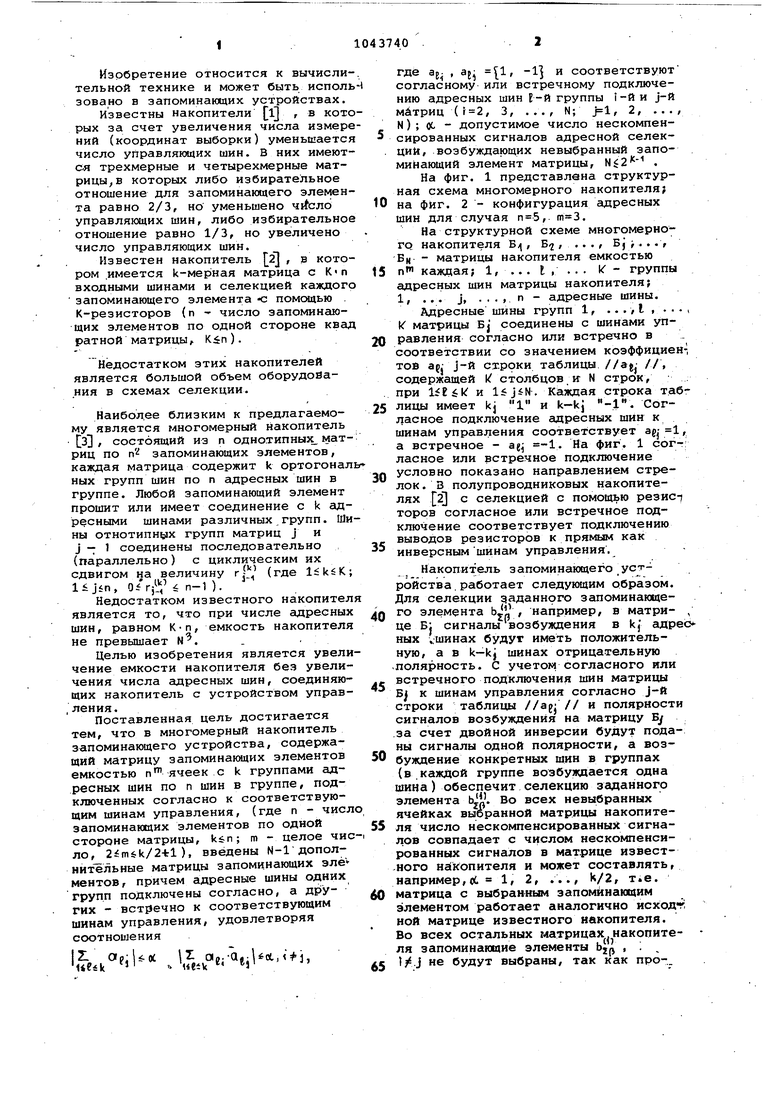

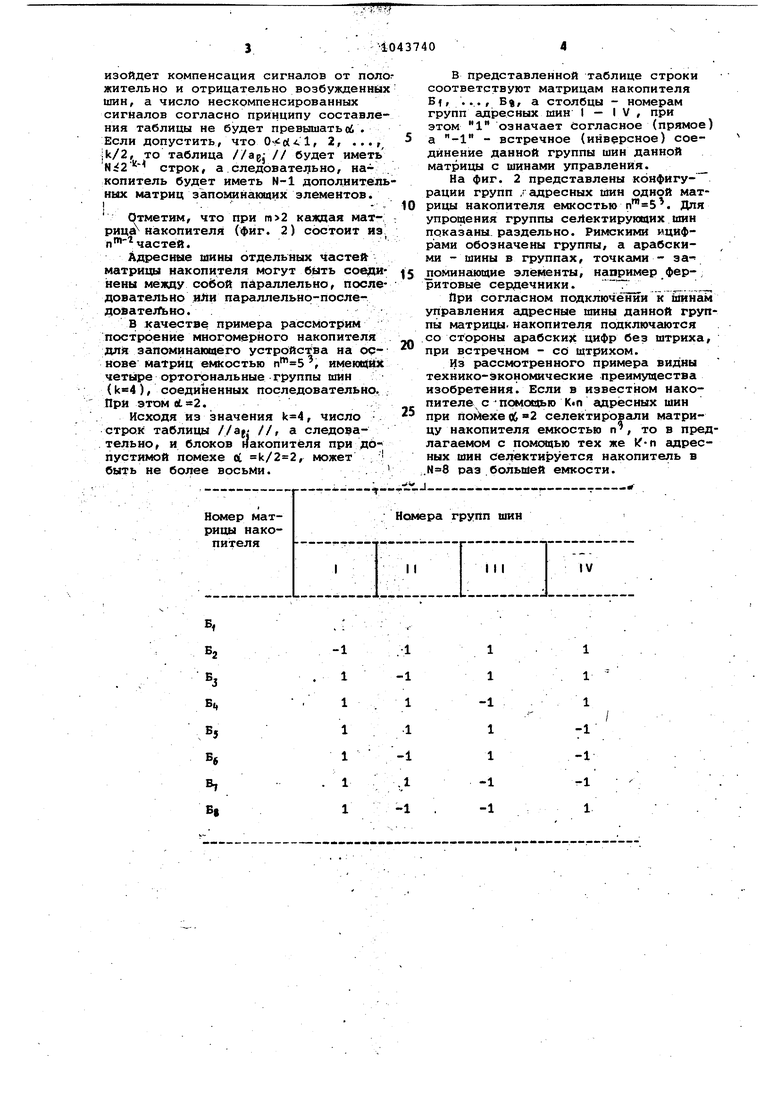

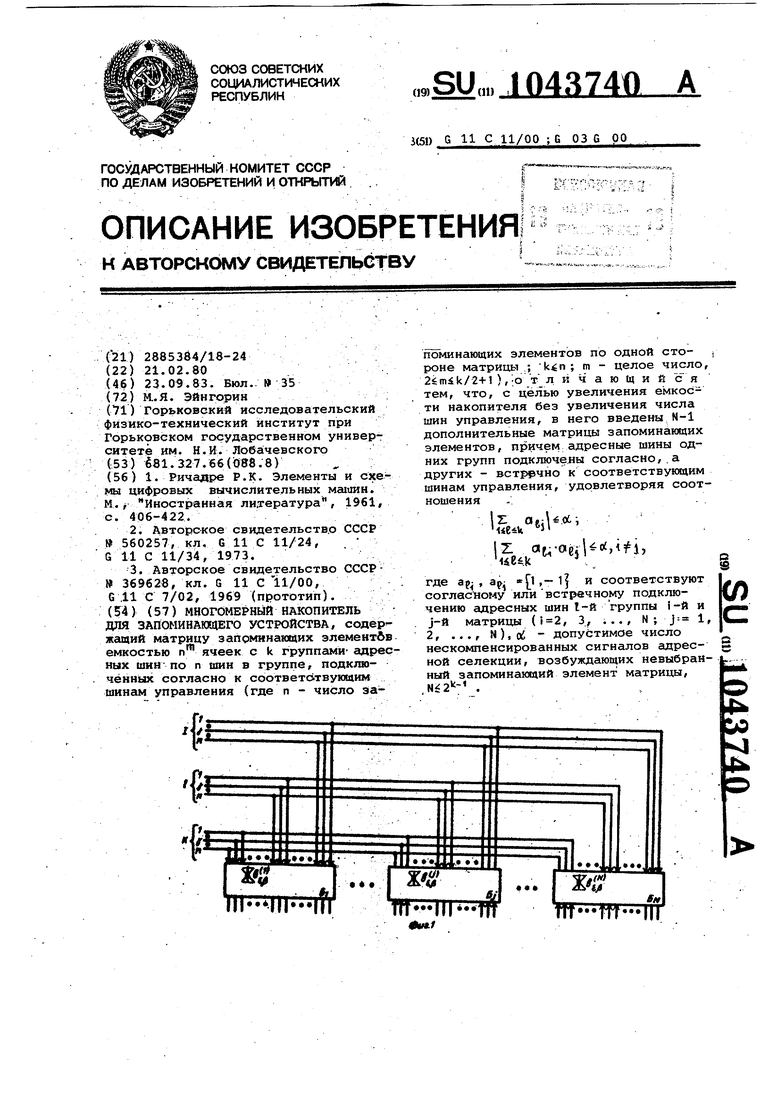

Изобретение относится к вычисли тельной технике и может быть испол зовано в запоминающих устройствах. Известны накопители l , в кот рых за счет увеличения числа измер ний (координат выборки) уменьшаетс число управляющих шин. В них имеют ся трехмерные и четырехмерные матрицы, в которых либо избирательное отношение для запоминающего элемен та равно 2/3, но уменьшено число управляющих шин, либо избирательно отношение равно 1/3, но увеличено число управляющих шин. Известен накопитель 2 , в кото ром имеется k-мерная матрица с К-п входными шинами и селекцией каждог запоминающего элемента -с помсндью . К-резисторов (п - число запоминающих элементов по одной стороне квад ратной матрицы. Kin). Недостатком этих накопителей является большой объем оборудования в схемах селекции. Наиболее близким к предлагаемому является многомерный накопитель з , состоящий из п однотипных, матриц по п запоминающих элементов, каждая матрица содержит k ортогонал ных групп шин по п адресных шин в группе. Любой запоминающий элемент прошит или имеет соединение с k адресными шинами различных,групп. Ши ны отнотипнух групп матриц j и j - 1 соединены последовательно , (параллельно) с циклическим их сдвигом на величину (где lijin. O/fjiV i n-1 ). Недостатком известного накопител является то, что при числе адресных шин, равном К-п, емкость накопителя не превышает N. . . Целью изобретения является увели чение емкости накопителя без увеличения числа адресных шин, соединяющих накопитель с устройством управ,ления. Поставленная цель достигается тем, что в многомерный накопитель запоминающего устройства, содержащий матрицу запоминающих элементов емкостью п ячеек с k группами алресных шин по п шин в группе, подключенных согласно к соответствующим шинам управления, (где п - числ запоминающих элементов по одной стороне матрицы, m - целое чис ло, 2 ni6k/2-H), введены N-1 дополнит льные матрицы запоминающих эле ментов, причем адресные шины одних групп подключены согласно, а других - вст 1ечно к соответствующим шинам управления, удовлетворяя соотношения 121 aoiUoc 21 c(,.-Q.(,,i, tieik . n«iv « где aj , 35 1 и соответствуют согласному или встречному подключению адресных шин Е-й группы i-йи j-й мАтриц (, 3, ... , N; 2, ..., N) ; ot - допустимое число нескомпенсированных сигналов адресной селекции, возбуждающих невыбранный запоминающий элемент матрицы, . На фиг. 1 представлена структурная схема многомерного накопителя на фиг. 2 - конфигурация адресных шин для случая , . На структурной схеме многомерного накопителя Бц, Б, ..., Бj j..., БМ- - матрицы накопителя емкостью п каждая; 1, ... t .... k - группы адресных шин матрицы накопителя; 1, ... j, ..., п - адресные шины. Адресные шины групп 1, .. .,I , .., k матрицы БJ соединены с шинами управления согласно или встречно в соответствии со значением коэффйциентов ар; j-й строки таблицы //aj //, содержащей k столбцов к N строк, при и . Каяузая строка таблицы имеет kj 1 и k-kj -1. Согласное подключение адресных шин к шинам управления соответствует ajj 1, а встречное - aj -1. На фиг. 1 сог-; ласное или встречное подключение условно показано направлением стрелок . 3 полупроводниковых накопителях 2 с селекцией с помощью резис-i торов согласное или встречное подключение соответствует подключению выводов резисторов к прямым как инверсным шинам управления . Накопитель запоминающего устройства . работает следующим образом. Для селекции заданного запоминающего элемента bJJ , например, в матри- , це Bj сигналы возбуждения в kf адрео ных vшинax будут иметь положительную, а в k-kj шинах отрицательную полярность. С учетом согласного или встречного подключения шнн матрицы Б к шинам управления согласно j-й строки таблицы //aj: // н полярности сигналов возбуждения на матрицу Бу за счет двойной ннверсин будут поданы сигналы одной полярности, а возбуждение конкретных шин в группах (в каждой группе возбуждается одна шина) обеспечит селекцию заданного элемента . Во всех невыбранных ячейках выбранной матрицы накопителя число нескомпенсированных сигналов совпадает с числом нескомпенсированных сигналов в матрице известного накопителя и может составлять, например,с 1, 2, ..., /2, . матрица с выбранным запоминающим элементом работает аналогично исходг, ной матрице известного накопителя. Во всех остальных матрицах.накопителя запоминающие элементы ьЦ , . lj.j не будут выбраны, так как про-.. изойдет компенсация сигналов от пол жительно и отрицательно возбужденны шин, а число нескомпенсированных сигналов согласно принципу составле ния таблицы не будет превышаться . Если допустить, что , 2, г, ;k/2, то таблица //ац // будет иметь строк, а следовательно, накопитель будет иметь N-1 дополнител ных матриц запоминающих элементов. Отметим, что при каждая матрица накопителя (фиг. 2) состоит из частей. Адресные шины отдельных чаете матрицы накопителя могут быть соеяи йены между собой параллельно, после довательно иЛи параллельнр-последosaтeJfьнo. В качестве примера рассмотрим построение многомерного накопителя дл)я запоминающего устройст ва на основе матриц емкостью , имеюцйЯ четыре ортотчэналь ные группы шин ( ), соединенных последовательно. При этомА :2. Исходя из значения , число строк таблицы //ац II, а следовательно, и блоков накопителя при дЬпустимой помехе оС , может быть не более восьми.. В представленной таблице строки соответствуют матрицам накопителя Б f, ..., Б %, а столбцы - номерам групп адресных шин I - I V , при этом 1 означает согласное (прямое) а встречное (инверсное) соединение данной группы шин данной матрицы с шинами управления. На фиг. 2 представлены конфигурации групп ,. адресных шин одной матрицы накопителя емкостью . Для упрощения группы селектирующих шин показаны, раздельно. Римскими ицифрами обозначены группы, а арабскими - шины в группах, точками - запоминсОощие элементы, например ферритовые сердечники. . , При согласном подключении к шинам управления адресные шины данной группы матрицЫ накопителя подключаются со стороны арабских цифр без штриха, при встречном - со штрихом. Из рассмотренного примера видны технико-экономические преимущества изобретения. Если в известном накопителе с помощью К«п адресных шин при пойехе о& 2 селектировали матрицу накопителя емкостью п, то в предлагаемом с помощью тех же адресных шин селектируется накопитель в . раз.большей емкости.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многомерный дешифратор | 1987 |

|

SU1631730A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ИНФОРМАЦИИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378683A1 |

| Многомерное устройство выборки | 1987 |

|

SU1430988A1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1169023A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Запоминающее устройство | 1987 |

|

SU1552229A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| ДЕТЕКТОР ИЗЛУЧЕНИЯ | 1992 |

|

RU2032189C1 |

МНОГОМЕРНЫЙ НАКОПИТЕЛЬ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содер жащий матрицу запомингиоцих элемент& емкостью п ячеек с k группами адре ных шин по п шин в группе, подключённых согласно к соответбтвукяцим шинам управления (где п - число заiii iM m поминающих элементов по одной сто- , роне матрицы.; ; tn - целое число, 26 mi k/2+1 ),-о т л и ч а ю Щ и и с я тем, что, с целью увеличения емкости накопителя без увеличения числа шин управления, в него введены,М-1 дополнительные матрицы запоминающих элементов, причем-адресные шины одних групп подключены согласно,.а других - встрэчно к соответствующим шинам управления, удовлетворяя соотношения -.. . i5e. iZ ae -aeiHoinfl, где ар , - 1 j и соответствуют согласному иливстречному подключению адресных шин 1-й группы i-й и j-й матрицы (, 3, ..., N; j 1, 2, ..., N ), ей - допустимое число нескомпенсированных сигналов адресной селекции, возбуждающих невыбранный запоминающий элемент матрицы, . «|||. Ш «1ТГ 1Т1

-1 1 1 1 1 1 1

Бг Sj

Бц

% Бб В, Б$

1

1

1

1

1

1 1 1

-1

1

-1

1

1

-1

1

-1

-1

1

-1 41 - - - « -.;.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ричадре Р.К | |||

| Элементы и схе мы цифровых вычислительных мшиин | |||

| М | |||

| Иностранная ли.тература, 1961, с | |||

| Электрическая лампа накаливания с двумя нитями | 1923 |

|

SU406A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-09-23—Публикация

1980-02-21—Подача