4

00

о

CD 00 00

Изобретение относится к вычислительной технике .и может быть использовано при создании матричных запоминающих устройств, устройств отображения информации и коммутирующих устройств.

Целью изобретения является упрощение изготовления устройства при сохранении отношения сигнал/помеха.

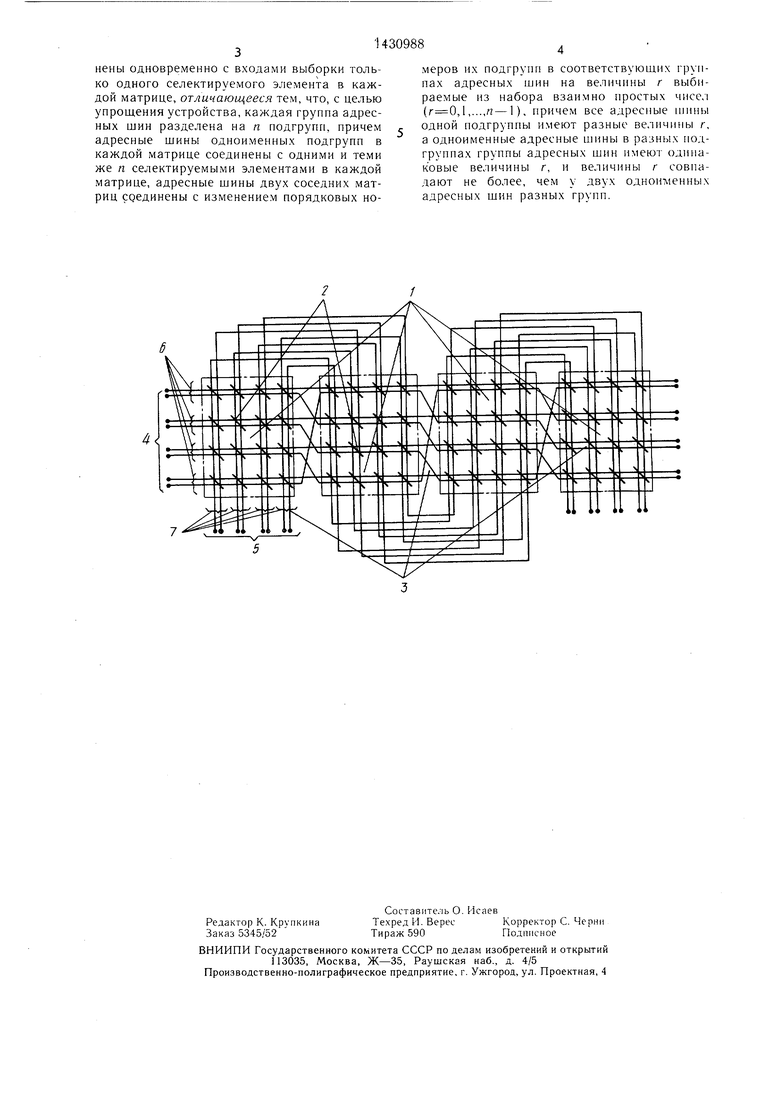

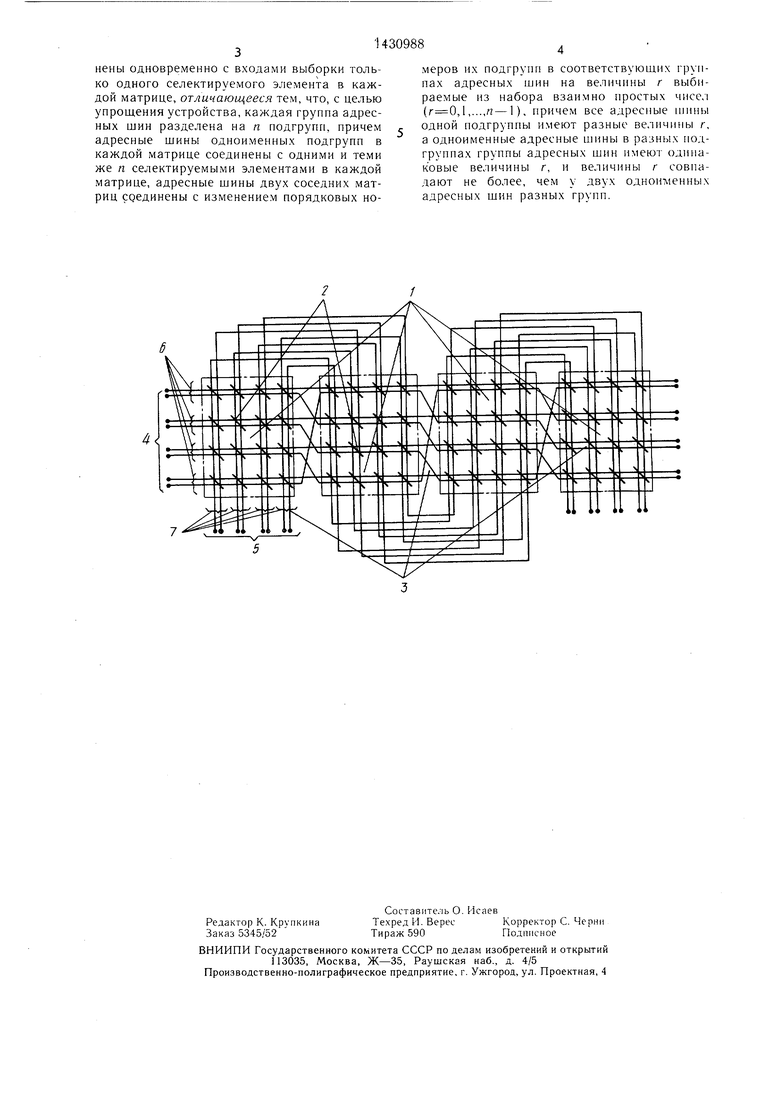

На чертеже показан пример выполнения многомерного матричного запоминающего устройства.

Устройство содержит п однотипных матриц 1. Каждая матрица содержит п селектируемых элементов 2 и адресные щины 3. Адресные тины 3 каждой матрицы 1 образует К ортогональных групп шин 4 и 5 (при ). Каждая ортогональная группа шин 4 и 5 состоит из п подгрупп 6 (подгрупп первой ортогональной группы) и 7 (подгрупп второй ортогональной группы). Каждая подгруппа содержит т адресных шин (на чертеже ).

Каждая адресная шина 3 в каждой матрице 1 соединена с п селектируемыми элементами 2. Каждый элемент памяти 2 соединен с адресными шинами 3, принадлежащими ко всем К группам. Адресные ШИНЬЕ одной подгруппы соединены с одними и теми же п селектируемыми элементами 2, а две шины разных подгрупп одной группы не имеют ни одного соединения с одним и тем же селектируемым элементом 2.

Ортогональность группы адресных шин матрицы 1 понимается в следующем смысле:

-любые две адресные щины из разных групп имеют равно один общий селектируемый элемент 2 в одной матрице 1;

-любые две адресные шины 3 из одной и той же группы либо не имеют ни одного общего селектируемого элемента 2 (тогда они принадлежат к разным подгруппам), либо имеют ровно п общих селектируемых элементов 2 (тогда они принадлежат к одной I той же подгруппе и подключены к разным входам одних и тех же элементов одной матрицы).

Адресные шины 3 однотипных /С-х ортогональных групп шин (т. е. групп одинаковой конфигурации) двух соседних матриц 1 соединены с изменение.м номеров подгрупп, к которым они принадлежат, в /С-й группе шин на величины г, выбираемые из любого полного набора взаимно простых чисел ri,..., Гпшх, где , г,.

Все адресные щины 3 одной и той же подгруппы /(-и группы щин имеют разные величины г: на чертеже первая щина первой подгруппы первой ортогональной группы имеет , а вторая - .

Адресные шины 3, имеющие одинаковый

10

15

20

25

30

35

40

45

50

величину , а все вторые шины всех подгрупп первой группы - .

Величины г совпадают не более, чем у двух щин разных ортогональных групп щин.

Устройство работает следующим образом.

Для выбора определенного селектируемого элемента 2 па все адресные щины 3, соединенные с ним, подаются сигналы с уровнем «логической единицы. Как правило, в качестве селектируемых элементов 2 используются элементы, которые переходят в активизированное состояние («срабатывают) в том случае, когда более чем на половину их входов поданы сигналы с уровнем «логической единицы. Таким образом, выбранный селектируемый элемент 2 «срабатывает. При этом максимальное количество активизированных входов (т. е. входов, на которые поданы сигналы с уровнем «логической единицы) у остальных (невыбранпых) элементов селектируемых 2 той же матрицы 1, к которой принадлежит выбранный элемент, составляет т/тшх (т. е. максимальное количество щин в подгруппе одной из К групп щин). Это обусловлено тем, что любая из К подгрупп адресных щин 3, соединенных с выбранным селектируемым элементом 2 (и, соответственно, активизированных), целиком соединена и с целым рядом невыбранных элементов, вследствие чего гПк входов каждого из них активизирована. Таким образом, величина помехи в той матрице 1, в которой находится выбранный селектируемый

(f

элемент 2, составляет rat.,,ia.v/2 ш. В остальных матрицах 1 благодаря тому, что все адресные шины 3 одной и той же подгруппы в любой группе щин имеют разные величины, а также тому, что величины г совпадают не более, чем у двух шин разных ортогональных групп шин, максимальное количество активизированных входов у невыбранных селектируемых элементов 2 равно

двум, т. е. величина помехи равна .

Таким образом, величина помехи в прилагаемом устройстве составляет т, что обеспечивает однозначную селекцию его элементов при более простой конфигурации адресных шин.

Формула изобретения

Многомерное устройство выборки, содержащее п квадратных матриц по л селектируемых элементов, адресные щины каждой матрицы разделены на К групп (/(-2,3,...,п) и соединены с входами выборки и селектиномер в разных подгруппах К-й группы шин, 55Руемых элементов в каждой группе, входы

имеют одинаковые величины г: на чертежевыборки каждого элемента подключены к

все первые щины всех подгрупп первойадресным щинам всех групп, причем любые

ортогональной группы имеют одинаковуюдве адресные разных групп соеди0

5

0

5

0

5

0

5

величину , а все вторые шины всех подгрупп первой группы - .

Величины г совпадают не более, чем у двух щин разных ортогональных групп щин.

Устройство работает следующим образом.

Для выбора определенного селектируемого элемента 2 па все адресные щины 3, соединенные с ним, подаются сигналы с уровнем «логической единицы. Как правило, в качестве селектируемых элементов 2 используются элементы, которые переходят в активизированное состояние («срабатывают) в том случае, когда более чем на половину их входов поданы сигналы с уровнем «логической единицы. Таким образом, выбранный селектируемый элемент 2 «срабатывает. При этом максимальное количество активизированных входов (т. е. входов, на которые поданы сигналы с уровнем «логической единицы) у остальных (невыбранпых) элементов селектируемых 2 той же матрицы 1, к которой принадлежит выбранный элемент, составляет т/тшх (т. е. максимальное количество щин в подгруппе одной из К групп щин). Это обусловлено тем, что любая из К подгрупп адресных щин 3, соединенных с выбранным селектируемым элементом 2 (и, соответственно, активизированных), целиком соединена и с целым рядом невыбранных элементов, вследствие чего гПк входов каждого из них активизирована. Таким образом, величина помехи в той матрице 1, в которой находится выбранный селектируемый

(f

элемент 2, составляет rat.,,ia.v/2 ш. В остальных матрицах 1 благодаря тому, что все адресные шины 3 одной и той же подгруппы в любой группе щин имеют разные величины, а также тому, что величины г совпадают не более, чем у двух шин разных ортогональных групп шин, максимальное количество активизированных входов у невыбранных селектируемых элементов 2 равно

двум, т. е. величина помехи равна .

Таким образом, величина помехи в прилагаемом устройстве составляет т, что обеспечивает однозначную селекцию его элементов при более простой конфигурации адресных шин.

50

Формула изобретения

Многомерное устройство выборки, содержащее п квадратных матриц по л селектируемых элементов, адресные щины каждой матрицы разделены на К групп (/(-2,3,...,п) и соединены с входами выборки и селекти55Руемых элементов в каждой группе, входы

йены одновременно с входами выборки только одного селектируемого элемента в каждой матрице, отличающееся тем, что, с целью упрощения устройства, каждая группа адресных шин разделена на п подгрупп, причем адресньге шины одноименных подгрупп в каждой матрице соединены с одними и теми же п селектируемыми элементами в каждой матрице, адресные шины двух соседних матриц соединены с изменением порядковых номеров их подгрупп в соответствующих группах адресных шин на величины г выбираемые из набора взаимно простых чисел

(,1« -1), причем все адресные 1пины

одной подгруппы имеют разные величины г, а одноименные адресные шины в разных подгруппах группы адресных шин имеют одинаковые величины г, и величины г совпадают не более, чем у двух одноименных адресных шин разных групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многомерное матричное селектирующее устройство | 1987 |

|

SU1481853A1 |

| Многомерный дешифратор | 1987 |

|

SU1631730A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Матричный экран | 1975 |

|

SU930351A1 |

| АССОЦИАТИВНЫЙ НАКОПИТЕЛЬ | 1973 |

|

SU374662A1 |

Изобретение относится к вычислительной технике и может бь1ть использовано при создании матричных запоминающих устройств, устройств отображения информации и коммутирующих устройств. Целью изобретения является упрощение изготовления устройства при сохранении отношения сигнал/ помеха. Устройство содержит п однотипных матриц, каждая из которых включает п селектируемых элементов памяти. Адресные щины устройства разделены на К ортогональных групп щин, каждая из которых содержит п подгрупп. Каждая адресная шина в каждой матрице соединена с входами выборки соответствующих п селектируемых элементов строки или столбца матрицы. Каждый селектируемый элемент соединен с соответствующими адресными шинами всех К групп. Цель изобретения достигается упрощением конфигурации адресных щин при сохранении их количества и отнощения сигнал/помеха. 1 ил. (Л

| Проблемы кибернетики | |||

| Сб | |||

| статей/Под ред | |||

| А | |||

| А | |||

| Ляпунова | |||

| М.: Наука, 1961 | |||

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU369628A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-15—Публикация

1987-03-03—Подача