1

Изобретение относится к вычислительной технике и может .быть использовано в регистрирующей аппаратуре три автоматизации исследований различных процессов.

Известен аналого-цифровой П(ре0бразователь, содержащий Б каждом разряде унифицированный элемент, преобразователь тока ,в напряжение, триггер, две схемы «И, входы которых подключены к выходам триггер разряда, а выходы соединены с одними входами схем «ИЛИ следующих разрядов, две дополнительные схемы «И, одни входы которых соединены с выходами триггерав разрядов.

Однако известный лреобразаватель обладает недостаточным быстродействием и большой погрешностью преобразования, так как около половины погрешности преобразования приходится на динамическую погрешность, величина которой различна для четных и нечетных уровней квантования.

С целью повышения быстродействия, уменьшения 1погрешности и исключения ошибок при считывании в (предлагаемом аналого-цифровом преобразователе в каждом разряде, кроме старшего, к выходу унифицированнюто элемента подключены другой вход первой схемы «ИЛИ и первой схемы «И непосредственно и другой вход второй схемы «ИЛИ и второй схемы «И через схему «НЕ, другие входы дополнительных схем «И через блок формирования сигнала считывания соединены с выходами триггера младшего разряда.

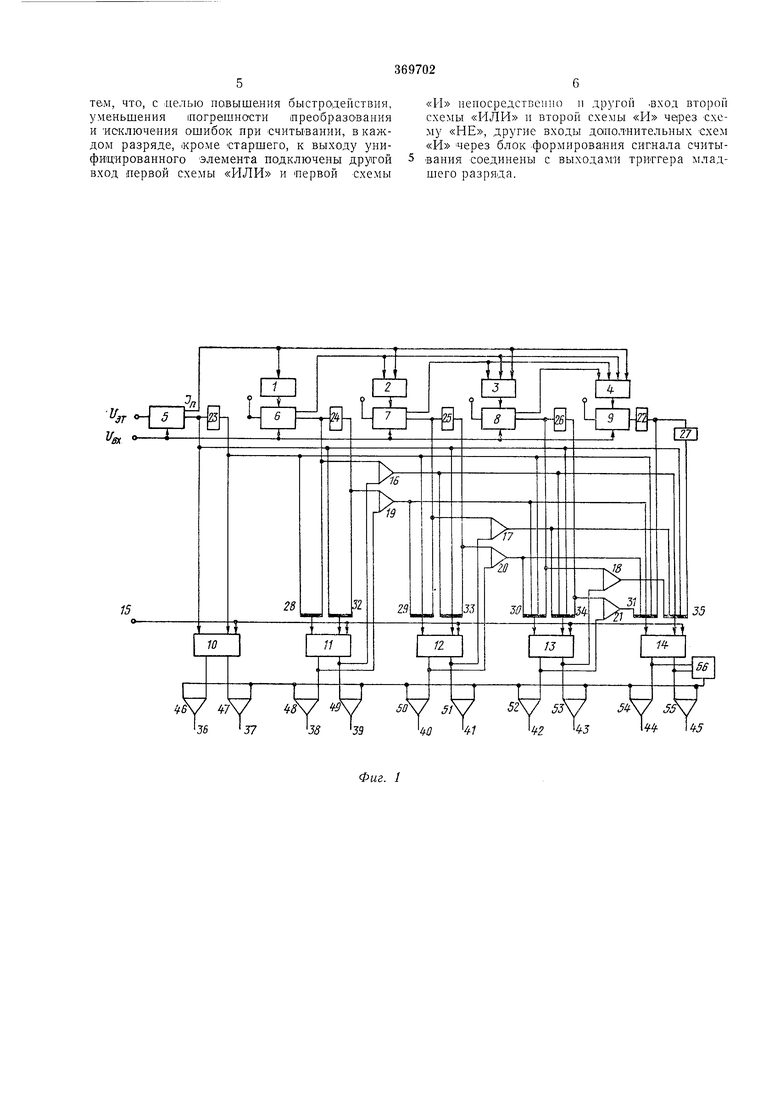

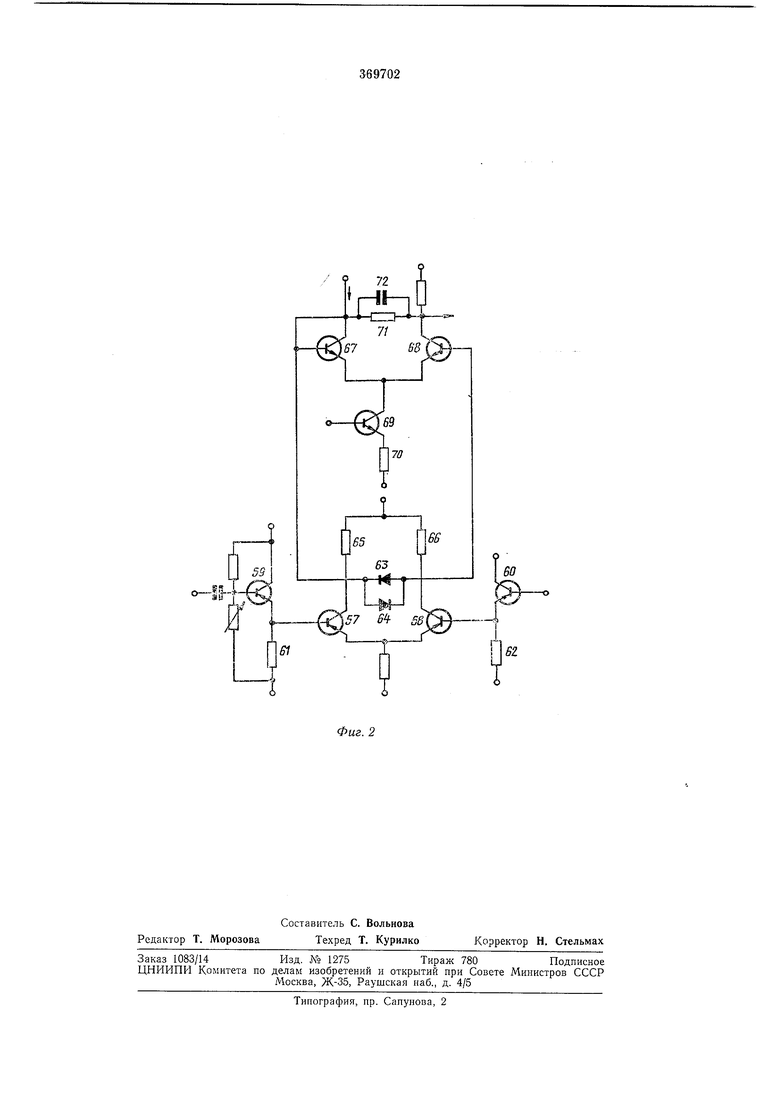

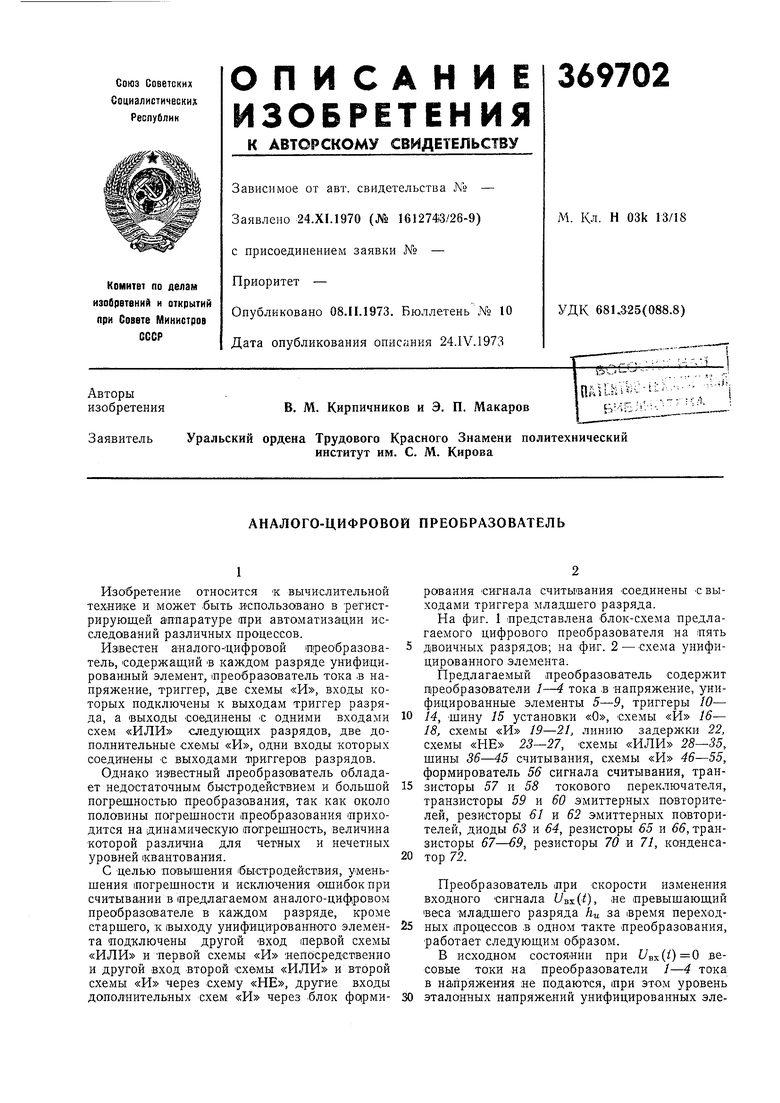

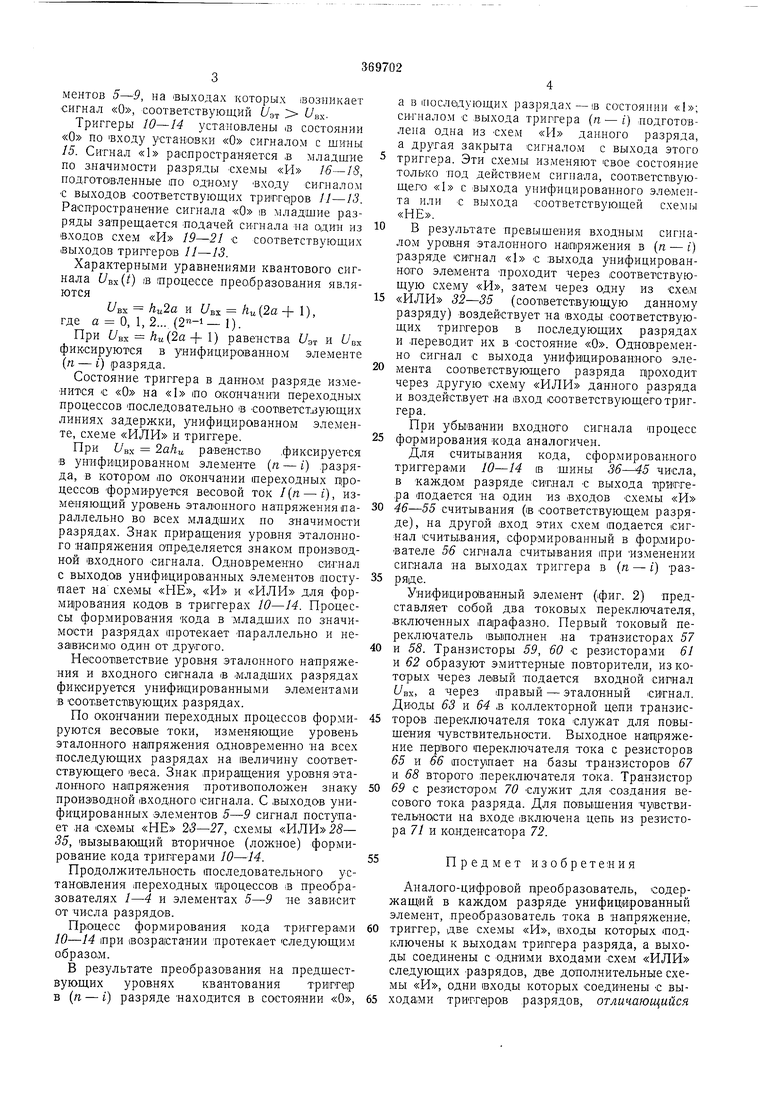

На фиг. 1 представлена блок-схема предлагаемого цифрового преобразователя на пять двоичных разрядов; на фиг. 2 схема унифицированного элемента.

Предлагаемый преобразователь содержит преобразователи 1-4 тока в напряжение, унифицированные элементы 5-9, триггеры 10-

14, шину 15 установки «О, схемы «И 16- 18, схемы «И 19-21, линию задержки 22, схемы «НЕ 23-27, схемы «ИЛИ 28-35, шины 36-45 считывания, схемы «И 46-55, формирователь 56 сигнала считывания, транзисторы 57 и 55 токового переключателя, транзисторы 59 и 60 змиттерных повторителей, резисторы 61 и 62 эмиттерных повторителей, диоды 63 и 64, резисторы 65 и 65, транзисторы 67-69, резисторы 70 и 71, конденсатор 72.

Преобразователь лри скорости изменения

входного сигнала t/Bx(), яе превышающий

веса Младшего разряда hu за время переходных яроцессов в одном такте преобразования,

работает следующим образом.

В исходном состоянии при i/Bx( вб

совые токи на преобразователи /-4 тока

в напряжения не подаются, при этом уровень

эталонных напряжений унифицированных элементов 5-9, на выходах которых 1возникает сигнал «О, соответствующий эт .

Триггеры 10-14 установлены IB состоялии «О по входу установки «О сигналом с шины 15. Сигнал «1 распространяется .в младшИе по значимости разряды схемы «И 16-IS, подготовленные по одному Входу сигналом с выходов соответствующих три ггдров 11-13. Распространение сигнала «О IB младшие разряды запрещается подачей сигнала на один из входов схем «И 19-21 с соответствующих выходов триггеров 11-13.

Характерными уравнениями квантового сигнала (УвхСО IB процессе прео1бразования являются

вх hu2a и f/Bx /г„(2а + 1), где а О, 1, 2.... (2«-1- 1).

При f/Bx /ги(2а-J-1) равенства i/эт и Ивк фиксируются в унифицированном элементе (п - t) разряда.

Состояние триггера в данно м разряде изменится с «О на «1 по окончании переходных процессов последовательно в сооиветстлующих линиях задержки, унифицированном элементе, схеме «ИЛИ и триггере.

При t/Bx 2ahu равенство .фиксируется в унифицированном элементе (п - г) .разряда, в котором по окончании переходных цроцессов формируется весовой ток 1(п - г), изменяющий уровень эталонного напряжения параллельно во всех младших по значимости разрядах. Знак приращения уровня эталонного напряжения определяется знаком производной входного сигнала. Одновременно сигнал с выходов унифицированных элементов поступает на схемы «НЕ, «И и «ИЛИ для форми|рования кодов в триггерах 10-14. Процессы формирования кода в младши.х по значимости разрядах протекает параллельно и неaaiBHCHMO один от другого.

Несоответствие уровня эталонного напряжения и входного сигнала в младших разрядах фиксируется унифицированными элементами в соответствующих разрядах.

По окончании переходных процессов формируются весовые токи, изменяющие уровень эталонного напряжения одновременно на всех последующих разрядах на величину соответствующего веса. Знак приращения уровня эталонного напряжения противоположен знаку производной входного сигнала. С .выходов унифицированных элементов 5-9 сигнал поступает на схемы «НЕ 25-27, схемы «ИЛИ.2§- 35, вызываю|щий вторичное (ложпое) формирование кода триггерами 10-14.

Продолжительность последовательного установления переходных процессов IB преобразователях /-4 и элементах 5-9 не зависит от числа разрядов.

Процесс формирования кода триггерами 10-14 при возрастании протекает следующим образом.

В результате преобразования на предществующих уровнях квантования триггер в (п - t) разряде находится в состоянии «О,

а в 1Г1осладующих разрядах-IB состоянии сигнало.м с выхода триггера (п - г) подготовлена одна из схем «И данного разряда, а другая закрыта сигналом с выхода этого

триггера. Эти схемы изменяют свое состояние только под действием сигнала, соответствующего «I с выхода унифицированного элемента или с выхода соответствующей схемы «НЕ.

В результате превышения входным сигналом уровня эталонного напряжения в (л - г) разряде сигнал «1 с .выхода унифицированного элемента проходит через соответствующую схему «И, затем через одну из схем

«ИЛИ 32-35 (соответствующую данному разряду) воздействует на входы соответствующих триггеров в последующих разрядах и переводит их в состояние «О. Одновременно сигнал с выхода унифицированного элемента соответствующего разряда проходит через другую схему «ИЛИ данного разряда и воздействует на вход соответствующего триггер а. При убывании входного сигнала процесс

формирования кода аналогичен.

Для считывания кода, сформированного триггерами 10-14 IB шины 36-45 числа, в каждом разряде сигнал с выхода триггера подается на один из входов схемы «И

46-55 считывания (в соответствующем разряде) , на другой вход этих схем подается сигнал считывания, сформированный в формирователе 56 сигнала считывания при изменении сигнала на выходах триггера в (л - i) разряде.

Унифицированный элемент (фиг. 2) представляет собой два токовых переключателя, включенных парафазно. Первый токовый переключатель выполнен на транзисторах 57

и 55. Транзисторы 59, 60 с резисторами 61 и 62 образуют эмиттерные повторители, из которых через левый подается входной сигнал (Увх, а через правый - эталонный сигнал. Диоды 63 и 64 в коллекторной цепи транзисторов переключателя тока служат для повышения чувствительности. Выходное на П1ряжение первого переключателя тока с резисторов 65 и 66 поступает на базы транзисторов 67 и 68 второго переключателя тока. Транзистор

69 с резистором 70 служит для создания весового тока разряда. Для повышения чувствительности на входе включена цепь из резистора 71 и конденсатора 72.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий в каждом разряде унифицированный элемент, .преобразователь тока в напряжение.

триггер, две схемы «И, входы которых (подключены к выходам триггера разряда, а выходы соединены с одними входами схем «ИЛИ следующих разрядов, две дополнительные схемы «И, одни входы которых соединены с выходами триггеров разрядов, отличающийся

T6i, что, с |Целью повышения оыстродействия, уменьшения 1ногрешности преобразования и -нсключеиия ошибок при считывании, в каждом разряде, «роме старшего, к выходу унифицированного элемента подключены другой вход первой схемы «Р1ЛИ и первой схемы

«И иепосредствеиио и другой .вход второй схемы «ИЛИ и второй схемы «И через схему «НЕ, другие входы дополнительных схем «И через блок формирования сигнала считывания соединены с выходами триггера младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| •РСЕСО-ЭЗНА^^г •^'•2[[Т].0- г;:^^':г^:;пт | 1973 |

|

SU369707A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU400021A1 |

| Параллельный аналого-цифровой преобразователь | 1978 |

|

SU769731A1 |

| Преобразователь напряжения в циклический код | 1976 |

|

SU738144A1 |

| Аналого-цифровое устройство | 1981 |

|

SU1018239A1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU247640A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| Параллельно-последовательный преобразователь напряжения в код | 1982 |

|

SU1039027A2 |

| Аналого-цифровой преобразователь | 1978 |

|

SU869021A1 |

Фиг. 1

Авторы

Даты

1973-01-01—Публикация