1

Изобретение относится к импульсной технике, в частности к устройствам параллельного аналого-дискретного преобразования, в которых множество опорных значений, различных по величине, одновременно сравниваются с аналоговыми значениями преобразуемого сигнала. Устройство молсет быть использовано в скоростных системах обработки информации.

Известен параллельный аналого-цифровой преобразователь, содерлсащий л групп компараторов и элементов памяти, где п 1, 2, 3,..., п - число разрядов, причем общее число компараторов, подключенных к управляющим входам элементов памяти, составляет 2 а элементов памяти - (), тактовые входы элемеитов памяти иодключены к источнику стробирующего сигнала, а выходы - к разрядным щинам 1.

Недостатки этого АЦП - низкая точность, равная четырем разрядам, и значительная аипаратуриая избыточность.

Наиболее близким по технической сущности и достигаемому результату является иараллельный аналого-цифровой иреобразователь, содержащий групиу компараторов старщих разрядов и групиу компараторов младших разрядов, первые входы которых подключеиы к выходам источников опорных нанряжении, сигнальные входы груииы комиараторов старших разрядов иодключены к источнику преобразуемого сигнала, выходы комиараторов в каждой группе, 5 кроме компараторов старщих разрядов соответствующей группы, объединены попарно и нодключены к уиравляющим входам соответствующих элемеитов памяти, выходы комиараторов старших разрядов соответствующих групи соединены с уиравляющими входами соответств ющих им элементов памяти, резистивиый делитель, источиик стробирующего сигнала и источники тока смещения 2.

15 Известное устройство имеет недостаточно высокую точность.

Целью изобретения является повышение точности иреобразователя.

Поставленная цель достигается тем, ,что

20 в иараллельный аналого-цнфровой преобразователь, содержащий группу компараторов старших разрядов и группу компараторов младших разрядов, первые входы которых подключеиы к выходам источников опорных

95 напряжений, а сигнальные входы группы комиараторов старших разрядов иодключены к источнику преобразуемого сигнала, выходы компараторов в каждой группе, кроме компараторов старших разрядов со30 ответствующей группы, объединены попарно n подключены к управляющим входам соответствующих элементов памяти, выходы компараторов старших разрядов соответствующих групп соединены с управляющими входами соответствующих им элементов памяти, резистивный делитель, источник стробирующего сигнала и источники тока смещения, введены инвертор, повторитель, элемент И-ИЛИ и дополнительный резистивный делитель, причем первые входы резистивных делителей подключены к выходам источников тока смещения, вторые входы соответственно через повторитель и инвертор подключены к выходу источника преобразуемого сигнала, а выходы попарно, со сдвигоц на один, через элемент И- ИЛИ подключены к сигнальным входам группы компараторов младших разрядов, а входы стробирования элементов памяти подключены к выходу источника стробирующего сигнала.

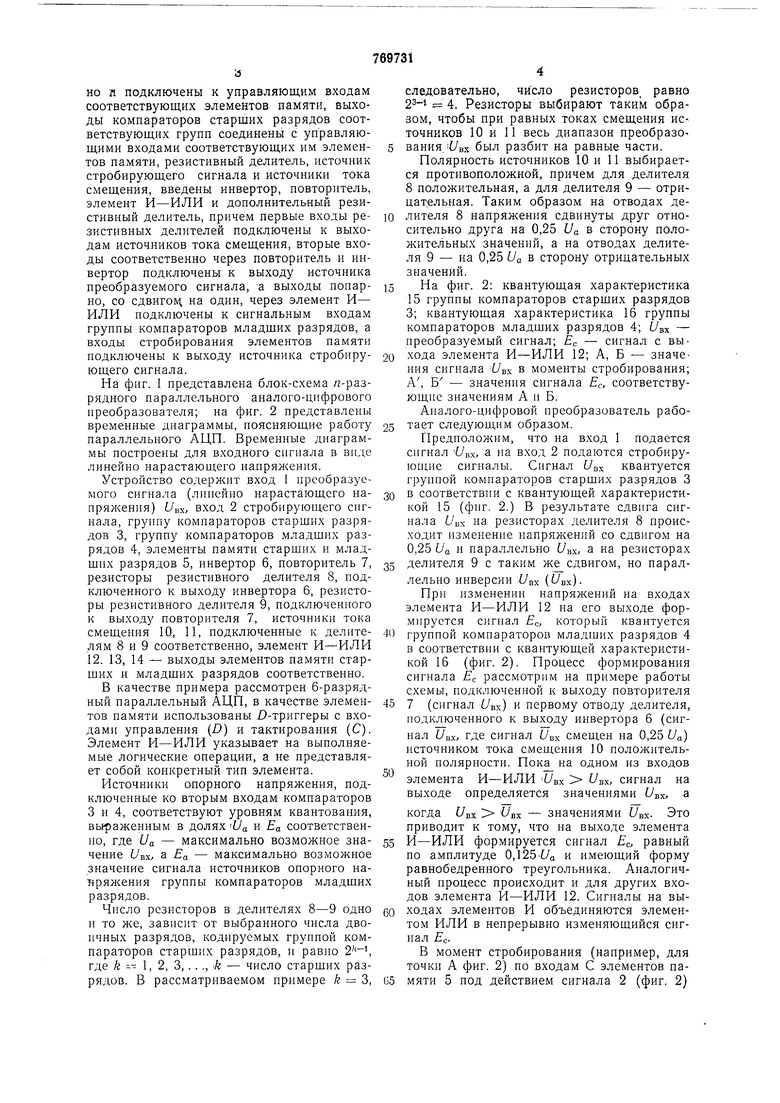

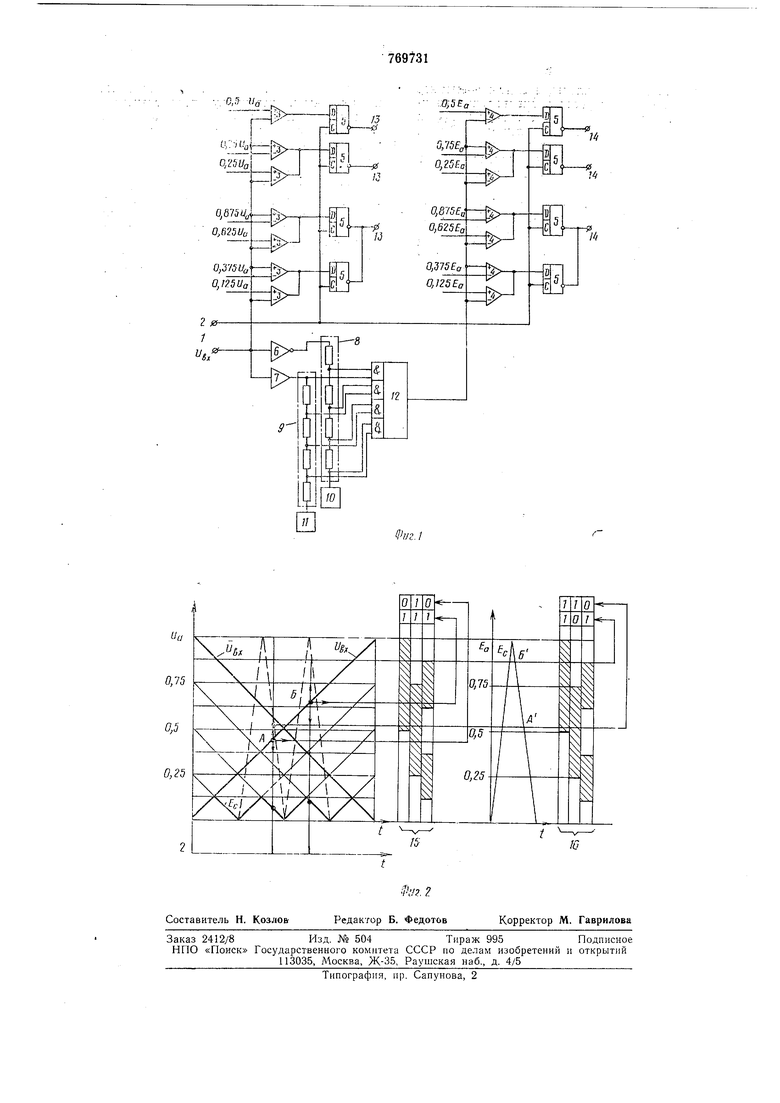

На фиг. 1 представлена блок-схема «-разрядного параллельного аналого-цифрового преобразователя; на фиг. 2 представлены временные диаграммы, поясняющие работу параллельного АЦП. Временные диаграммы построены для входного сигнала в виде линейно нарастающего напряжения.

Устройство содержит вход 1 преобразуемого сигнала (линейно нарастающего напряжения) УВХ, вход 2 стробирующего сигнала, группу компараторов старших разрядов 3, группу компараторов младших разрядов 4, элементы памяти старших и младщих разрядов 5, инвертор 6, повторитель 7, резисторы резистивного делителя 8, подключенного к выходу инвертора 6, резисторы резистивного делителя 9, подключеииого к выходу повторителя 7, источники тока смещения 10, 11, подключенные к делителям 8 и 9 соответственно, элемент И-ИЛИ 12. 13, 14 - выходы элементов памяти старших и младших разрядов соответственно.

В качестве примера рассмотрен 6-разрядный параллельный АЦП, в качестве элементов памяти использованы /)-триггеры с входами управления (D) и тактирования (С). Элемент И-ИЛИ указывает на выполняемые логические операции, а не представляет собой конкретный тип элемента.

Источники опорного напряжения, подключенные ко вторым входам компараторов 3 и 4, соответствуют уровням квантования, вьрраженным в долях (Уд и Еа соответственно, где Ua - максимально возможное значение t/Bx а 0 - максимально возможное значение сигнала источников опорного наТ1ряжения группы компараторов младших разрядов.

Число резисторов в делителях 8-9 одно и то же, зависит от выбранного числа двоичных разрядов, кодируемых группой компараторов старших разрядов, и равно 2 где k -- , 2, 3,..., k - число старших разрядов. В рассматриваемом примере k 3,

следовательно, число резисторов равно 23-1 : 4. Резисторы выбирают таким образом, чтобы при равных токах смещения источников 10 и 11 весь диапазон преобразо ванияjf/Bx был разбит на равные части.

Полярность источников 10 и И выбирается противоположной, причем для делителя 8 положительная, а для делителя 9 - отрицательная. Таким образом на отводах делителя 8 напряжения сдвинуты друг относительно друга на 0,25 Ua в сторону положительных значений, а на отводах делителя 9 - на 0,25 Ua в сторону отрицательных значений.

На фиг. 2: квантующая характеристика 15 группы компараторов старших разрядов 3; квантующая характеристика 16 группы компараторов младших разрядов 4; t/вх - преобразуемый сигнал; ЕС - сигнал с выхода элемента И-ИЛИ 12; А, Б -- значения сигнала :{7вх в моменты стробирования; А , Б - значения сигнала ЕС, соответствующие зиачеииям А и Б. Аналого-цифровой преобразователь работает следующим образом.

Предположим, что на вход 1 подается сигнал У„х, а на вход 2 подаются стробируюияие сигналы. Сигнал f/Bx квантуется г)уипой компараторов старших разрядов 3

в соответствии с квантующей характеристикой 15 (фиг. 2.) В результате сдвига сигнала Lljx на резисторах делителя 8 происходит изменеиие напрял ений со сдвигом на 0,25 Ua и параллельно /7вх, а на резисторах

делителя 9 с таким же сдвигом, но параллельно инверсии /7вх (UEK)При изменении напряжений на входах элемента И-ИЛИ 12 на его выходе формируется сигнал ЕС, который квантуется

группой компараторов младших разрядов 4 в соответствии с квантующей характеристикой 16 (фиг. 2). Процесс формирования сигнала ЕС рассмотрим на примере работы схемы, иодключениой к выходу повторителя

7 (сигнал и первому отводу делителя, подключенного к выходу инвертора 6 (сигнал UBX, где сигнал (Увх смещен на 0,25 Ua) источником тока смещения 10 положительной полярности. Пока на одном из входов

элемента И-ИЛИ Usx. вх. сигнал на выходе определяется значениями LBX, а

когда /вх UB:S. - значениями 1/вх. Это приводит к тому, что на выходе элемента

И-ИЛИ формируется сигнал ЕС, равный по амплитуде 0,125La и имеющий форму равнобедренного треугольника. Аналогичный процесс происходит и для других входов элемента И-ИЛИ 12. Сигналы на выходах элементов И объединяются элементом ИЛИ в непрерывно изменяющийся сигнал ЕС.

В момент стробирования (например, для

точки А фиг. 2) по входам С элементов намяти 5 под действием сигнала 2 (фиг. 2)

происходит параллельное и одновременное запоминание цифрового эквивалента квантованных значений А н А сигналов I/BX и ЕС, в результате чего на выходах 13 и 14 элементов памяти 5 одновременно появляется цифровой эквивалент значения t/вх в точке А (фиг. 2), кодированный в коде Грея.

Суммарный цифровой результат преобразования получается как суперпозиция цифровых значений, получаемых при запоминании элементами памяти с выходами 13 и 14 результатов квантования обеих групп компараторов 3 и 4. Суммарный код следует рассматривать как сумму двоичных чисел, которая образуется в момент запоминания кода и хранится в элементах памяти с выходами 13 и 14 до появления по входу 2 следующего стробирующего импульса.

Конкретное значение кода (от старших разрядов к младшим) для точки А (фиг. 2) - 010 + 110 010110, что соответствует 27 квантам, а для точки Б - 111 + 101 111101, что соответствует 41 кванту.

Формула изобретения

Параллельный аналого-цифровой преобразователь, содержаш,ий группу компараторов старших разрядов и группу компараторов младших разрядов, первые входы которых подключены к -выходам источников опорных напряжений, а сигнальные входы

группы компараторов старш 1х разрядов подключены к источнику преобразуемого сигнала, выходы компараторов в каждой группе, кроме компараторов старших разрядов соответствующей группы, объединены попарно и подключены к управляющим входам соответствующих элементов памяти, выходы компараторов старших разрядов соответствующих групп соединены с управляющими входами соответствующих им элементов памяти, резистивный делитель, источник стробирующего сигнала и источники тока смещения, отличающийся тем, что, с целью повышения точности, в него введены инвертор, повторитель, элемент И-ИЛИ и дополнительный резистивный делитель, причем первые входы резнстивных делителей подключены к выходам источников тока смещения, вторые входы соответственно через повторитель и инвертор подключены к выходу источника преобразуемого сигнала, а выходы попарно, со сдвигом на один, через элемент И-ИЛИ подключены к сигнальным входам группы компараторов младших разрядов, а входы стробирования элементов памяти подключены к выходу источника стробирующего сигнала.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3829853, кл. 340-347, 1976.

2. Авторское свидетельство СССР по заявке №. 2254459/18-21, 28.04.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1980 |

|

SU869026A1 |

| Параллельный аналого-цифровой преобразователь | 1977 |

|

SU934574A1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1035795A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1019623A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-11—Подача