1

Изобретение относится к области вычислительной, измерительной техники.

Известен аналого-цифровой преобразователь, содержащий в каждом разряде схему сравнения, триггер, схемы «ИЛИ, входы которых соединены с выходами схемы сравнения старшего разряда и с выходами схем «И предыдущих разрядов, а выходы подключены ко входам триггера, схемы «И, соединенные с выходами триггера, цифровые, управляемые сопротивления и ключи, подключенные к выходам триггеров предыдущих разрядов.

Известное устройство имеет недостаточное быстродействие и недостаточно высокую точность преобразования.

С целью повышения быстродействия и точности преобразования в предлагаемом преобразователе в младшем разряде выходы схемы сравнения подключены ко входам четырех схем «И, выходы которых через схемы «ИЛИ соединены со входами триггера, вторые входы двух схем «PI через линию задержки подключены к выходу формирователя импульсов, третьи входы двух схем «И соединены с выходами триггера и входами формирователя импульсов.

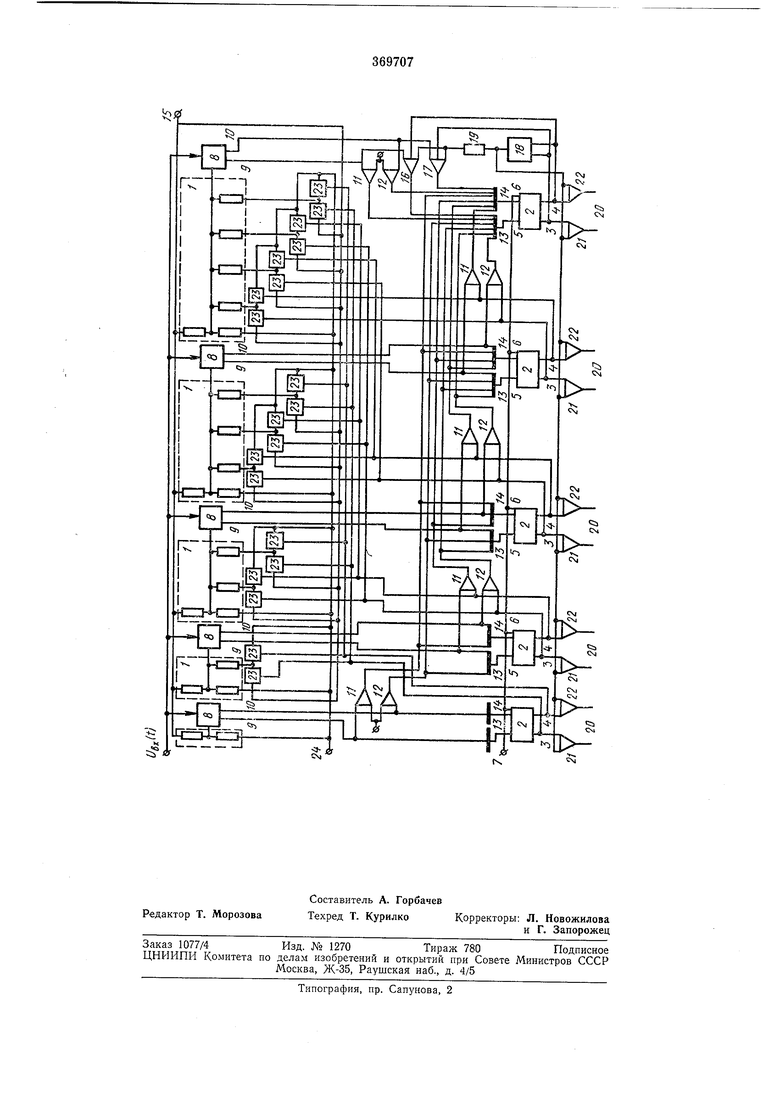

На чертеже представлена блок-схема предлагаемого аналого-цифрового преобразователя на пять двоичных разрядов. Устройство содержит цифровые управляе

мые сопротивления 1, статические триггеры 2 выходного регистра с выходами 5 и 4 и входами 5 и 6, шину 7 «установка нуля триггеров 2 выходного регистра, схемы 5 сравнения с выходами 9 и 10, схемы «И 11 и 12 на два входа, схемы «ИЛИ 13 и 14, шину 15 опорного напряжения, схемы «И 16 и 17 на три входа, формирователь 18 импульса, линию 19 задержки, кодовые шины 20 числа, схемы «И 21 и 22, транзисторные ключи 23, шину 24 «земля.

В предлагаемом устройстве процесс преобразования при изменении скорости входного сигнала t/Bx (0. е превышающей веса младщего разряда hu за время переходных процессов в одном такте преобразования Тпр, происходит следующим образом.

В исходном состоянии (при ) уровень эталонного напряжения на выходе цифровых управляемых сопротивлений / в каждом разряде соответствует весу разряда и формируется под действием управляемых сигналов с выходов 3 а 4, предшествующих разрядов, подключающих с помощью соответствующих ключей 23 сопротивления 1 к шине 24, при этом триггеры 2 установлены в состояние «нуль сигналом по шине 7.

Характерными уровнями квантования входного сигнала в процессе преобразования для данного устройства являются

t/Bx 2a/iu t/Bx(2a+l)/i«,

, 1,2...., 15.

где

Для четных уровней квантования факт равенства уровня эталонного напряжения и выходного сигнала фиксируется схемой 8 сравнения в г-ом разряде ().

При положительном знаке производной входного сигнала код, соответствующий предшествующему уровню эталонного напряжения, в триггерах 2 устанавливается: в t-ом разряде - «нуль, в последующих - «единица. Схема «И // в t-ом разряде по одному входу подготовлена сигналом с выхода 4 для распространения сигнала с выхода 9 в последующие разряды при формировании кода. Схема «И 12 в i-OM разряде не подготовлена по одному входу сигналом с выхода 3 для распространения сигнала с выхода 10. Сигнал факта равенства с выхода Р в f-ом разряде поступает на вход схемы «И 11 и схемы «ИЛИ 13. По окончании переходных процессов в схеме «И 11 (тц) и схеме «ИЛИ 13 (TIS) в 1-ом разряде и параллельно в схемах «ИЛИ 14 () последующих разрядов код в триггерах 6 соответствующих разрядов устанавливается одновременно. Под действием сигналов с выходов 5 и 4 i-TO разряда соответствующие транзисторные ключи 2с в младших по значимости разрядах подключают сопротивления 1 к шине 15 (т2з+Т1). Знак приращения уровня эталонного напряжения определяется знаком производной входного сигнала.

Одновременно ключи 23, управляемые сигналами с выходов 3 и 4 каждого последующего после i-ro разряда, подключают цифровые управляемые сопротивления 1 в младших по значимости разрядах к шине 24 с помощью соответствующих |слючей 23. Знак приращения уровня эталонного напряжения противоположен знаку производной входного сигнала. Схемы 8 сравнения последующие после i-ro разрядов фиксируют превышение уровня эталонного напряжения входного сигнала. Однако распространение сигнала с выхода 10 по окончании переходных процессов в схемах 8 сравнения (tg) /-го разряда () в триггеры 2 младших по значимости разрядов исключается сигналом с выхода 3 в /-ом разряде.

При отрицательном знаке производной входного сигнала процесс преобразования аналогичен, за исключением того, что сигнал факта равенства распространяется с выхода 10 i-ro разряда в последующие через схемы «И 12 () и приводит в противоположное состояние триггеры 2 через схемы «ИЛИ 13 по раздельным входам 6.

Продолжительность процесса преобразования на четном уровне квантования без учета переходных процессов в схемах 8 сравнения, последующих после t-ro разрядов, ограничивается одним шагом независимо от числа разрядов выходного кода и определяется соотнощением

SP + ч + +t-Ь- «1 + 1Если переходные процессы в схемах 8 в последующих после i-ro разрядах не закончились до момента начала процесса преобразования на следующем нечетном уровне квантоваиия, то происходит их наложение.

Предположим, что после первого шага в процессе преобразования на четном уровне квантования схема 8 сравнения i-ro и последующих младщих разрядах находится в состоянии «единица, триггеры 2 в i-ом разряде - в состоянии «единица, а в последующих младших разрядах - в состоянии «нуль. Несоответствие состояния схемы 8 сравнения и триггера 2 в младшем разряде фиксируется

схемой «И 16, на входы которой с выходов 9 и 10 схемы 8 сравнения поступают уровневые сигналы.

При наложении переходных процессов, схема 8 сравнения, фиксируя факт равенства

уровня эталонного напряжения и входного сигнала, не изменяет своего состояния.

Несоответствие состояния схемы 8 и триггера 2 в младшем разряде выявляется импульсным сигналом, поступающим на третий

вход схемы «И 16. Импульсный сигнал формируется формирователем 18 при изменении состояния триггера 2 на предшествующем уровне квантования и поступает на вход схемы «И 16 с задержкой в линии 19 задержки

на время, необходимое для окончания переходных процессов в транзисторных ключах 23, управляемых сопротивлениях /, схемах 8 сравнения. Импульсный сигнал с выхода схемы «И 16 () через схемы «ИЛИ 13

и раздельный вход 5 переводит триггеры 2 в соответствующее схеме 8 состояние.

При входном сигнале с отрицательной производной несоответствие состояний схемы 8 сравнения и триггера 2 в младшем разряде

выявляется схемой «И 17.

Продолжительность процесса преобразования на нечетном уровне квантования при наложении переходных процессов определяется соотношением

111

при 8 +п .

Для нечетных уровней квантования при условии, что переходные процессы на предшествующем уровне квантования закончились, процесс преобразования ограничивается младшим разрядом. Факт равенства уровня эталонного напряжения и входного сигнала фиксируется схемой 8. При положительном

знаке производной входного сигнала с выхода 9 сигнал факта равенства с задержкой по отношению к началу процесса преобразования на длительность переходных процессов в схеме 8 (TS) последовательно проходит в младшем и старшем разрядах постоянно подготовленных по одному входу схему «И // (тп), схему «ИЛИ 13 (т1з) и переводит триггер 2 (тг) по раздельному входу 5 импульсным сигналом в соответствующее схеме 8 состояние.

При отрицательном знаке производной входного сигнала с выхода 10 сигнал факта равенства поступает на схему «И 12 (Ti2 Tii). Под действием импульсного сигнала триггер 2 с выхода схемы «ИЛИ 14 {т14 Т1з) переходит в соответствующее схеме 8 сравнения состояние на вход 6.

Процесс преобразования является однощаговым, его продолжительность на различных характерных уровнях квантования отличается на время переходных процессов в ключах 23

и сопротивлениях 1 (Т23 + Т1).

Для расчета максимальной частоты преобразуемого входного сигнала принимаем Тпр Тпр.ц. Запаздывание установления кода в триггерах 2 на различных уровнях квантования (тк) постоянно и не зависит от числа разрядов устройства.

Для считывания кода, сформированного в триггерах 2 в кодовые щины 20, в каждом разряде сигнал с выхода 3 подается на один из входов схемы «И 21, а с выхода 4 - на один из входов схемы «И 22. На другой вход схем «И 21 и 22 подается сигнал опроса, сформированный формирователем 18 при изменении состояния триггера 2 в младщем разряде. Процесс считывания кода, продолжительность которого (тс„) постоянна и не входит во время Тпр, может осуществляться в течение времени TS при преобразовании входного сигнала на следующем уровне-квантования.

Считывание кода с выходов 3 и 4 по окончании переходных процессов полностью исключает ошибки из-за наложения импульсов считывания на переходные процессы в тригге5 pax 2. Запаздывание выходного кода в щинах 20 по отнощению к началу процесса преобразования определяет динамическую погрешность преобразования устройства и складывается из времени Тк+Тс„ . Отнесение кода на

0 шинах 20 при регистрации к моменту начала процесса преобразования, ввиду постоянства Тк-fTcj, на различных уровнях квантования, позволяет исключить составляющую динамической погрешности из общей погрешности

преобразования.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий в каждом разряде схему сравнения, триггер, схемы «ИЛИ, входы которых соединены с выходами схемы сравнения старшего разряда и с выходами схем «И предыдущих разрядов, а выходы подключены ко входам

5 триггера, схемы «И, соединенные с выходами триггера, цифровые управляемые сопротивления и ключи, подключенные к выходам триггеров предыдущих разрядов, отличающийся тем, что, с целью повышения быстродействия

0 и точности преобразования, в младшем разряде выходы схемы сравнения подключены ко входам четырех схем «И, выходы которых через схемы «Р1ЛИ соединены со входами триггера, вторые входы двух схем «И через

5 линию задержки подключены к выходу формирователя импульсов, третьи входы двух схем «И соединены с выходами триггера и входами формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1978 |

|

SU869021A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU369702A1 |

| Параллельно-последовательный преобразователь напряжения в код | 1982 |

|

SU1039027A2 |

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

Авторы

Даты

1973-01-01—Публикация