OQ СО

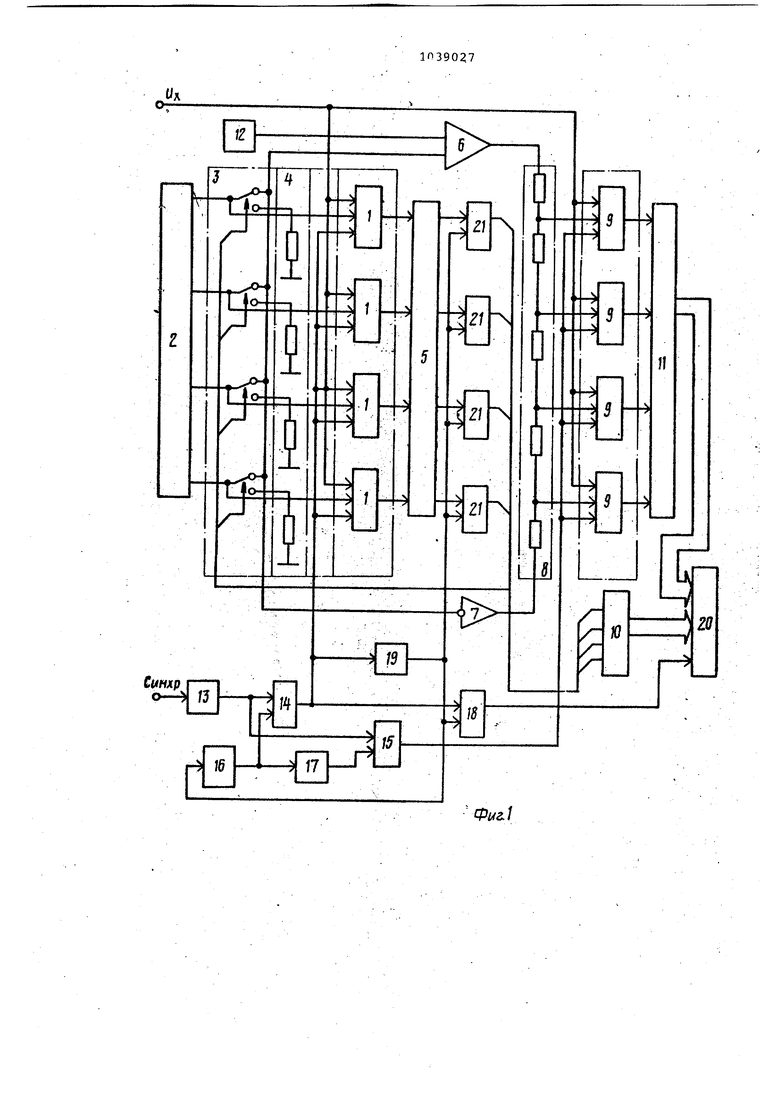

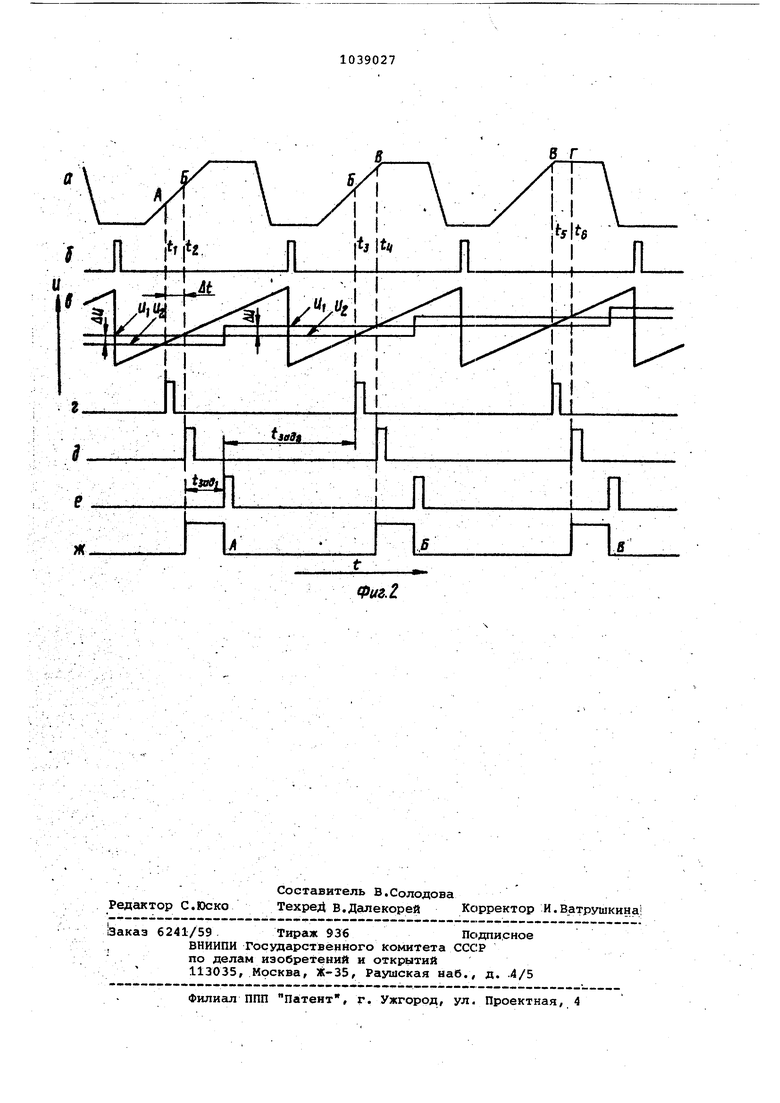

to . Изобретение относится к аналогоцифровой вычислительной технике и может быть использовано при автоматическом измерении широкополосньк периодических сигналов, По основному авт.св. № 513490 известен параллельно-последовательный преобразователь .напряжения в код, содержащий источник эталонных напряжений, выходы которого соединены с одними входами компараторов первой ступени, вторые входы которых подключены к источнику преобразу емого напряжения, и с входами ключей, управляющие входы которых и входы шифратора первой ступени соединены с выходами устройства выделения старшей единицы, входы последнего подключены к выходам ко:мпара-1 торов первой ступени, компараторы второй ступени, одни входы которых соединены с выходом источника преоб разуемого напряжения, другие - с вых дами последовательного делителя напряжения, а выходы - с входами шифр тора второй ступени, суммирующий и инвертирующий операционные усилители и- резисторы, включенные между об щей шиной и первым выходом ключей, вторые выходы которых через инвертирующий операционный усилитель под ключены к одному входу последователь ного делителя напряжения, второй вх которого соединен с выходом суммиру щего операционного усилителя, один вход последнего подключен к выходу дополнительного, эталонного источника, а второй вход - к вторым выходам ключей. Недостатком устройства является высокая динамическая погрешность пр образования в режиме амплитудно-вре менного квантования сигнала. При амплитудно-временном квантов нии непрерывного сигнала производит ся его преобразование в последовательность цифровых кодов, соответст щих мгновенным значениям измеряемог сигнала в фиксированные моменты вр мени. В данном преобразователе межд моментом определения старших разряд выходного кода и моментом определения младших разрядов с помощью компараторов второй ступени должно про ти определенное время, определяемое длительностью переходных процессов переключения ключей и установления выходного напряжения инвертирующего и суммирующего усилителей. Динамическую, ошибку, обусловленн временем преобразования, можно оценить по следующей формуле Аин-1 .) . где Tjj - апертурноё время применяе мых компараторов; Тзк - время задержки компаратор Т, время задержки шифратора; Т. - время установления переходных процессов переключения ключей и выходного напряжения усилителей; 5 - скорость изменения сигнала. При высокой скорости нарастания измеряемого сигнала младшие разряды выходного кода будут определяться неверно, при этом ошибка в опре-. делении--мгновенного значения сигнала может достигать преобразования компараторов первой ступени. Цель иг1Обретения - уменьшение ди- . намической погрешности.. Для достижения поставленной цели в параллельно-последовательный преобразователь напряжения в код введены генераторы пилообразного и ступенчатого изменяющегося напряжений/ два элемента сравнения, регистр, вычитающее устройство, тригггер с включенным параллел ьно его входам элементом задержки и фиксирующие триггеры, управляющие входы которых подключены к первому входу триггера и входу генератора ступенчато изменяющегося напряжения, выход которого непосредственно и через вычитающее устрой,ство соединен с первыми входами первого и второго элементов сравнения соответственно, вторые входы которых подключены к выходу генератора пилообразного напряжения, при .этом выход первого элемента сравнения соединен непосредственно с входами опроса компараторов первой ступени и через триггер - с входом записи регистра, первый и второй входал которого соединены с выходами шифраторов первой и второй ступени соответственно, а выход второго элемента сравнения -: с входами опроса компараторов второй ступени, причем выходы устройства вьщеления старшей единицы соединены с управляющими входами ключей и входами шифратора первой ступени через фиксирующие триг геры. Компараторы имеют дополнитель 1ЫЙ вход спроса, компаратор изменяет свое состояние, только при наличии импульса на входе опроса. Таким образом, можно зафиксировать состояние компаратора, т.е. произвести сравнение входного сигнала с эталонными напряжениями, в определенный момент времени. Генератор пилообразного напряжения, элементы сравнения и генератор ступенчатоизменяющегося напряжения образуют систему автосдвига, синхроимпульсов, обеспечивающую стробоскопический режим работы пре образователя. Введением элемента задержки, регистра, фиксирующих триггеров обеспечивается распределение синхроимпульсов, при котором определение старших и младиих разрядов происходит в разных периодах входного сигнала, с определенной задержкой относительно начала периода. Положительный эффекте, таким образом, достигается тем, что старшие и младшие разряды кода оцределяются в одной эквивалентной точке входного сигнала, и динамическая погрешность определяется только апертурным временем компаратора . о( . т.е. исключается составляющие Тьк поскольку процессы ,шифрации и установления переходных jipoueccoB протекают в течение перио fla входного сигнала. « На фиг. 1 изображена функциональ ;ная схема предлагаемого преобразователя, на фиг.2 - временные диагра мы, поясняющие его работу. Преобразователь содержит компара торы 1 первой ступени, источник 2 эталонных уровней, ключи 3, резисто ры 4, устройство 5 выделения старше единицы, суммирующий усилитель 6, инвертирующий усилитель .7, последо|ва гельный делитель 8 напряжения, ко параторы 9 второй ступени, шифратор 10 первой ступени, шифратор 11 второй ступени, дополнительный эта. лонный источник 12,генератор 13 пиЛ образного напряжения, элементы 14 и ,15 сравнения, генератор 16 ступенчатоизменяющегося напряжения, вы читающее устройство 17, триггер 18 элемент 19 задержки/ регистр 20, фи сирующие триггеры 21. . На вход измеряемого сигнала Uy поступает периодический сигнал (фиг.2 ) на вход генератора 13 пиШообразного напряжения подается последовательность синхроимпульсов (фиг.2 б) сопровождающих измеряемы .сигнал. При поступлении очередного синхроимпульса генератор 13 пилообразного напряжения вырабатывает пилообразные импульсы (фиг.2 BJ , кот рые сравниваются элементом 14 с напряжением, снимаемым с выходом генератора 16 (Ц на фиг.25)и элементом 15с напряжением, снимаемым с в хода вычитающего устройства 17 (U2 на фиг„2 S) . В моменты равенст ,ва напряжений на входах элементОв--1 :и 15 последние формируют на своих выходахимпульсы (фиг.2 г с выход .элемента 15 и фиг.2 Э - с выхода . элемента 14 ). Изменение выходного напряжения .генератора 16 ступенчато изменякицегося Напряженик Ц (фиг.2 5) проис-. ходит скачком на величину л при поступлении на вход генератора 16 им- пульса (фиг.2 е , представляющего собой импульс (фиг.2д/ , задержанны навремяtjp,- элементом 19 задержки. С каждьтм периодом измеряемого сигнала задержка импульсов (фиг. ;сительно синхроимпульсов (фиг.2& увеличивается на время ai ,.определявмое величиной приращения 4U напряже- . ния и и крутизной s пилообразного напряхсения с выхода генератора 13 пилообразного напряжения. С помощью вычитающего устройства 17 из -напряжения Uxj вычитается постоянная величина л и I, и напряжение с выхода вычитающего устройства 17 равно О, ( (фиг. Благодаря наличию вычитающего устройства импульсы (фиг.21, ;с выхода элемента 15 постоянно опережают импульсы (фиг.2д)на время, равное -at . Импульсы (фиг.2д поступают на входы опроса компараторов 1, тем самым фиксируя единичный код старших раэрядов, соответствующий мгновенному значению напряжения измеряемого сигнала в момент- времени 2 точка Б на измеряемом сигнале,(фиг.2а)на вы- ходах компараторов . По номеру старшего сработавшего компаратора устрой-, ство 5 выделения старшей единицы формирует код с единицей в одной позиции, соответствующей старшему сработавшему компаратору. Этот код поступает на входы фиксирующих триггеров 21, выполненных по схеме триггера-защелки. На управляющие входы , триггеров 21 поступает импульс (фиг.2е)с выхода элемента 19 задержки. При поступлении импульса (фиг.2 на выходах триггеров 21 фиксируется код, сформированный устройством 5 выделения старшей единицы. Этот код подается на шифратор 10 первой ступени , который формирует код старших разрядов, и на управляющие входы ключей 3; при этом ключ, соответствующий старшему сработавшему-компаратору, отключает соответствующий выход эталонного источника 2 от резистора 4 и подключает его к входам усилителей 6 и 7. Номинальное напряжение дополнительного эталонного источника 12 равно величине кванта первой ступени ( . На выходе инвертирующего усилителя 7 напряжение по модулю равно -f , где 1 - номер старшего сработавшего компаратора. Аналогично, на выходе суммирующего усилителя 6 модуль напряжения равен (i+ i) , на Входах делителя 8 напряжения будут присутствовать два напряжения: одно равно ближайшему меньшему, чем и)( напряжению эталонного источника 2, другое - ближайшему большему. Разность между соседними эталонными уровнями, подаваемыми с выходов делителя 8 на входы компараторов 9 равна величине кванта второй ступени. Импульсы (фиг. поступающим с выхода элемента 15 на входы опроса компараторов 9, фиксируется состояние компараторов 9/ единичный код с их выходов, соответствующий мгновенному значению напряжения измеряемого сигнала в точке Б (момент времени tj фиг. 2 а), подается на шифратор 11 второй ступени, который формирует код младших разрядов. Импульсом Б (фиг.2, сформированном из импульсов (фиг.2 д и 2ejc помощью триггера 18, полученный код, соответствующий мгновенному значению сигнала в точке Б, заносится в выходной ре- гистр 20. Далее преобразование мгноЁенных значений периодического сигнала (фиг. 2а происходит аналогично: в момент времени t. определяется код старших разрядов значения сигнала в точке В, в момент времени tr- формируется код младших разрядов, соответствующий значению сигнала в точг ке В (фиг.2с|| полученные коды заносятся в регистр 20 импульсом В (фиг.2Ж, образуя новое значение кода выборки сигнала. Смена кодов, соответствующих значениям выборок, происходит по импульсам (фиг,2ж|с частотой следования измеряемого сигнала.

Элемент задержки необходим дця того, чтобы предотвратить изменение старших и младших разрядов кода в момент записи в регистр 20.

Таким образом, в предлагаемом преобразователе реализован стробоскопический режим работы. При этом в течение периода измеряемого сигнала формируется один полный цифровой

код, соответствующий мгновенному зна чению сигнала, сигнал квантуется с эквиваленгньдм периодом квантования ,. равным it .

Благодаря синхронизации компарато ров 1 и 9 старших и младших разрядов старшие и младшие разряды выходного кода определяются в одной точке измеряеморо сигнала, и динамическая погрешность .преобразрвания Определяется только апертурной погрешностью компараторов, обычно имеющую малую величину.

. При скорости нарастания входного сигнала В/мкс динамическая погрешность предлагаемого устройства 4д1,нг мВ, динамическая погрешность прототипа

VH t 42(о..),

Т.е. в сравнении с прототипом имеется выигрыш в точности преобра;зова ния в 160 раз.

Процессы переключения Ключей и установления выходного напряжения Суммирующего и инвертирующего усилителей протекают в течение време- ; ни между импульсами опроса(.2д} ;И не оказывает влияния на динамическую погрешность ..преобразования Г Это дает иозможность дополнительно снизить общую погрешность преобразования путем применения менее быстродействующих, зато более точных усилителей и ключей.

в г

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1980 |

|

SU940295A2 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2121753C1 |

| Устройство для измерения погрешности цифро-аналоговых преобразователей | 1982 |

|

SU1112546A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1029410A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Логарифмический преобразователь напряжения в код | 1979 |

|

SU917337A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД по авт.св. Ю 513.490, о т л и- . чаю щи и с я тем, целью уменьшения динамической погрешности , введены генераторы пилообразного и ступенчатого изменяющегося напряжений, два элемента сравнения, регистр, вычитающее устройство, триргер с включенным параллельно его вхо дам элементом задержки и фиксирующие триггеры, управляющие входы которых подключены к первому входу триггера и входу генератора ступенчато изменяющегося/Напряжения, вы;ход которого непосредственно и че|рез вычитающее устройство соединен ,с первыми входами первого и второго элементов сравнения соответственно, вторые входы которых подключены к выходу генератора пилообразного напряжения, при этом выход первого элемента сравнения соединен не- посредственно с входами опроса компараторов первой ступени и через триггер -. с входом записи регистра , первый и второй входы которого .: соединены с выходами шифраторов первой и второй ступени соответственно, а выход второго элемента сравнения - с входами опроса ком- параторов второй ступени, причем вы(Л ходы устройства выделения старшей единицы соединены с управляющими входами ключей и входами шифрато|ра первой ступени через фиксирую-щие триггеры. .

Фиг2

| Параллельно-последовательный преобразователь напряжения в код | 1974 |

|

SU513490A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-08-30—Публикация

1982-02-23—Подача