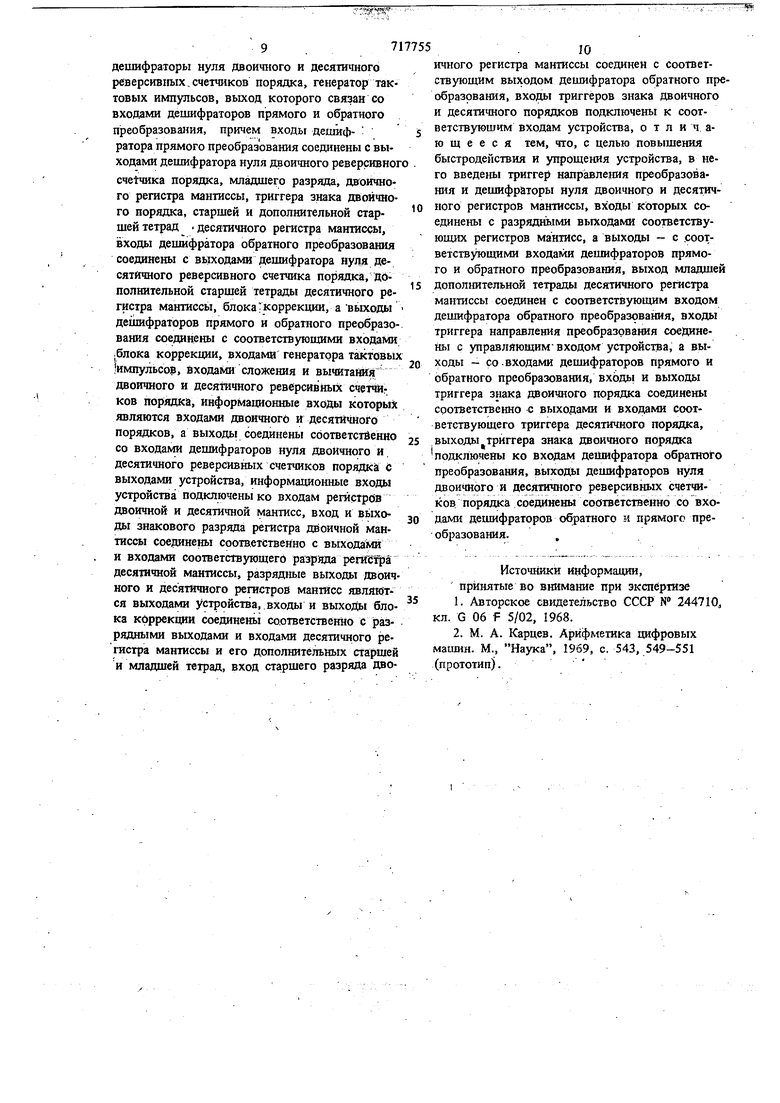

V .37 ррйства, информационные входы устройства подключены ко входам регистров двоичной и десятичной мантисс, вход и выходы знакового разряда регистра двоичной мантиссы соединены соответственно с выходами и входами ответствующего разряда регистра десятшшой мантйсЛ, разрядные выходы двоичного и десятичного регистров мантисс являются выходами устройства, входы и выходы блока кор-, рекции соединены соответственно с разрядными выходами и входами десятичного регистра . мантиссы и его дополнителыагх старшей и младшей тетрад, вход старшего разряда двоичного регистра мантиссы соединен с соответстйвующим выходом дешифратора обратного / преобразования, входы триггеров знака двоич-. ного и десятичного порядков подкйюченьт к соот ветстйующим входам устройства 2. Однако, алгоритм преобразования в известном устройстве не содержит случая преобразования чисел с нулевой мантиссой, что приводат к непроизводительной работе оборудования во время ее преобразования и к снижению быстродействия устройства. .При преобразовании десятишогЬ порядка в двоичный, в зависи рт знака его в обоих счетчиках (двричном и десятичном) должш зьп1олня11.сй ЬпераЦйи сложения и вычитания, что усложняет устройство. В схеме для преобразования мантисс, двоичный регистр снабжен цепями сдвига влево на один двоичный pa3pJ3Ui, kbiopbie нужны лишь для преобразования цель1х чисел из дв(эйчнрй системы Ьчисления в десятичную. Поскольку мантисса числа в форме с плавающей запятой является правильной дробью, необхрдимость в указанных цепях для преобразования таких шсел отпадаег. Целью настоящего изобретения является по вышение быстродействия и упрощение устройства. . Поставленная цеНь достигается тем, что в устройство введены триггер направления преобраз6)ванИя и дешифраторы нуля: двоичного и десятичного регистров мантиссы, входы кото рых соединены с разрядньтми выхрдами соответствующих регистров, мантиссы, а выходы . с соответствую1цими входами дешифраторов прямого и обратного щзеобразования, выход ;младшей дополнительной тетрады десятичного регистра мантиссы соединён.с соответствующим входом, дешифратора обратного преобразования входы триггера направления преобразования соединены с управляющим входом устройства, а выходы - со входами дешифраторов прямр го обратного преобразования, входа и выходы .триггера знака двоичного порядка соеди нены соответственно с выходами и входами соответствующего триггера десятичнбгд порядка, выходы триггера знака двоичного Порядка подключены ко входам дешифратора обратноto преобразования, выходы дешифраторов нуля двоичного и десятичного реверсивных счетчиков порядка соединены срответственно со вхоДами дешифраторов обратного и прямого преобразования. На чертеже представлена блок-схема устройства для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой, содержащая: двоичный 1 и десятичнь1й 2 регистры мантисс, дополнительную ctapшук) 3 и допол1штельную младшую 4 тетрады десятичного 2 регистра мантиссы, блок 5 коррекции, двричньШ 6 и десятичный 7 реверсивные счетчики порядка, триггеры 8, 9 знака г двоичного и соответственно десятичного . Дешифраторы нуля 10 и 11 соответственно двоичного и десятичного регистров мантиссы, дешифраторы нуля 12 и 13 соответственно двоимого и десятичного реверсивных счетчиков порядка, дешифраторы 14 и 15 соответственно прямого и обратного преобразования, генераторы 16 тактовых импульсов,.триггер 17 направления преобразования, входы 18 и 19 регистров соответственно двоичной и десятичной мантисс, вхрдь 20 и 21соответственно двоичногр и десятичного порядков, входы 22 и 23 триггеров знака соответственно, двоичного и десятичного порядков, выходы 24, 25, 26, 27 .: устройства, управляющие входы 28 устройства, триггеры знаков двоичной 29 и десятичной 30 мантисс. -::. -- .:, - - . Алгоритмы перевода чисел из двоиадой стёмы счисления в десятичную сводятся к следую1цему. . ., Сначала производится преобразование даоичнрй мантиссы М, в десятичную М, „ подачей ее цифр, начиная с младшей, в десятичный регистр, где вьшоЛняется последовательное деление ее на два. При т-разрядной мантиссе двоичного числа преобразование заканчивается через tr тактов, и в десятичном регистре оказывается мантисса Мц,, а в двоичном - .нуль. После этого выполняется преобразование порядков. Эта процедура зависит от знака двоичного порядка. Если двоичный порядок полояштелен, мантисса М,в умножается на два до тех пор, пока произведение М,о не станет больще единицы. Одновременно с каждым удвоением из двоичного йорядка вычитается единица. После переполнения мантисс умножение прекращается и выполняется нормализация полученного произведения; сдвиг вправо на один десятичный разряд и добавление единицы к десятичному порядку. Процесс продолжается до тех пор, пока двоичный порядок не станет равен нулю. В случае, если двоичный порядок отрицателен, мантисса М,, последовательно делится на два, пока старший десятичный разряд частного не станет равен нулю. При каждом делении к двоичному порядку добавляется едини-. ца. После нарушения нормализации впразо деление прекращается и полученное частное нормализуется: сдвигается влево на ойан ДёШйЧньш разряд, а к десятичному порядку добав ляется -1, Процесс заканчивается, как только двоичный порядок станет равен нулю. Если двоичная мантисса равна нулю, пргобразование мантисс не вьтолняется. Результат считается равным нулю. Рассмотрим работу преобразователя для Дву режимов: прямого преобразования из двоичной системы счисления в десятичную и обратного - из десятичной системы счисления в двоичнуй. Вид преобразования задается триггером 17, который сигналом от устройства управления ЦВМ устанавливается в состояние О - при прямом и в состояние I - при обратном преоб разовании.; Преобразовавде из двоичной системы счисления в десятичную. Работой устройства зпрговляет дешифратор 14. В зтом случае триггер 17 устанавливается в состояние О и по шинам 18, 20, 22 на вход преобразователя передается исходйое двоичное число. Десятичный же регистр и счедгчик устанавливаются в нулевое состояние по входам 19, 21, 23. На выходах дешифраторов 10 и 12 появляются сигналы о том, что двоичный регистр и счетчик находятся в ненулевом состояиии. Знаки мантиссы и порядка из триггеров 29 и 8 передаются на вхоДы триггеров 30 и 9 соответственно. Если двоичное число или его мантисса рав нЫ нулю, дешифратор 14 выдает сигнал Конец преобразования. При этом десятичное, число также равно нулю. Если же нулю равен тол ко порядок двоичного числа, то преобразование выполняется так же, как и в общем случае, который описьшается ниже. В общем случае, когда мантисса М, и поря док Р, не равны нулю, дешифратор 13 запускает генератор тактовых импульсов и начинает сдвиг мантиссы М, на один разряд вправо. Младшие разряды мантиссы Mj проходят на вход блока 5 коррекции и через него - йа вход первого разряда регистра 2. При зтом происходит деление на два в десятичном регистре. После m тактов Сдвига и деленияпо- полам в десятичном регистре оказывается преобразованная мантисса М,о, а в двоичном регистре - нуль. Дешифратор 14 прекращает преобразование мантисс. Дальнейшей работой преобразователя кодов управляет триггер 8 знака порядка. Если он в нулевом состоянии (порядок положительный), то дешифратор 14 начинает выполнять удвоения десятичной Mairmccbl, если в единичном - Дешифратор 14 вьшолняет последовательное деление- на дв мантиссы М,,. Пусть ДВОИЧ1П.1Й порядок положителен. В этом случае дешифратор 14 через блок коррекции 5 вьшолняет последовательное умножение десятншой мантиссы на два с одновременным вычитанием единицы из двоичного б счетчика порядка. Как только в результате умножешя произойдет переполне1ше Мантисс в регистре 2, дешифратор 14 прекращает удвоение и вьшолняет нормализацию десятичной мантиссы: сдвиг вправо на один десятичньй разряд и добавление едйнйЩ) к счетчику 10. Затем снова выполняется последовательное умножение на два до тех пор, пока в даоичном 6 не появится нуль и не будет получена нормализованная мантисса М, о. . Де1Ш1фратор 14 вьщает сигнал Конец преобразования и отключает генератор 16. Предположим теперь , что исхоядое двоИчное число имеет отрицательный порядок. В этом случае после преобразования мантисс дешифратор 14 через блок 5 коррекции выполняет последовательное деление десятичной мантиссы на два с одновременным вычитавшем единицы из дбсолютной величины двоичного порядка (эта величина хранится в счетчике б порядка, а знак порядка - в триггере 8). . - . Процесс продолжается- до нарушения нормализации десятичной мантиссв - появления нуля в старшей декаде регистра 2. При этом дешифратор 14 прекращает деление и выполняет нормализацию: сдвиг Влево на один десятичный разряд и добавлеш1е 1 к абсолютной величине порядка (знак минус присвоен ему в самом начале преобразования посде установки триггера 9 в состояние .. Затем дешифратор 14. начинает новый цикл дёле1шя и так до тех пор, пока в Двоичном счетчике не появится нуль и не будет получена нормализованная мантисса М,о, Дешифратор 14 выдает сипйл Конец преобразова дая и отключает генератор 16. Если порядок исхощгаго двоичного шсла , а мантисса М, э О, то с преобразованием MaHTifcc процесс перевода заканчивается и дешифратор 14 сразу выдает сишал Конец преобразования. ; 7 Мантисса М,о и порядок Р,„ полз {еш1ого десятичного числа снимаются с выходных 1Ш1н Ж27г;:::;:- -.- Преобразование из десятичной системы счисления 1В дйоштуго.у: Работой устройства управляет деишфратор 1 Такое преобразование удобнее нагииать с перевода порядков. Триггер 17 для этого устшшливается в срстояше I. По шинам 19, 21, 23 на вход преобразователя подаётся исх)Д11ое десятичное число. Двоишйш регистр и счетадк по шинам 18, 20, 22 устанавливается в нулевое состояние.- - На выходах дегпифраторов И ji 13 появ.ляютсй Сигналы о том, что десятичный регистр и счетчик находятся в ненулевом состояШй.Зна ки маимссы и порядка из триггеров 30 и 9 передаготся на входы триггеров 29 8 соот вйственно. Если десятичное число или его гиантисса равны нулю, дешифратор 15 выдает сигнал Конец преобразования. В этом случае двоичное число будет также равно нулю При ну еВом йорядке и нензшевой мантиссе преобраШйа 5й:ё;начийаетсй с псревйда MaiftHcc:, В общем случае, когда мантисса М,„ О и порядок Р,о , дешифратор 15 запускает тейёратор тактовых импульсов. Предположим/4td йдрвдрк десятичного, Ч11С ла положителен. При этом Деиш $ратор 15 через блок .5 J;Ыпqлпяeт сдвиг десятечной мать тйссы ни сдан разряд влево с одновременным вычитание, м единицы из Де.сйтичного порядка. Зате деип фратор 15 через блок 5 вьтолняет последоватёлБное деление сдвинутой майтоссы .на два с одновременным добавлением еданицы к двоичному счетчику порядка. Процесс деления продолжается до тех пор, пока не будет устранено HapyEiefflie нормализаида в десятичном регистре. После этого дешифратор 15 выполняет очередной сдвиг десятичной мантиссы влево и так до тех пор, пока в десятичном счетчике не окажется iyrn., а десятиШая мантисса не будет нормализована. Если исходный десятичный порядок отрица телен, го дешифратор 15 через блок 5 вбШолня ет сдвиг дёсят11Ч1юй ifirBKiCbf М Itfoffpisjpara вправо. При это.м младшая цифра ее пша:дает в дополнительную младшую тетраду 4. Одновременно со сдвигом дешифратор 15 осуществляет -з леньшение десятитаого порядка на еди нйцу. , : : .. .....,, Затем дешифратор 15 через блок 5 вьшолнябт последовате11ьное удвоение десятичной ма тиссы с одновременным увеличением на единицу абсолютной вел11чины двоичного порядка (знак минус присвоен ему is самом начале прербраз&вания после устайЬйкй триггера 8 в состояниеЧ). Как только нарушение нормализации в регистре 2 будет устранено и в допотштельной младшей тетраде 4 будет нуль, деишфратор 15 начинает новый цикл преобразования поряд-: ков: сдвиг вправо и удвоения матгиссы. Процесс продолжается до тех пор, пока десятичньц порядок не станет равен нулю, а десятичная мантасса не будет нормализована. На этом преобразова 1ше порядков за1санчивается. Далее выполняется преобразование мантисс. При этом деишфратор 15 через блок 5 осуществляет последовательное деление на два в регистре 2. Цифра младшего разряда десятичной мантиссы после каждого такта деления дает очередную младшую цифру двоичной мантиссы. Эта цифра передается дешифратором 15 на вход старшего разряда регистра 17. После m тактов сдвига и деления в регистре 1 окажется преобразованная, двоичная мантисса. Перевод окончен. Дешифратор 15 вьщает сигнал Конец преобразования и отключает генератор 16. Полученное двоичное число снимается с шин 24, 26. Отсутствие цепей сдвига в двоичном регистре мантиссы упрощает устройство и повышает надежность еко работы за счет уменьшения ко личества элементов и связей меясду йими. Вьтолнение при перейоде порядков операций одного знака (только сложения или вычитания) над их абсолютными величниа(Сш также сокращает количество вхоДов у счетчиков порядков: предлагаемое устройство срдерЖ1ит на восемь таких входов меньше, чем известное. В известном устройстве анализ на нуль мантиссы не производится, что может привести к выполиению m бесполезных сдвигов в регистре 1 при преобразовании из двоичной системы счисления в десятичнзто, а также к m + 10 - 1 таких же сдвигов в регистре 2 при обратном преобразовашш, где К - количество разрядов в десятичном счетчике порядка. В предлагаемом устройстве, если мантисса исходного числа равна нулю, преобразование не выполняется, и результат также равен нулю. Это позволяет повысить быстродействие устройства при преобразовании чисел с кулевой мантиссой. Формула изобретения .,... Устройство для преобразования двоичного кода 8 десятичщ.1й и обратно для чисел с плавшощей запятой, содержащее двоичный и десятич10)1й регистры мантиссы, дополнительные старшую и младшую тетрады, десятичного реriiCTpa мантиссы, блок коррекции, двоичный и десятичный реверсивные счетчики порядка. 971 дешифраторы нуля двоичного и десятичного реверсивных,счетчиков порядка, генератор тактовых импульсов, выход которого связан со входами дешифраторов прямого и обратного преобразования, причем входы дешйфратора прямого преобразования соединены с выходами дешифратора нуля двоичного реверсивног c4et4HKa порядка, младшего разряда, двоичного регистра мантиссы, триггера знака двоичного порядка, старшей и дополнительной старшей тетрад -десятичного регистра мантиссы, входы дешифратора обратного преобразования соединены с выходами дешифратора нуля десятичного реверсивного счетчика порядка, дополнительной старшей тетрады десятичного регистра мантиссы, блокакоррекции, авыходы деишфраторов прямого и обратного преобразования соединены с соответствующими входами ;блока коррекции, входами генератора тактовых |импульсов, входами сложения и вычитанная двоичного и десятичного реверсивных счетчиг ков порядка, информационные входы которых являются входами двоичного и десятичного порядков, а выходы соединены соответственно со входами дешифраторов нуля двоичного и десятичного реверсивных счетчиков порядка С выходами устройства, информационные входы устройства подключены ко входам регистров двоичной и десятичной мантисс, вход и выходы знакового разряда регистра двоичной мантиссы соединены соответственно с выхода мм и входами соответствующего разряда региЩза десятичной мантиссы, разрядш 1е выходы Двоичного и десятичного регистров мантисс являются выходами устройства, входы и выходы блока коррекции соединены соответственно с разрядными выходами и входами десятичного регистра мантиссы и его дополнительных старшей и младшей тетрад, вход старшего разряда двоичного регистра мантиссы соединен с соответствующим выходом дешифратора обратного преобразования, входы триггеров знака двоичного и десятичного порядков подключены к соответствующим входам устройства, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, в него введены триггер направлешя преобразования и дешифраторы нуля двоичного и десятичного регистров мантиссы, входы которых соединены с разрядными выходами соответствующих регистров мантисс, а выходы - с .соответствующими входами дешифраторов прямого и обратного преобразования, выход младшей допол1штельной тетрады десятичного регистра мантиссы соединен с соответствзтощим входом дещифратора обратного преобразования, входы триггера направления преобразования соединены с управляющим- входом устройства, а выходы - со .входами дешифраторов прямого и обратного преобразования, входь и выходы триггера зшка двоичного порядаса соединены соответственно -с выходами и входами соответствующего триггера десятичного порядка, выходы триггера знака двоичного порядка подключены ко входам дешифратора обратного преобразования, выходы дешифраторов нуля двоичного и десятичного реверсивных счетчиков порядаса соединены соответственно со входами дешифраторов обратного и прямого преобразования., Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 244710., кл. G 06 F 5/02, 1968. 2.М. А. Карцев. Арифметика цифровых машш. М., Наука, 1969, с. 543, 549-551 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

Авторы

Даты

1980-02-25—Публикация

1977-03-25—Подача