эо

О)

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1988 |

|

SU1619414A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство для приема измерительной информации | 1985 |

|

SU1257689A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2011 |

|

RU2471287C1 |

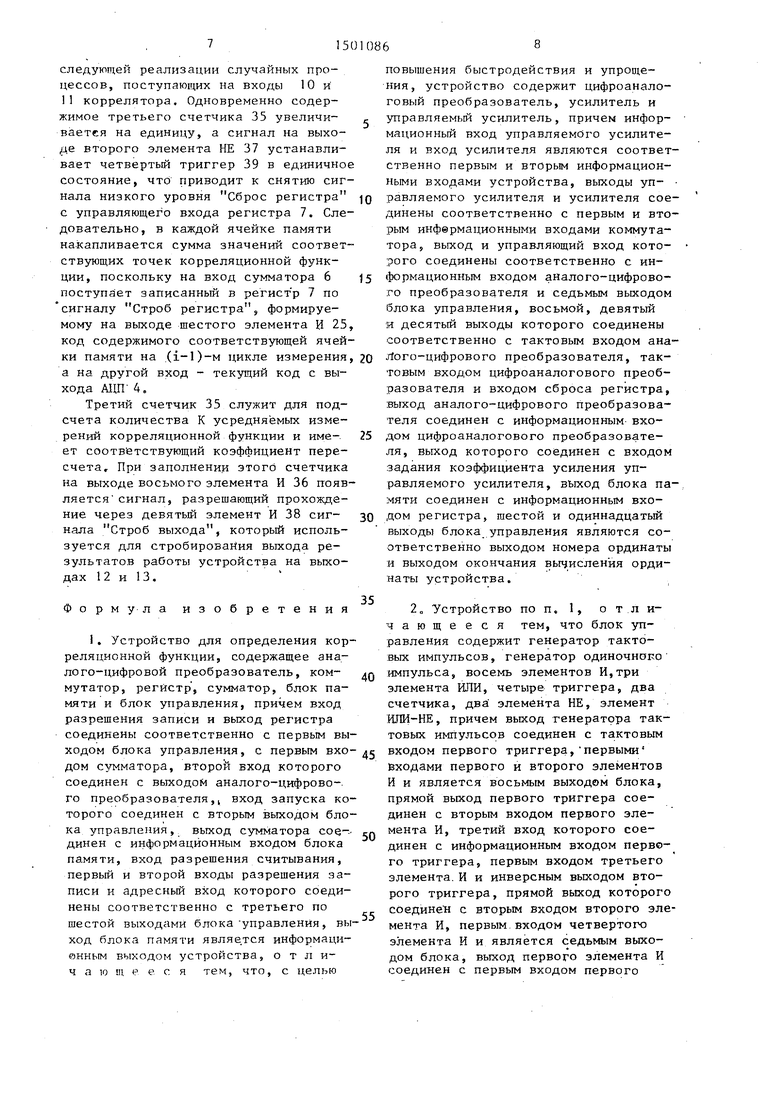

Изобретение относится к специализированным средствам вычислительной техники и предназначено для нахождения оценок корреляционной функции случайных процессов. Целью изобретения является повышение быстродействия вычислителения корреляционной функции и упрощение устройства. Устройство содержит управляемый усилитель 1, усилитель 2, коммутатор 3, аналого-цифровой преобразователь (АЦП) 4, цифроаналоговый преобразователь (ЦАП) 5, сумматор 6, регистр 7, блок 8 памяти, блок 9 управления. Суть изобретения заключается в том, что информационный вход ЦАП 5 связан с выходом АЦП 4, а выход управляет усилителем первого процесса сигналом, пропорциональным задержанному сигналу с выхода усилителя второго процесса. Это позволяет исключить аппаратное умножение ординат первого и второго процессов. Полученный сигнал, пропорциональный произведению указанных величин, преобразуется АЦП и подается через сумматор на блок памяти, на выходе которого после усреднения получается оценка корреляционной функции. 1 з.п. ф-лы, 2 ил.

фиг1

3150

Изобретение относится к специали- знрованн 1м средствам вычислительной техники и пре/и азначено для нахождения опенок корреляционной функции случайных процессов, например, с использованием датчиков, преобразующих физические ве;п1чины в электрический сигнал.

Цель изобретения - повышение бы- стродействия и упрощение устройства.

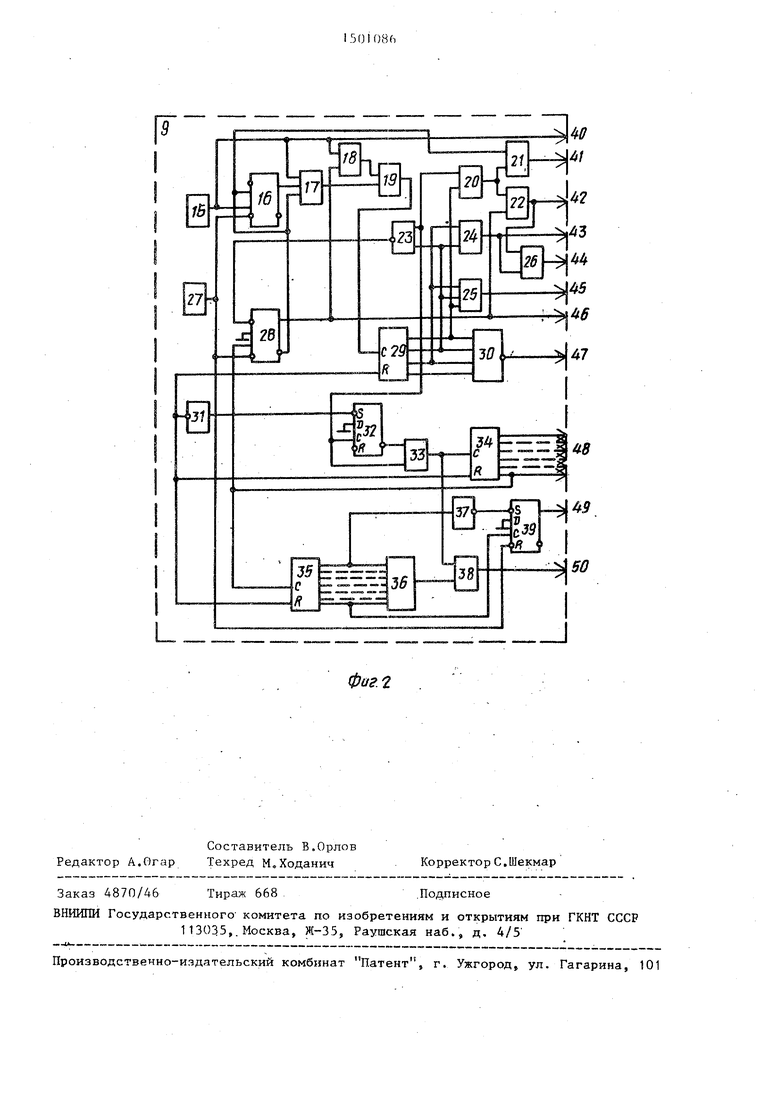

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока синхронизации.

Устройство содержит управляемый -усилитель 1, усилитель 2, коммутатор 3, аналого-цифровой преобразователь (А1Щ) 4, цифроаналоговый преобразователь (ПАИ) 55 сумматор 6, регистр 7, блок 8 памяти, блок 9 управления, первый 10 и второй 11 входы, информационный выход 12, выход 3 номера ординаты и выход 14 окончания вычисления ординаты.

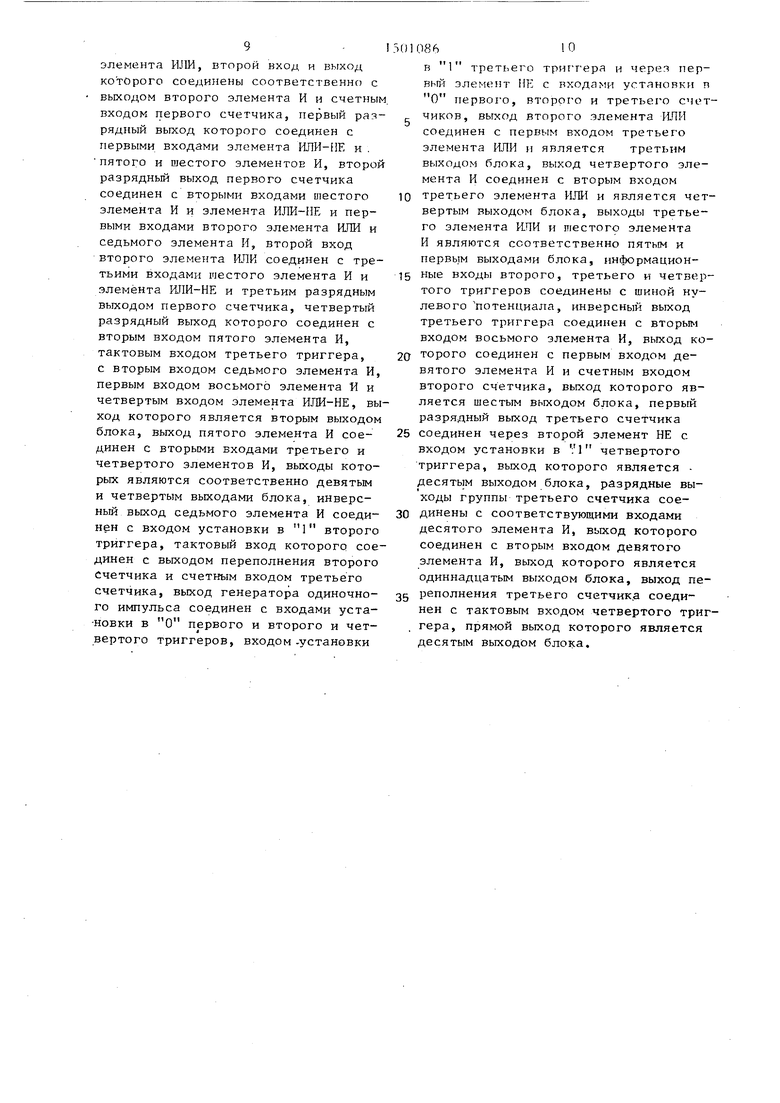

Блок 9 управления (фиг. 2) образуют генератор 15 тактовых импульсов, триггер 16, элементы И 17 и 18, элемент ИЛИ 19, элементы И 20-22, элемент И 23, элемент ИЛИ 24,- элемент И 25, элемент ИЛИ 26, генератор 27 одиночного импульса, триггер 28, счетчик 29, элемент ИЛИ-НЕ 30, элемент НЕ 3.1, триггер 32, элемент И 33, счетчики 34 и 35, элемент И 36, вто- рой элемент НЕ 37, элемент И 38, триггер 39, а также восьмой 40, девятый 41, четвертый 42, третий 43, пятый 44, первый 45, седьмой 46, второй 47, шестой 48, десятьш 49 и одиннадцатьй 50 -выходы.

Устройство работает следующим образом.

На первый 10 и второй 11 входы коррелятора поступают сигналы соответственно X(t) и y(t). В начале цикла определения корреляционной функции коммутатор 3 подключает усилитель 2 на вход AIJ,n 4, число М разрядов которого зависит,от требований к точности измерения. Рассмотрим случай с использованием восьмиразрядного АЦП с поразрядным преобразованием, При появлении сигнала Пуск АЦП на вы- ходе 47 блока синхро1 изации АЦП за 8 тактов выполняет операцию преобразования cnrHaj a y(t) в цифровую форму. Этот код с выхода А1Щ поступа

0

0

5

0 5 0

с

0

ет па ип(1ормационный вход ПАП 5 и по сигналу (л роб ЦАП па выходе 41 блока 9 управления заносится в ЦАП. После преобразования усилитель 1 управляется напряжением с выхода 11АЛ 5, пропорциональным сигналу усилителя 2, задержанным на время A t , задаваемое блоком синхронизации.

После переключения коммутатора 3 по сигналу на выходе 46 блока 9 сигнал с усилителя 1 первого процесса

пропорциональный произведению X(t)it У(), поступает на вход АЦЛ 4 и после преобразования в цифровую форму поступает на вход сумматора 6. Поскольку на инверсный управляющий вход регистра 7 с выхода 49 блока 9 поступает сигнал низкого уровня Сброс регистра, то на вход сумма- тора 6 поступает нулевой код и код на выходе сумматора равен коду АЦЦ 4, Наличие сигналов разрешения записи Запись и Выбор микросхемы соответственно на выходах 42 и 44 блока 9 управления обеспечивает запись этого кода в ячейку блока 8 памяти по адресу, установленному на выходе 48 блока управления, после чего значение адреса увеличивается на единицу. А1Щ 4 осуществляет следующий цикл преобразования, и в следу- . ющую ячейку блока 8 памяти записы- рается код, пропорциональный величине X(t) y(t+2A t ), т.е. вторая точка корреляционной функции. После записи значений N точек в блок 8 памяти цикл измерения корреляционной функции повторяется, но при этом по сигналам разрешения считывания на выходах 43 и 44 блока управления код, хранящийся в ячейке памяти, по текущему адресу поступает на вход регистра 7 и заносится в него по сигналу Строб регистра на выходе 45 блока управления, далее он поступает на вход сумматора бив каждую-ячейку записывается сумма текущего значения и значения на предыдущем цикле изме-- рения i-й точки корреляционной функции . I -

Таким образом, происходит накапливание К значений ординат корреляционной функции с целью получения усредненного значения в соответствии с формулой

. k Куч(й) i Xx(t).y(t-(-iA),

с 1 1

Для ввода значений точек корреляционной функции на последнем цикле измерения смена адреса сопровождается сигналом на одиннадцатом выходе 50 5 блока 9 управления и, соответственно, на выходе 1-4 устройства.

Блок 9 управления (фиг. 2) работает следующим образом.

Генератор 27 одиночного импульса 10 устанавливает в нулевое состояние первый 29, второй 34 и третий 35 счетчики и D-триггеры 16, 28 и 39. Третий триггер 32 устанавливается в единичное состояние. Первый элемент 15 НЕ 31 предназначен для формирования сигнала сброса счетчиков. На инверсном выходе первого элемента ИЛИ-НЕ 30 появляется единичный сигнал Пуск АЦП, которьй поступает на выход 47 20 блока синхронизации.

Первый импульс с генератора 15 тактовых импульсов переводит первый триггер 16 в единичное состояние, разрешая прохождение тактовых импуль- 25 сов через первый элемент И 17 и первый элемент ИЛИ 19 на вход первого счетчика 29 с коэффициентом пересчета, равным одиннадцати. Таким образом осуществляется задержка на 30 один такт, необходимая для переключения коммутатора 3 коррелятора. Сигнал Запуск АПП на выходе 47 блока управления длитйя два такта. По заднему .фронту сигнала Пуск АЦП запус- 35 Кода с выхода сумматора 6 в. соответкается АЦП 4 коррелятора. В течение тактов 3-8 действзпот сигналы Чтение на выходе второго элемента ИЛИ 24 и Выбор микросхемы на выходе-третьего элемента ИЛИ 26, которые с выхода 43 и вьгхода 44 блока управления поступают на входы разрешения записи блока 8 памяти. Однако запись содержимого ячейки памяти в регистр 7 не будет осуществляться до тех пор, пока на выходе 49 блока синхрониз а- ции имеется сигнал низкого уровня, т.е. четвертый триггер 39 находится в нулевом состоянии.

В течение тактов 3-10 происходит аналого-цифровое преобразование АЦП 4, на вход которого коммутатор 3 подает сигнал усилителя 2 второго процесса (сигнал управления коммутатора на выходе 46 блока синхронизации равен нулю). Полученный на выходе АЦП 4 код з.аносится в ЦАП 5 по сигналу Строб ЦАП,который формируется на -одиннадцатом тактовом импульсе трег

40

ствии с адресом, установленным на выходе 48 блока управления. На вход сумматора 6 по-прежнему не поступает информация с регистра 7, поскольку сигнал Сброс регистра имеет нулевое значение.

После окончания записи в очередную ячейку бл&ка 8 памяти содержимое второго счетчика 34 увеличивается 45 на единицу, что соответствует установке адреса следующей ячейки блока 8 памяти. Такая последовательность работы повторяется до тех пор, пока второй счетчик 34 не заполнится полностью. Коэффициент пересчета этого счетчика равен числу ячеек блока 8 . памяти, что соответствует числу точек вычисляемой корреляционной функции.

При переполнении второго счетчика 34 происходит установка второго триггера 28 в нулевое состояние,в результате чего подготавливается цикл вычисления взаимокорреляционной функции

5d

55

тьим элементом И 20 и четвертым элементом Р1 21. Сигнал с выхода первого элемента И 23 после одиннадцатого тактового имтулЬса устанавливает второй триггер 28 в единичное состояние что обеспечивает прохождение тактовых импульсов на вход первого счетчика 29 без задержки через второй элемент И 18 и первый элемент ИЛИ 19, а также появление единичного сигнала переключения коммутатора 3, Таким образом, на вход АЦП 4 подключается усилитель 1, управляемый с выхода ДАЛ 5 сигналом, пропорциональным ординате второго процесса, задержанным на требуемое время A S .

Следующий тактовый импульс сбрасывает выходы первого счет.чика 29, что приводит к появлению импульса Пуск АЦП на инверсном выходе первого элемента ИЛИ-НЕ 30 и установке третьего триггера 32 в нулевое состояние, разрешающее прохождение импульсов через седьмой элемент И 33 на вход второго счетчика 34.

Последующая серия тактовых им- пульсов обеспечивает ансшого-цифровое преобразование сигнала усилителя 2 в описанном порядке, но вместо сигнала Строб ЦАП блок управления формирует на выходе пятого элемента И 22 сигнал Запись, которьй разрешает запись в ячейку памяти В блока

0

ствии с адресом, установленным на выходе 48 блока управления. На вход сумматора 6 по-прежнему не поступает информация с регистра 7, поскольку сигнал Сброс регистра имеет нулевое значение.

После окончания записи в очередную ячейку бл&ка 8 памяти содержимое второго счетчика 34 увеличивается 5 на единицу, что соответствует установке адреса следующей ячейки блока 8 памяти. Такая последовательность работы повторяется до тех пор, пока второй счетчик 34 не заполнится полностью. Коэффициент пересчета этого счетчика равен числу ячеек блока 8 . памяти, что соответствует числу точек вычисляемой корреляционной функции.

При переполнении второго счетчика 34 происходит установка второго триггера 28 в нулевое состояние,в результате чего подготавливается цикл вычисления взаимокорреляционной функции

d

5

следующей реализации случайных процессов, поступающих на входы 10 и 11 коррелятора. Одновременно содержимое третьего счетчика 35 увеличи- вается на единицу, а сигнал на выходе второго элемента НЕ 37 устанавливает четвертьй триггер 39 в единичное состояние, что приводит к снятию сигнала низкого уровня Сброс регистра с управляющег о входа регистра 7. Следовательно, в каждой ячейке памяти накапливается сумма значений соответствующих точек корреляционной функции, поскольку на вход сумматора 6 поступает записанньш в регист р 7 по °сигналу Строб регистра, формируемому на выходе шестого элемента И 25 код содержимого соответствующей ячейки памяти на (i-l)-M цикле измерения а на другой вход - текущий код с выхода А1Щ 4,

Третий счетчик 35 служит для подсчета количества К усредняемых измерений корреляционной функции и име- ет соответствующий коэффициент пересчета. При заполнении этого счетчика на выходе восьмого элемента И 36 появляется сигнал, разрешающий прохождение через девятый элемент И 38 сиг- нала Строб выхода, который используется для стробировайия выхода результатов раОоты устройства на выходах 1 2 и 1 3.

ормула изобретения

Q 5 0

5 О

5

JQ гп

5

повышения быстродействия и упрощения, устройство содержит цифроанало- говый преобразователь, усилитель и управляемьй усилитель, причем информационный вход управляемого усилителя и вход усилителя являются соответственно первым и вторым информационными входами устройства, выходы уп- равляемого усилителя и усилителя соединены соответственно с первым и вторым инфермационными входами коммутатора, выход и управляющий вход которого соединены соответственно с ин- (|юрмационным входом аналого-цифрового преобразователя и седьмым выходом блока управления, восьмой, девятый и десятый выходы которого соединены соответственно с тактовым входом аналого-цифрового преобразователя, тактовым входом цифроаналогового преобразователя и входом сброса регистра, выход аналого-цифрового преобразователя соединен с информационным входом цифроаналогового преобразователя, выход которого соединен с входом задания коэффициента усиления управляемого усилителя, вЬгход блока памяти соединен с информационным входом регистра, шестой и одиннадцатьм выходы блока управления являются соответственно выходом номера ординаты и выходом окончания вьгчисления ординаты устройства.

2„ Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, генератор одиночного импульса, восемь элементов И,три элемента ИЛИ, четыре триггера, два счетчика, два элемента НЕ, элемент ;ИЛИ-НЕ, причем выход генератора тактовых импульсов соединен с тактовым входом первого триггера, первыми йходами первого и второго элементов И и является восьмым выходом блока, прямой выход первого триггера соединен с вторым входом первого элемента И, третий вход которого соединен с информационным входом перво- го триггера, первым входом третьего элемента. И и инверсным выходом второго триггера, прямой выход которого соедине н с вторым входом второго элемента И, первым входом четвертого элемента И и является седьмым выходом блока, ВЬГХОД первого элемента И соединен с первым входом первого

9

элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и счетным входом первого счетчика, первый разрядный выход которого соединен с первыми входами элемента lillH-dE и .

пятого и шестого элементов И, второй разрядньй выход первого счетчика соединен с вторыми входами шестого элемента И и элемента ИЛИ-НЕ и первыми входами второго элемента ИЛИ и седьмого элемента И, второй вход второго элемента ИЛИ соединен с третьими входами шестого элемента И и элемента И.ПИ-НЕ и третьим разрядным выходом первого счетчика, четвертый разрядный выход которого соединен с вторым входом пятого элемента И, тактовым входом третьего триггера, с вторым входом седьмого элемента И, первым входом восьмого элемента И и четвертым входом элемента ИЛИ-НЕ, выход которого является вторым выходом блока, выход пятого элемента И соединен с вторыми входами третьего и четвертого элементов И, выходы которых являются соответственно девятым и четвертым выходами блока, инверсный выход седьмого элемента И соединен с входом установки в I второго триггера, тактовый вход которого соединен с выходом переполнения второго Счетчика и счетным входом третьего счетчика, выход генератора одиночного импульса соединен с входами установки в О первого и второго и четвертого триггеров, входом -установки

0108610

в 1 третьего триггера и через пер- элемент И с входами установки в О nepBoi o, второго и третьего счетчиков, выход второго элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и является третьим выходом блока, выход четвертого элемента И соединен с вторым входом

10 третьего элемента ИЛИ и является четвертым выходом блока, выходы третьего элемента КПИ и шестого элемента И являются соответственно пятым и первым выходами блока, информацион15 Hbie входы второго, третьего и четвертого триггеров соединены с шиной нулевого потенциала, инверсный выход третьего триггера соединен с вторым входом восьмого элемента И, выход ко20 торого соединен с первым входом девятого элемента И и счетным входом второго счетчика, выход которого является шестым выходом блока, первый разрядный выход третьего счетчика

25 соединен через второй элемент НЕ с входом установки в VI четвертого триггера, выход которого является - десятым выходом блока, разрядные выходы группы третьего счетчика сое30 динены с соответствующими входами десятого элемента И, выход которого соединен с вторым входом девятого элемента И, выход которого является одиннадцатым выходом блока, выход пе25 реполнения третьего счетчика соединен с тактовым входом четвертого триггера, прямой выход которого является десятым выходом блока.

фаг. 2

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-15—Подача