1129

Изобретение относится к радиотехнике и может использоваться в устройствах синтеза частот и управления частотой перестраиваемого генератора,

Цель изобретения - повышение быстродействия,

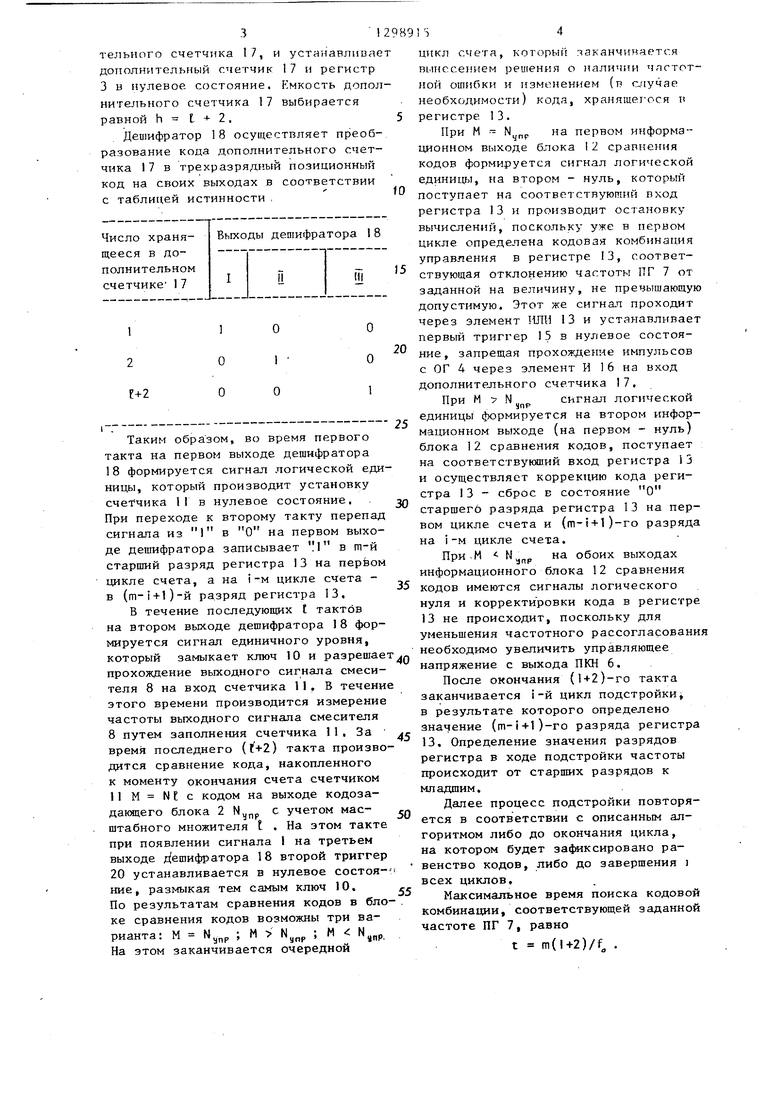

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит делитель 1 частоты с переменным коэффициентом деления (ДПКД), кодозадающий блок 2, частотный детектор (ЧД) 3, опорный генератор (ОГ) 4, итерационный вычислительный блок ИВБ 5, преобразователь 6 код - напряжение (ПКН), перестраиваемый генератор 7 (ПГ), .смеситель 8, умножитель 9 частоты, ключ 10, -счетчик 11, блок 12 срав

нения кодов, регистр 13 последова

тельных приближений, формирователь импульсов, первый триггер 5, элеме И 16, дополнительный счетчик 17, дешифратор 18, элемент ИЛИ 19, второй триггер 20.

Устройство работает следующим образом.

, Величина управляющего напряжения на выходе ПКН 6 может принимать п фиксированных значений.

Число п обычно выбирается исходя из требуемой точности подстройки &f ПГ 7

п i nt(f

f )/Af + 1,

лин

де fи f

Исхксмин

АЙН--35

- соответственно максимальная и минимальная частоты int ,..- операция взятия

; 40

целой части чис ла, заключенного в скобки.

Е соответствии с выбранным значением п число двоичных разрядов ИВБ 5 выбирается равным

П1 1.

В статическом , режиме частота сигнала на выходе ПГ 7 равна

+ fp+f ,

вых °

где fg - частота ОГ А;

N - коэффициент деления ДПКД 1, который устанавливается кодозадающим блоком 2;

Р - коэффициент умножения умножителя 9;.

5

0

5

5

52

f - величина абсолютной г)ог решOuj

ности частоты, не превышаю-. щая требуемой точности подстройки Af .

На ЧД 3 поступают сигналы, частоты KOToj-ibix отличаются на величину . Это значение погрешности не превышает величину частотной зоны нечувствительности ЧД 3, которая выбирается равной .с

В этом случае на выходе ЧД имеется постоянный уровень напряжения, в регистре 13 сохраняется код, соответствующий требуемой рабочей частоте, триггеры 15 и 20 находятся в состояниях, при которых сигналы с выходов ОГ 4 и смесителя 8 не проходят соответственно через элемент И 16 и ключ 10 на входы дополнительного счетчика 17 и счетчика 11.

При смене кода частоты в кодоза- дающем блоке 2 происходит изменение коэффициента деления ДПКД 1 и частотная ошибка между сравниваемыми в ЧД 3 сигналами превысит величину зоны его нечувствительности. В результате на выходе ЧД 3 скачком изменится уровень постоянного напряжения, на стартовом входе ИВБ 5, следствием является появление импульса на выходе формирователя 14 - начинается процесс подстройки. Настройка ПГ 7 осуществляется за m циклов, каждый из которых состоит из f тактов измерения двух дополнительных тактов.

Максимальное число циклов m опре/

деляется количеством разрядов регистра 13

m int fog n

+ 1

После появления импульса на выходе формирователя 14 начинается первый цикл подстройки. Число тактов измерения в каждом цикле зависит от требуемой точности подстройки uf и частоты f , поступающей на тактовый вход итерационного вычислительного блока 5

1 + 1

Импульс с выхода преобразователя 14 устанавливает первый триггер 15 в единичное состояние, разрешая тем самым прохождение импульсов ОГ 4 че рез элемент И 16 на вход дополнительного счетчика 17, и устанавливает дополнительный счетчик 17 и регистр 3 в нулевое состояние. Емкость дополнительного счетчика 17 выбирается равной h t + 2,

Дешифратор 18 осуществляет преобразование кода дополнительного счетчика 17 в трехразрядный позиционный код на своих выходах в соответствии с таблицей истинности ,

1 2 1+2

О О 1

о о

Таким образом, во время первого такта на первом выходе дешифратора 18 формируется сигнал логической единицы, который производит установку счетчика 11 в нулевое состояние, При переходе к второму такту перепад сигнала из 1 в О на первом выходе дешифратора записывает в гп-й старший разряд регистра 13 на перйом цикле счета, а на i-м цикле счета - в (т-1+1)-й разряд регистра 13,

В течение последующих t тактов на втором выходе дешифратора 18 формируется сигнал единичного уровня, который замыкает ключ 10 и разрешает прохождение выходного сигнала смесителя В на вход счетчика II, В течение этого времени производится измерение частоты выходного сигнала смесителя В путем заполнения счетчика 11, За время последнего {t+2) такта производится сравнение кода, накопленного к моменту окончания счета счетчиком 11 М N t с кодом на выходе кодоза- дакяцего блока 2 Н с учетом мае- штабного множителя t , На этом такте при появлении сигнала 1 на третьем выходе Дешифратора 18 второй триггер 20 устанавливается в нулевое состояние, размыкая тем самым ключ 10, По результатам сравнения кодов в бло- ке сравнения кодов возмоткны три на- рианта: М N,,, ; М N ; М . На этом заканчивается очередной

т 5

10

)5

20

25

JQ

е„ .

цикл счета, которьн гчаканчинается вынесением решения о наличии члстот- ной ошибки и изменением (в случае необходимости) кода, храняшет ося и регистре 13.

При М - на первом информационном выходе блока I2 сравнения кодов формируется сигнал логической единиф, на втором - нуль, который поступает на соответствующий вход регистра 13 и производит остановку вычислений, поскольку уже в первом цикле определена кодовая комбинация управления в регистре 13, соответствующая отклонению частоты ПГ 7 от заданной на величину, не пречышающую допустимую. Этот же сигнал проходит через элемент 11ПИ 13 и устанавливает первый триггер 15 в нулевое состояние, запрещая прохождение импульсов с ОГ 4 через элемент И 16 на вход дополнительного счетчика 17.

При М 7 N ,р сигнал логической единицы формируется на втором информационном (на первом - нуль) блока 12 сравнения кодов, поступает на соответствукший вход регистра 13 и осуществляет коррекцию кода регистра 3 - сброс в состояние О старшегб разряда регистра 13 на первом цикле счета и (m-i+l)-ro разряда на i-м цикле счета,

При-М N, на обоих выходах информационного блока 12 сравнения кодов имеются сигналы логического нуля и корректировки кода в регистре 13 не происходит, поскольку для уменьшения частотного рассогласования необходимо увеличить управляющее напряжение с выхода ПКН 6,

После окончания ()-го такта заканчивается i-и цикл подстройкиj в результате которого определено значение (m-i+l)-ro разряда регистра 13, Определение значения разрядов регистра в ходе подстройки частоты происходит от старших разрядов к младшим.

Далее процесс подстройки повторяется в соответствии с описанным алгоритмом либо до окончания цикла, на котором будет зафиксировано равенство кодов, либо до завершения i всех циклов.

Максимальное время поиска кодовой комбинации, соответствующей заданной частоте ПГ 7, равно

t ni(H-2)/f .

512

.Формула изобретения

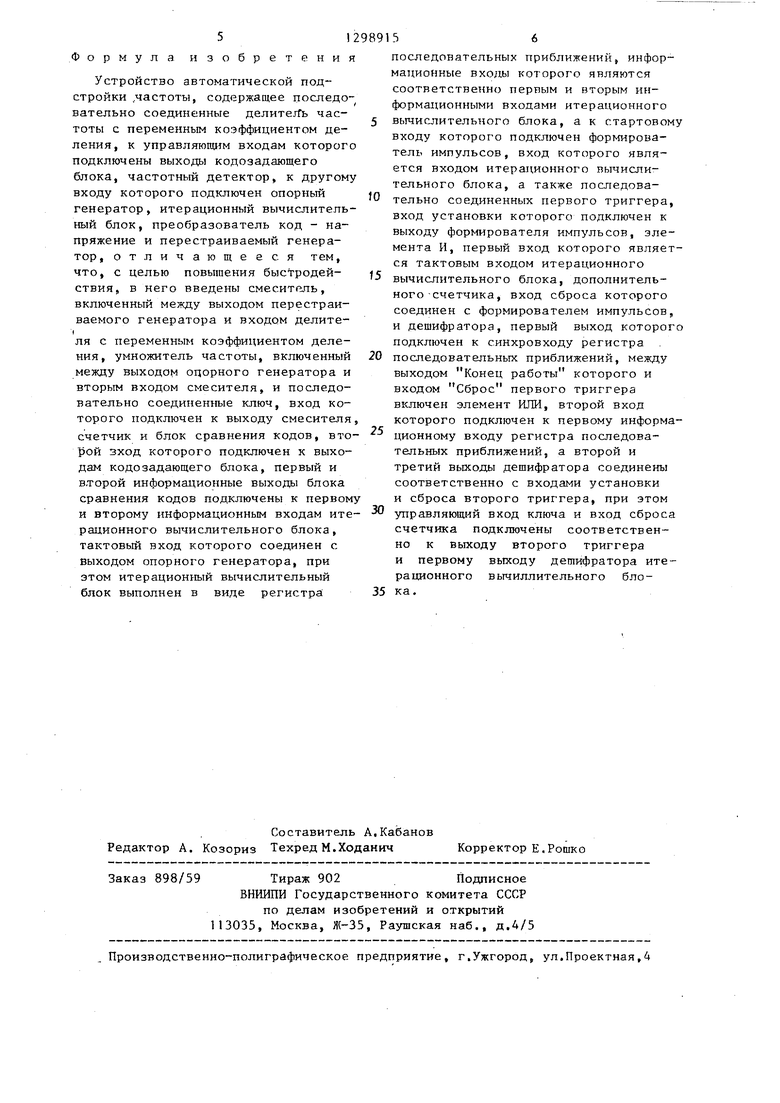

Устройство автоматической подстройки „частоты, содержащее последовательно соединенные делитехГь частоты с переменным коэффидиентом деления, к управляющим входам которого подключены выходы кодозадающего блока, частотный детектор, к другому

входу которого подключен опорный

генератор, итерационный вычислительный блок, преобразователь код - напряжение и перестраиваемый генератор, отличающееся тем, что, с целью повышения быстродей- ствия, в него введены смеситель, включенный между выходом перестраиваемого генератора и входом делите- (

ля с переменным коэффициентом деления, умножитель частоты, включенный между выходом опорного генератора и вторым входом смесителя, и последовательно соединенные ключ, вход которого подключен к выходу смесителя, счетчик и блок сравнения кодов, второй вход которого подключен к выходам кодозадающего блока, первый и второй информационные выходы блока сравнения кодов подключены к первому и второму информационным входам итерационного вычислительного блока, тактовый вход которого соединен с выходом опорного генератора, при этом итерационный вычислительный блок выполнен в виде регистра:

Составитель А.Кабанов Редактор А. Козориз Техред М.Ходаиич

898/59

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

5

0 5

5

0

36

последовательных приближений, информационные входы которого являются соответственно первым и вторым информационными входами итерационного вычислительного блока, а к стартовому входу которого подключен формирователь импульсов, вход которого является входом итерационного вычислительного блока, а также последовательно соединенных первого триггера, вход установки которого подключен к выходу формирователя импульсов, элемента И, первый вход которого является тактовым входом итерационного вычислительного блока, дополнительного -счетчика, вход сброса которого соединен с формирователем импульсов, и дешифратора, первый выход которого подключен к синхровходу регистра последовательных приближений, между выходом Конец работы которого и входом Сброс первого триггера включен элемент ИЛИ, второй вход которого подключен к первому информационному входу регистра последовательных приближений, а второй и третий выходы дешифратора соединены соответственно с входами установки и сброса второго триггера, при этом управляющий вход ключа и вход сброса счетчика подключены соответственно к выходу второго триггера и первому выходу дешифратора итерационного вычиллительного блока.

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Устройство для автоматической подстройки частоты | 1982 |

|

SU1054907A2 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Генератор ступенчатого напряжения | 1986 |

|

SU1330734A1 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение & стродействия. Устройство содержит делитель 1 частоты с переменным козф, деления, кодозадаюпий блок 2, частотный детектор 3, опорный генератор (г) 4, интерационный вычислительный блок 5, преобразователь 6 код - найря- жение, перестраиваемый Г 7, смеситель 8, умножитель 9 частоты, к.пюч 10, счетчик 11, блок 2 сравнения кодов, регистр I3 последовательных приближений, формирователь 14 импульсов, триггеры 15 и 20, элемент И 16, дополнительный счетчик 17, дешифратор 18, элемент ИЛИ 19. 1 ил., 1 табл. 1ЧЭ со 00 со

| Устройство для автоматической подстройки частоты | 1976 |

|

SU657575A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-04-15—Подача