(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| Логическое запоминающее устройство | 1975 |

|

SU529486A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1974 |

|

SU492934A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения дискретной информации.

По основному авт.св. № 490183 известно логическое запоминающее устройство (ЛЗУ), содержащее регистр признаков обращения, числовые линейки, разрядные шины записи, считывания и чтения, линейные шины записи и считывания которых подключены соответственно через разрядные элементы ИЛИ и разрядные элементы И к выходам регистра слова, через усилители чтения - к входам регистра регенерации и через адресные формирователи записи и считывания - к выходам адресных элементов И, управляющие входы которых соединены через управляющие элементы ИЛИ с шинами управления, подключенными к управляющим входам разрядных элементов И, и вспомогательных разрядных элементов И, функциональные входы которых соединены с выходами регистра регенерации выходы подключены к разрядным элементам ИЛИ, шину опроса, линейные элементы Запрет по числу разрядов устройства, выходной элемент ИЛИ, входы которого подключены к выходам

усилителей чтения, а выход - к функциональному входу элемента И, управляющий вход которого соединен с шиной опроса, функциональные входы i-x (...n) линейного и разрядного элементов Запрет и (п+1)-го, (п+ +2)-го линейных элементов Запрет подключены соответственно к выходам i-x и ()-го, (п + 2)-го разрядов

0 регистра признаков оСраг1ения, управляющие входы i-X разрядных и линейных элементов Запрет и (n-fl)-ro, (п+2)-го линейных элементов Запрет соединены с соответствующими разряд5ной и линейной шинами управления, выход каждого линейного элемента Зап рет подключен к выходам двух адресных элементов И соответствующей числовой линейки, выход каждого разряд0ного элемента Запрет соединен со входом соответствующего разрядного элемента ИЛИ 1.

Недостатком этого ЛЗУ является его низкое быстродействие.

5

Цель изобретения - повышение быстродействия ЛЗУ.

Поставленная цель достигается тем, что предлагаемое устройство содержит дзухвходовые переключатели по числу

0 раарядов регистра регенерации, перые входы которых соединены с шиной правления, вторые входы и выходы подлючены соответственно к выходу соотетствующего разряда регистра регеерации и к дополнительному запреающему входу разрядных элементов Запрет.

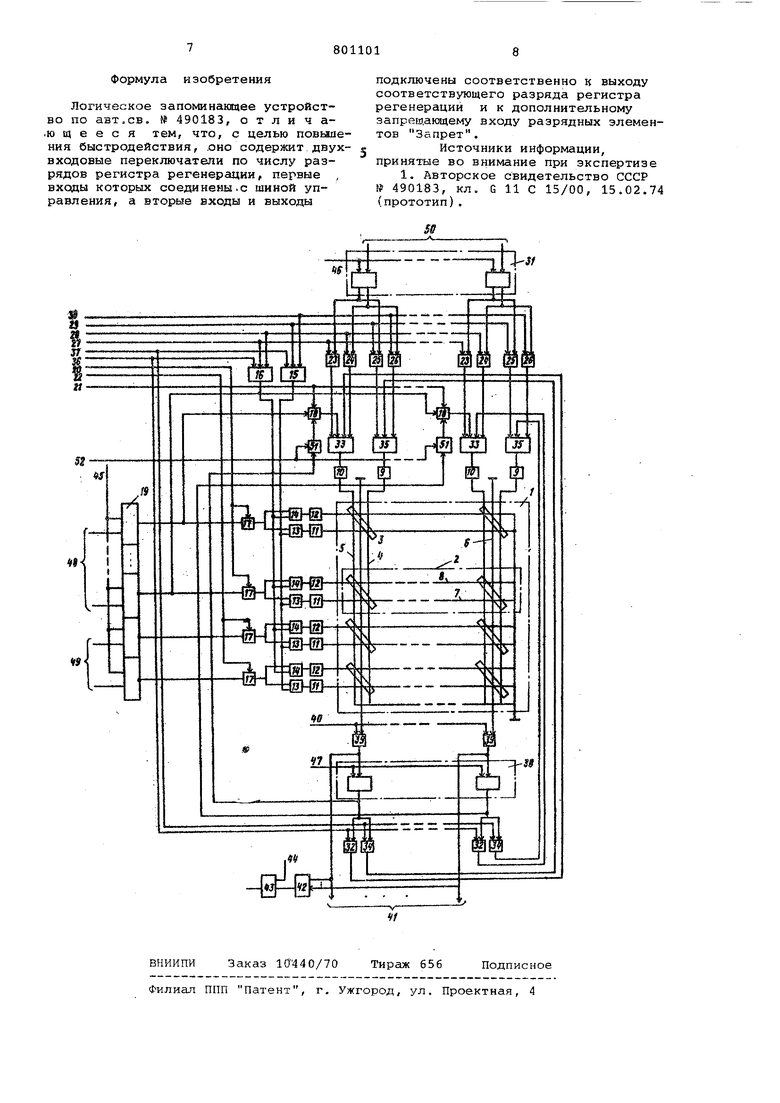

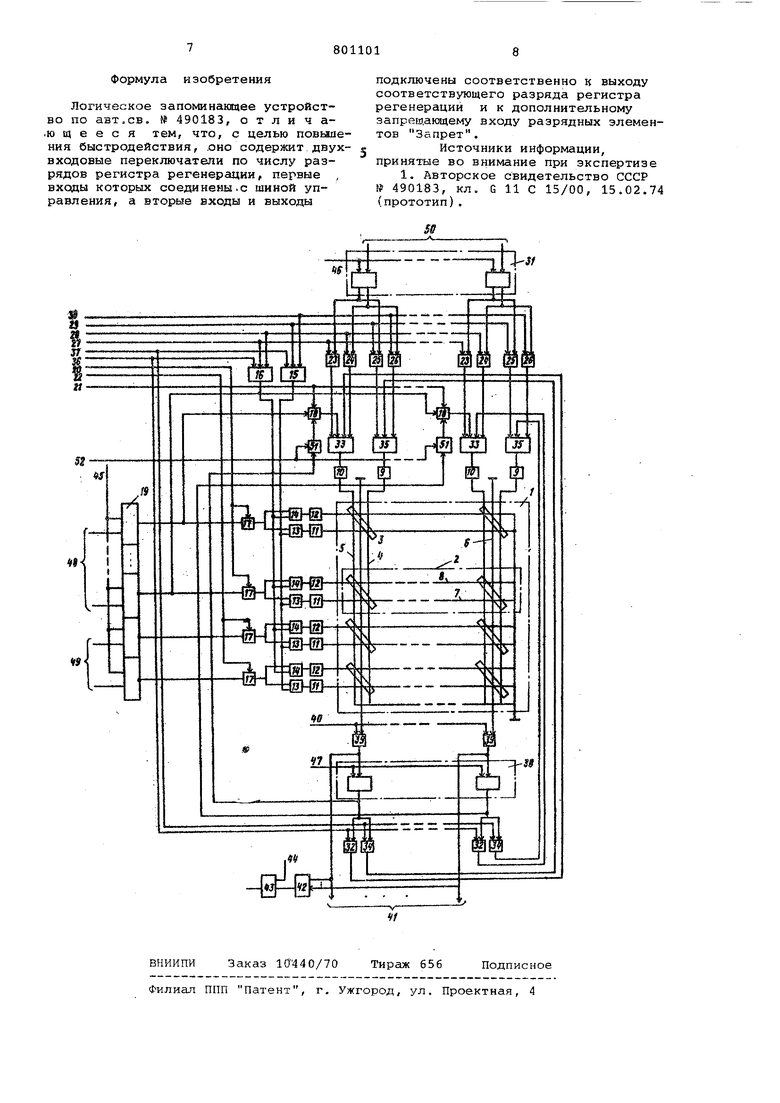

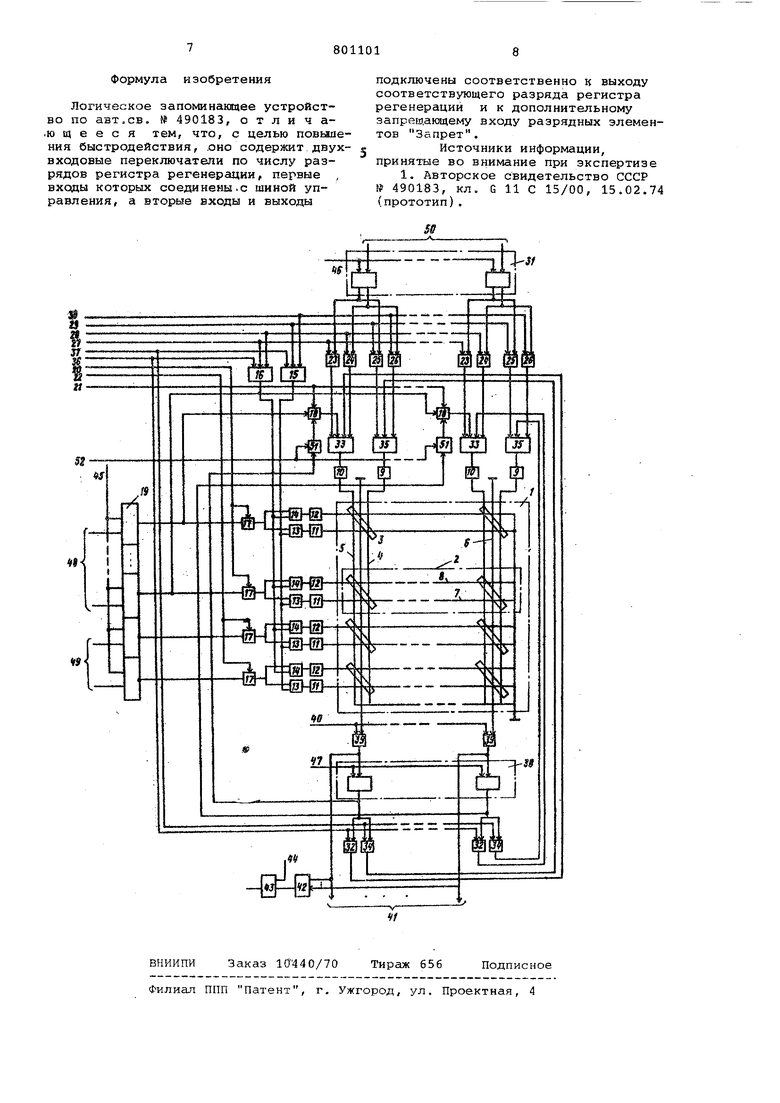

На чертеже изображена структ.урная схема ЛЗУ,

ЛЗУ содержит накопитель 1, состоящий из числовых линеек 2 на тороиальных сердечниках 3 с прямоугольной петлей гистерезиса, имеющих разядные шины записи 4, считывания 5 и чтения б и линейные шины записи 7 и считывания 8.

Каждая из разрядных шин записи 4 считывания 5 и каждая из линейных ин записи 7 и считывания 8 подключены к выходам соответствующих разрядных формирователей записи 9 и считывания 10 и адресных формирователей записи 11 и считывания 12. Вход каждого адресного формирователя записи и считывания связан с выходом адресного элемента И 13 или 14, -управляющие входы которых подключены соответственно к выходам управляющих элементов ИЛИ 15 и 16. Функциональные входы адресных элементов И 13 и 14 цепей записи и считывания каждой числовой линейки 2 соединены с выходом соответствующего линейного элемента Запрет 17. Функциональные входы i-x(,n) линейного и разрядного элементов Запрет 17 и 18 подключены к выходу i-ro разряда регистра 19 признаков обращения, а их управляющие входы соединены соответственно с линейной 20 и разрядной 21 шинами управления.

Функциональные входы (п +1)-го и (п+2)-го линейных элементов Запрет 17 подключены соответственно к выходам (п+1)-го и (п+2)-го разрядов регистра 19 признаков обращения, а их управляющие входы соединены с Линейной шиной 22 управления.

У111 авляющие входы разрядных элементов И 23-26 подсоединены к управляющим шинам 27-30. Функциональные входы i-x разрядных элементов И 23, 25 и 24, 26 связаны соответственно с инверсными и прякелм выходами i-ro разряда регистра 31 слова. Выходы i-x разрядных элементов И 23 и 24, разрядных элементов Запрет 18 и вспомогательных разрядных элементов И 32 подключены к входам разрядных элементов ИЛИ 33, а выходы i-x разрядных элементов И 25 и 26 и элементов И 34 соединены со входами элементов ИЛИ 35 i-й разрядной цепи. Выходы i-x элементов.ИЛИ 33 и 35 Лодключены соответственно к входам разрядных формирователей считывания 10 и записи 9.

Управляющие входы элементов И 32 соединены с шиной 36 управления.

а элементов И 34 - с шиной 37 управления. Функциональные входы i-x элементов И 32 и 34 подключены к выходу i-ro разряда регистра 38 регенерации, а вход этого регистра - к выходу i-rc усилителя 39 чтения, подсоеди ненного к шине 6 чтения i-и разрядной цепи. Управляющие входы усилителей чтения соединены с шиной 40 .стробирования, а их выходы - с выходными шинами 41 логического запоминающего устройства и с входами выходного элемента ИЛИ 42, выход которого подключен к функдионсшьному входу элемента И 43. Управляющий вход элемента И 43 соеди.нен с шиной 44 сброса, входы управляющих элементов ИЛИ 15 и 16соответственно с шинами 29,30,37 и 27, 28, 36 управления.

Регистры 19 и 31 имеют шины 45 и 46 сдвига, регистр 38 регенерациишину 47 сброса, i-e, (п+1)-й и (п+ +2)-и разряды регистра 19 - входные шины 48 и 49, регистр 31 слова входные шины 50. Первые входы двухвходовых переключателей 51 соединены с шиной управления 52, а второй вход и выход каждого i-ro (i-1,n) переключателя подключены соответственно к выходам i-ro разряда регистра 38 регенерации и к дополнительному запрещающему входу разрядных элементов Запрет 18.

Обозначим значение i-ro разряда двоичного кода, хранящегося в числовой линейке У; , значение сигнала в

1-й разрядкой цепи - Х|.Результат логической операции f(X(; Y,-), который остается в числовой линейке, PJ , результат логической операции CI5(x.y-)f который образуется на

i-ой разрядной шине 6 чтения, 0,. Логические операции, выполняемые

в логическом запоминающем устройстве

приведены в таблице.

Работает устройство следующим образом.

До начала работы в каждую i-ю числовую линейку накопителя 1 записывается двоичный код приоритета AJ 2 -1, а в (п +1)-ой, (п+2) числовых линейках хранится код приоритета А, а на регистре регенерации записан код приоритета Aj i-ro значащего разряда двоичного числа -В- .

В первом такте по входным шинам 48 в регистр признаков обращения поступает код двоичного числа ,

Во втором такте на шины управления 20, 22, 28, 52, стробирования 40 и опроса 44 подаются единичные сигналы.

При этом i-e, (п+1)-й, (п+2)-й ли.нейные элементы Запрет закрыты. Часть из. разрядных элементов Запрет 18, каждый элемент которой соответствует единичным разрядам кода приоритета А(, хранящегося на регистре 38

регенерации, закрыты. Оставшаяся часть элементов Запрет 18 находится в проводящем состоянии.

Е. иничные сигнсшы с выходов i-x(isk,,...m) разрядов .регистра признаков обращения через соответств ющие, не закрытые сигналами с переключателей 51, разрядные элементы Запрет 18 и связанные с ними элементы ИЛИ 33 возбуждают i-e разрядные формирователи 10 считывания. На шинах 6 чтения появляется двоичный код, соответствующий результату операции В„ ЛА| , который подается на входы усилителей 39 чтения. Выходные сигналы усилителей чтения поступают на входы элемента ИЛИ 42, сигна с его выхода - на функциональный вход выходного элемента И 43, на выходе которого формируется значение величины У.

Управляющие работой логического запоминающего устройства в третьем такте организуется в зависимости от значения величины У.

Если , то в третьем такте производится сброс в О содержимого регистра 19 и логическое запоминающее устройство переходит в исходное состояние.

Если же величина У, сформированна во втором такте, равна единице, то в третьем такте формируется признак AJJ к-го разряда числа Вц , для чего на линейные шины 22, 27 управления и на шину 40 стробирования подаются единичные сигналы, а на осталные шины управления - нулевые сигналы. В результате единичные сигналы Прим е ч а и и е.

с выходов (,f,...т) разрядов регистра признаков обращения через i-e ) линейныеэлементы Запрет 17 и адресные элементы И 14 поступают на входы соответствукнцих i-x(,J,...m) адресных форг-шрователей 12 считьшания,. а единичные сигналы с инверсных выходов разрядов регистра слова через открытые элементы И 23 и элементы ИЛИ 33 проходят на входы разрядных формироватеoлей 10 считывания.

В (,,...т) числовых линейках выполняются операции Р- ОлУ( и Q; Y; до , а на разрядшлх шинах 6

г%

чтения образуется код числа ,$;L

f

5

-.и nvif

который заносится с выходов усили телей чтения в регистр 38 регенерации и поступает на выходные шины 41.

В четвертом такте в первый разряд регистра слова и во все разряды регистра признаков обращения заносятся

0 еди ницы.

)вдом последукхцем (+4)-й (,n) такте на шины 45 и 46 сдвига регистров 19 и 31 и на шину 30 уп5равления подаются единичные сигналы. В результате в каждом )-м такте в i-e разряды с i-й по (п+2)-ю числовых линеек записываются единицы, в (п+4) такте в каждой 1-й (,n)

0 числовой линейке формируется код А. 2-1, а в (п+1)-й и (п+2)-й числовых линейках 2 - код числа (2 -1).

В (п+5) такте производится сброс в О кода регистров 19, 31 и логи5ческое запоминающее устройство переходит в исходное состояние. Символами Л, обозначены соответственно операции запрета, импликации, стрелка Пирса, дизъюнкция и коньюнкция.

Авторы

Даты

1981-01-30—Публикация

1979-03-22—Подача