1

Предложенное устройство относится к области вычислительной техники и может быть использовано для хранения и переработки дискретной информации.

Известно логическое полноточное запоминающее устройство, содержащее накопитель с числовыми линейками, с элементами па.мяти на двух сердечниках с прямоугольной петлей гистерезиса, регистры признаков обращения и слова, разрядные вентили; разрядные элементы «ИЛИ, усилители чтения, генераторы тока запрета, тока прямоугольной формы и тока пилообразной формы, управляющие и выходные вентили, разрядные элементы задержки и вентили единичного и нулевого входов.

Недостатком известного устройства является сложность схемы и большое количество оборудования, что снижает информационную надежность. Кроме того, известное устройство не позволяет реализовать полный набор логических операций, что сужает его функциональные возможности и область применения.

Целью изобретения является повышение надежности работы устройства и расширение области его примене)1ия.

Поставленная цель достигается тем, что устройство содержит схемы «ИЛИ, входы которых подключены к соответствующим выходам регистра адреса, а выходы - через выходные вентили к выходам соответствующих усилителей считывалия.

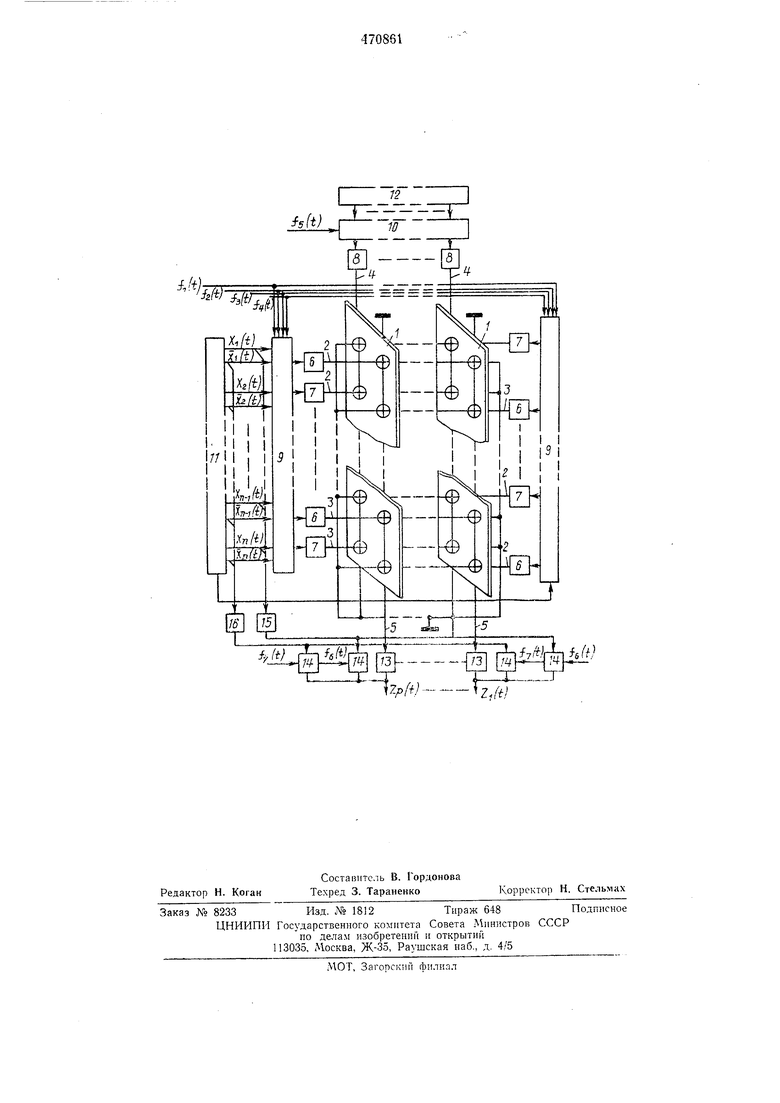

Иа чертеже изображена схема устройства. Предложенное устройство содержит накопитель, выпоЛПенный на интегральных числовых ферритовых линейках I, с шинами опроса 2, записи 3, запрета 4 и считывания 5, формирователи опроса 6, записи 7 и запрета 8, адресные 9 и разрядные 10 вентили, регистры адреса 11 и числа 12, усилители считывания 13, выходные вентили 14, схемы «ИЛИ 15 и 16, шииы прямой адресной переменной Х| (t) . .. Хд (J) и шины инверсной адресной переменной, xi(t)i...Xn (t), соответствующие

1-му и п-му адресам, fi f2f3f4f5 управляюшие сигналы, а Zi (t),...Zp (t) - выходные переменные соответствующие 1-му п Р-му разрядам.

В исходном СОСТОЯНИИ в регистре адреса 11 хранится неременная , хз. .. Хп-1 , х„ а переменная у у,, ys-yn-i , Уп 1 хранится в элементах памяти интегральных числовых феррптовых линеек 1 накопителя. Так как регистр адреса выполнен на триггерах, имеющих прямой и инверсный выход, то переменная представлена в виде xixi; Х2-Х2 . . . х„ 1 Хп-I ; Хп х„ .

В предлагаемом устройстве используется

припцпп суперпозиции выходной переменной

Z(t) с адресными переменными x(t) и x(t). При этом логические операции над переменными и являются поразрядными операциями, поэтому достаточно рассмотреть реализацию операции для одного разряда информации.

Обозначим через q(t+1) ) t переключательную функцию элемента памяти интегральной числовой фер-ритовой линейки. Для элемента памяти представленного устройства можно записать переключательную функцию в виде

w

(xfiVXf2)pfsV(xfiVxf2)pf5V{xf3Vxf4)

Ф(У) } ,

а выходную переменную можно представить выражением

()ф(у)у(хГзУХ 4)

tpCy vxfgVxfy

при ограничениях, накладываемых па управMbляющие сигналы flf3Vf2f4Vf3f5Vf4f5Vf|f7Vf2f6Vf4f6l О

где p(t) - разрядная двоичная переменная.

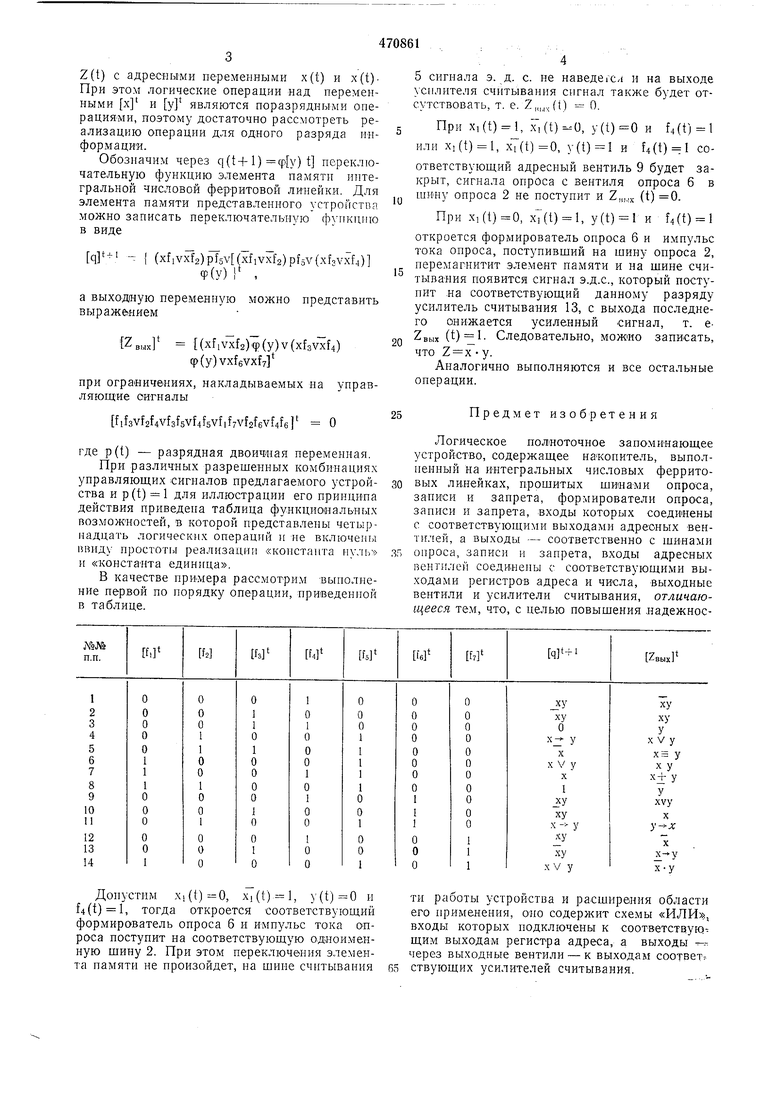

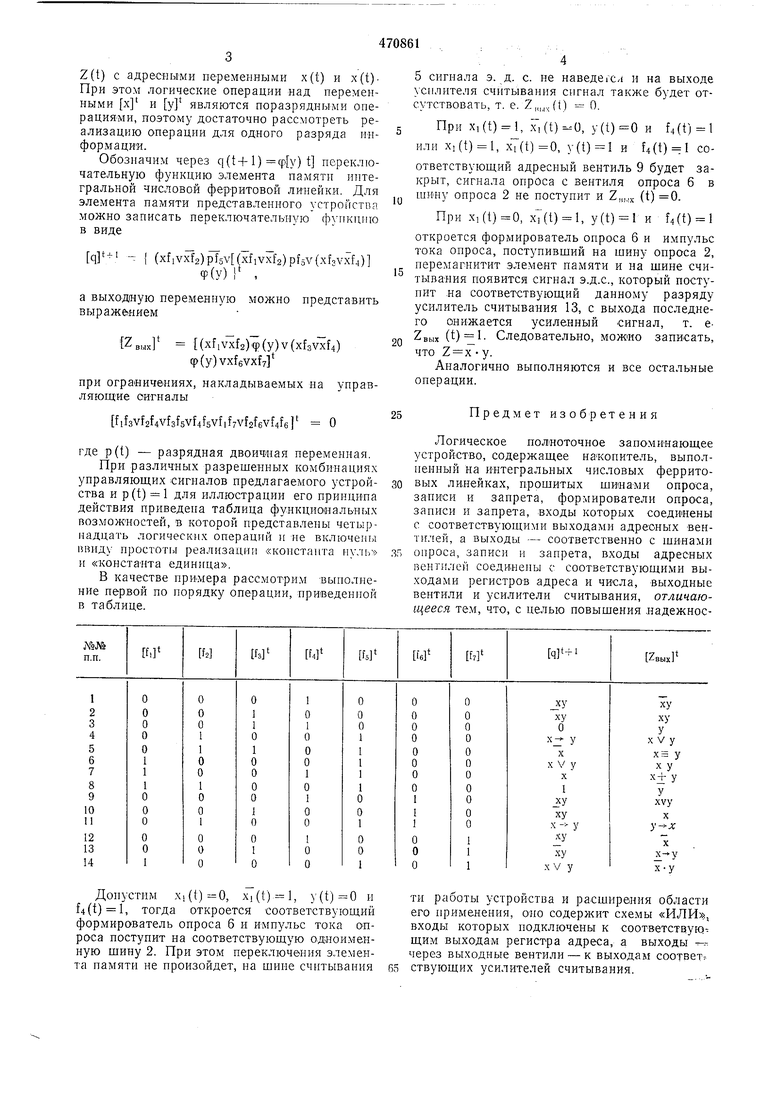

При различных разрешевпых комбинациях управляющих сигпалов предлагаемого устройства и p(t) 1 для иллюстрации его принципа действия приведепа таблица функциоиальных возможностей, в которой представлепы четырнадцать логически.к операций и пе включены ввиду простоты реализация «константа нуль н «константа един1 ца.

В качестве примера рассмотрим выполпение первой по порядку операции, нриведенпой в таблице.

5 сигнала э. д. с. не наведете л и на выходе уснлителя считывания сигнал также будет отсутствовать, т. е. Z ,„,,.( (t) 0.

При x,(t) l, .,(t)-0, y(t)0 и f4(t)l или xi(t) l, xT(t)0, y(t)I и f4(t)l соответствующий адресный вентиль 9 будет закрыт, сигнала опроса с вентиля опроса 6 в шину опроса 2 не поступит и Z,,,,,x (t)0.

При x,(t)0, x7(t) l, y(t) l и f4(t) l

откроется формирователь опроса 6 и импульс тока опроса, поступивший на шину опроса 2, перемагнитит элемент памяти и на шине считывания появится сигнал э.д.с., который поступит .на соответствующий данному разряду усилитель считывания 13, с выхода последнего анижается усиленный сигнал, т. е2вы с (t) l. Следовательно, можщо записать, что Z x -у.

Аналогично выполняются и все остальные операции.

Предмет изобретения

Логическое полиоточное запоминающее устройство, содержащее накопитель, выполненный на интегральных числовых ферритовых линейках, прошитых шинами опроса, запуск и запрета, формирователи опроса, записи и запрета, входы которых соединены с соответствующими выходами адресных венти.чей, а выходы - соответственно с шинами опроса, записи и запрета, входы адресных вентилей соединены с соответствующими выходами регистров адреса и числа, выходные вентили и усилители считывания, отличающееся тем, что, с целью повышения надежнос

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Логическое запоминающее устройство | 1975 |

|

SU529486A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

Допустим xi(t)0, xj(t) l, y(t)0 и f4(t) l, тогда откроется соответствующий формирователь опроса 6 и импульс тока опроса поступит на соответствующую одноименную шину 2. При этом переключения элемента памяти не произойдет, на шине считывания

ти работы устройства и расширения области его применения, оно содержит схемы «ИЛИ, входы которых подключены к соответствунэщим выходам регистра адреса, а выходы через выходные вентили - к выходам соответ ствующих усилителей считывания.

Авторы

Даты

1975-05-15—Публикация

1974-03-19—Подача