Изобретение относится к запоминаю щим устройствам. По основному авт. св. № 801101 из вестно, устройство, содержащее регист признаков обращения, числовые линейки, разрядные шины записи, считывания и чтения и линейные шины записи и считывания, которые подключены соответственно через разрядные элементы ИЛИ и разрядные элементы НК выходам регистра слова, через усили тели чтения - к входам регистра реге нерации и через адресные формировате ли записи и считьшания - к выходам адресных элементов И, управляющие . входы которых соединены через управляющие элементы ИЛИ с шинами управле ния, подключенными к управляющим входам разрядных элементов И и вспомогательных разрядных,элементов И, функциональные входы которых соединены с выходами регистра регистрации а выходы подключены к разрядным элементам РШИ, шину опроса, линейные элементы Запрет по числу линеек, разрядные элементы Запрет по числу разрядов устройства, выходной элемент ИЛИ, вход,ы которого подключены к выходам усилителей чтения, а выход к функциональному входу элемента И, управляющий вход которого соединен с шиной опроса, функциональные входы i-x(,n ) линейного и разрядного элементов Запрет и (п+1)-го и (п+2 У-ГО линейных элементов Запрет подключены соответственно к выходам и (п+1 )-го, (п+2 )-го разрядов - . регистра признаков обращения, управляющие входы i-x разрядных линейных элементов Запрет и (п+1)-го, (п+2)-го линейных элементов Запрет соединены с соответствующими разрядной и линейной шинами управления, выход каждого линейного элемента Запрет подключен к выходам двух адресных элементов И соответствующей числовой линейки, а выход каждого оазрядного элемента Запрет соединен с входом соответствующего разрядного элемента ИЛИ, двухвходовые . .переключатели по числу разрядов регистра регенерации, причем первые входы переключателей соединены с шиной управления, а вторые входы и выг ход каждого переключателя подключены соответственно к выходам .соответстг вующего разряда регистра регистрации и к дополнительному запрещающему входу разрядных элементов Запрет fO Недостатком этого устройства является низкое быстродействие устрой.ства при обработке приоритетов. Цель изобретения - повьппение быстродействия логического запоминающего устройства. Поставленная цель достигается тем что в устройство введены двухвходовые переключатели по числу разрядов регистра регенерации,. первые входы которых соединены с одной из шин . управления, вторые входы подключены соответственно к выходам регистра ре. генерации, а выходы соединены соответственно со входами регистра слова . При зтом сокращается время вьшолн ния логическим запоминающим устройстг вом операций по формированию кода приоритета для последовательности поступающих двоичных слов, каж,цьй из . значащих разрядов которых имеет определенный приоритет,за счет того,что исключается время,необходимое на восст.ановлейие содерлсимогО тех числовых линеек, которые не разрзппаются при фор мировании кода приоритета,в том слуJ4ae,когда в. поступающем двоичном. слов есть значащие разряды,соответствующи более высокому приоритету,чем приоритет любого из значащих разрядов предьщущегоАслова. Операции по обработке запросов описьшаются выражениями ysBite.triCf +l )4А,-(Г), flirt+n если , AI{i,-H)a|(j. если , где ,,,) +- +2 двоичное слово, поступившее н& вход ус тройкетва в момент Ct + l ), (U k, f,mrrijjt -... n - число разрядов в слове В.,, Ai() - приоритет i-ro знача разряда двоичного слова В|0,.; 2М +... поступившегб на вход устройства в момент t;(,p, 17р7....7г); 24 A:f - признак i-го разряда; И - сигнал, значение которого равно единице, если (t+l )A() и нулю, если A(t + l ) ,-(t). На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит накопитель 1, состоящий из числовых линеек 2 на тороидальных сердечниках 3 с прямоугольной петлей гистерезиса, имеющих разрядные шины 4, считывания 5 и чтения 6 в линейные шины записи 7 и считьшания 8. Каяодая из разрядных шин записи 4 и считьшания 5 и каждая из линейных шин записи 7 и считывания 8 подключены к выходам соответств пощих разрядных формирователей записи 9 и считьшания 10 и адресных формирователей записи 11 и считывания 12. Вход каждого адресного формирователя записи и считывания связан с выходом адресного элемента И 13 или 14, управляющие входы которых подключены соответственно к выходам управляющих элементов ИЛИ 15 и 16. Функциональные входы адресных элементов И I3 и 14 цепей записи и считывания каждой числовой линейки 2 соединены с выходом соответствующего линейного элемента Запрет 17. Функциональные входы i-x(,n) линейного и разрядного элементов Запрет 17 и 18 подключены к выходу i-ro разряда регистра 19 признаков обращения, а их управляющие входы соединены соответственно с линейной 20 и разрядной 21 шинами управления. Функциональные входы (п+ )-го к (п+2 )-го линейных элементов Запрет 17 подключены соответственно к выходам (п+1 )-го и (п+2)-го разрядов регистра 19 признаков обращения, а их управляющие входы соединены с линейной шиной 22 управления. Управляющие входы разрядных элементов И 23-26 подсоединены к управляющим шинам 27-30. Функциональные входы i-x разрядных элементов И 23, 25 и 24,26 связаны соответственно с инверсиями и прямыми выходами г-го разряда регистра 31 слова. Выходы Г-х разрядных элементов И 23 и 24, разрядных элементов Запрет 18 и вспомогательных разрядных элементов И 32 подключены к выходам разрядных элементов ИЛИ 33, а выходы i-x разрядных элементов И 25 и 26 и элементов И 34 соединены со в одами элемента mni 35- i-й разрядной цепи. Выходы i-x элементов liTBi 33 и 35 подключены соответственно к выходам разрядных формирователей считьгоания 10 и записи 9.

Управляющие входы элементов И 32 соединены с шиной 36 управления, а элементов И 34 - с шиной 37 управления. Функциональные входы i-x,элементов И 32 и 34 подключены к выходуi -и разрядной цепи.Управляющие, входы усилителей 39 чтения соединены с шиной 40 стробирования, а их выходы - с выходными шинами 41 логического запоминающего устройства, и с входами вькодного элемента И 43. Управляющий вход элемента И 43 соединен с шиной 44 опроса, входы управляющих элементов ИЛИ 5 и 16 - соответственно с шинами 29,30,37 и 27,36 управления.

Регистры 19 и 31 имеют шины 45 и 46 сдвига, регистр 38 регенерации шину 47 сброса, i-e, (п+1)-й и (п+2)-й разряды регистра 19-входные шины 48 и 49,регистр 31 слова-входные шины 50.Первые входы друхвходовых пеп:

реключателей 51 соединены с шиной 5 управления, а второй вход и выход каждого i-го (i t,п ) переключателя подключены соответственно к выходам f-ro разряда регистра 38 регенерации и к запрещающему входу разрядных элементов Запрет 18. Первые входы дополнительных двухвходовых переключателей 53 соединены с шиной 54 уп:р вления, а второй вход и выход каждого i-ro (i l,n} переключателя под- ключены соответственно к выходам i-ro разряда регистра 38 регенерации и к разрядным входам регистра 31 слова.

Обозначим значение i-ro разряда двоичного кода, хранящегося в числовой линейке, N( , значение сигнала в i-й разрядной цепи X4 , результат логической операции f (х , ), который остается в числовой линеже - Р( , результат логической операции Ч (х, у. который образуется на I-ой разрядной шине 6 чтения, -qi.

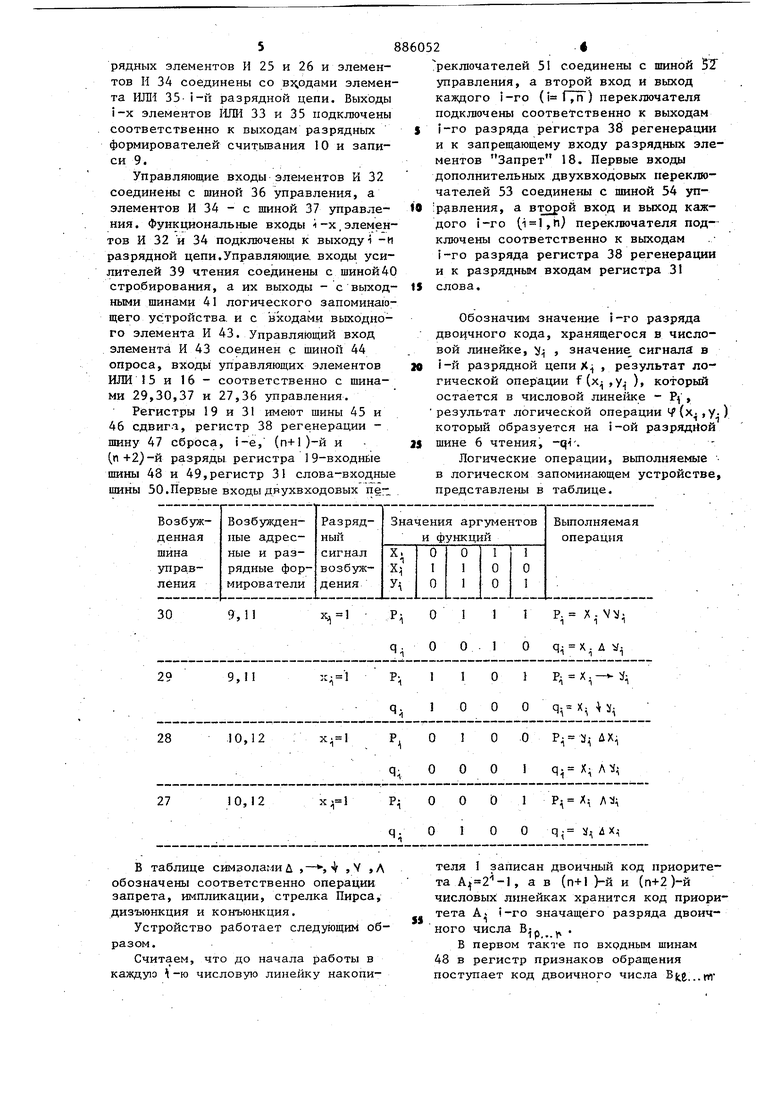

Логические операции, вьшолняемые в логическом запоминающем устройстве, представлены в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

| Логическое запоминающее устройство | 1975 |

|

SU529486A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1974 |

|

SU492934A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

30

9,11

в таблице символами д ,,- V ,Л обозначены соответственно операции запрета, импликации, стрелка Пирса, дизъюнкция и конъюнкция.

Устройство работает следующим образом.

Считаем, что до начала работы в каждую -ю числовую линейку накопи. О 1 11 Р. ; -VV:i

теля 1 записан двоичный код приоритета , а в (п+1 Ьй и (п+2)-й числовых линейках хранится код приоритета А. i-ro значащего разряда двоичного числа ,

В первом такте по входным шинам 48 в регистр признаков обращения поступает код двоичного числа .. ..пт Во втором такте на шину 20,22,28 и 52 управления, стробирования 40 и опроса 44 подаются единичные сигналы При этом i-e, (п+1 )-й и (п+2 Ьй линейные элементы Запрет закрыты. Часть из разрядных элементов Запрет 18, каждый элемент которой соответст вует единичным разрядам кода приоритета А, хранящегося на регистре 38 регенерации, закрыты. Оставшаяся часть элементов Запрет 18 находится в проводящем состоянии. Единичн)1е сигналы с выходов i-x(i К, В,...,П1) разрядов регистра признаков обращения через соответствующие, не закрытые сигналами с пес переключателей 51, разрядные элементы Запрет 18 и связанные с ними элементы ИЛИ 33 возбуждают 1-е разрядные формирователи 10 считьюания. На шинах 6 чтения появляется двоичный код, соответствующий резул тату операции BJL, HilA , который по дается на входы 39 чтения. Выходные сигналы усилителей чтения поступают на выходы элемента ИЛИ 42, сигнал с его выхода - на функциональный вход выходного элемента И 43, на выходе которого формируется значение -величины (. ..( Управление работой логического запоминающего устройства в третьем также организуется в зависимости от значения величины У . , то в третьем такте производится сброс в О содержимого регистра 19 и логическое запоминающее устройство переходит в исходное состояние. Если же величина , сформирована во втором такте, равна единице, то в третьем такте формируется признак А к-го разряда, числа В,,,, для чего на шины 22 и 27 управления и на шину 40 стробирования подаются единичные сигналы, а на остальные шины управления - нулевые сигналы. В результате единичные сигналы с выходов 1-х(и К, Е,.)раВрядов регистра признаков обращения через (i,n) линейные элементы Запрет 17 и адресные элементы И 14 поступают на входы соответствующих i-x( i Kj С,. адресных формирователей 12 считьгоания, а единичные сигналы с инверсных выходов.разрядов регистра слова через открытые элементы ИЛИ 33 проходят йа входы разрядных формировате-. лей 10 считывания. 28 В i-x( i К, Е,...,пт) числовых линейках вьшолняются операции Р{ и , а на разрядных шинах 6 чтения образуется код числа ,, который заносятся с выходов усилителей чтения в регистр регенерации и поступает на выходные шины 41. В четвертом такте на шину 54 управления подается единичный сигнал и код числа A.JJ записьшается в регистр 31 слова, В каждом последующем (+4)-м (,k,) такте на шины 44 и 46 сдвига регистров 19 и 31 и на шины 29 и 30 управления подаются единичные сигналы,а на шину 20 управления пода- . ется нулевой сигнал. В результате, в каждом (i+4 )-м такте в разряды с первого по (К+1-)-ьш числовых-линеек (К+1-i), (l+1-i),..., (m+1-i ) записываются единицы, а нули - в оставшиеся разряды соответствующих числовых линеек. После ктго сдвига регистры 19 и 31 остаются .заполненными нулями и устройство остается в исходном состоянии. Время выполнения известным устройством операций по формированию кода приоритета для последовательности поступающих двоичных слов, каждый из значащих разрядов которых имеет рпределенный приоритет, равно (n-t-5 ) тактов, В предлагаемом устройстве время вьшолнения операций по формированию кода приоритета (к+4) тактов, для запросов, имеющих равную вероятность появления, - . Поэтому время .выполнения операций по формированию кода приоритета сокращается в среднем. в (п+5 )(п/2-4) раз. Формула изобретения Логическое запоминающее устройство по авт. св. № 801101, отличающ е е с я тем, что, с целью повышения быстродействия устройства,оно содержит дополнительные двухвходовые перекочатели по числу разрядов регистра регенерации, первые входы которых j: о единены с одной из шин управления, вторые входы подключены соответственно к выходам регистра регенерации, а выходы соединены соответственно со входами регистра слова,, Источники информации, принятые во внимание при экспертизе I о Авторское свидетельство } 801101, кл. G 11 С 15/00, 1979 (прототип).

Авторы

Даты

1981-11-30—Публикация

1980-01-03—Подача