1

Изобретение относится к области вычислительной техники и может оьиъ использовано в устройствах дискретной обработки информации.

Известны распределители, содержащие матричный дешифратор на элементах «И - .

Эти распределители конструктивно громоздки и имеют большое число дополнительных связей, ухудшаюших надежность устройства в целом.

Для повышения быстродействия и надежности работы распределителя, последний снабжен многоустойчивым пересчетным блоком и многостабильиым триггером, на пересечении п-ых выходных шин которых включен матричный дешифратор, я-ые выходы элементов которого подключены к (п-1) установочным входам многостабильного триггера, а тактовый .вход .многостабильного трипгера и вход м«огоустойчи1вого пересчетного бло1ка объединены и подключены к .входу ра.епределителя.

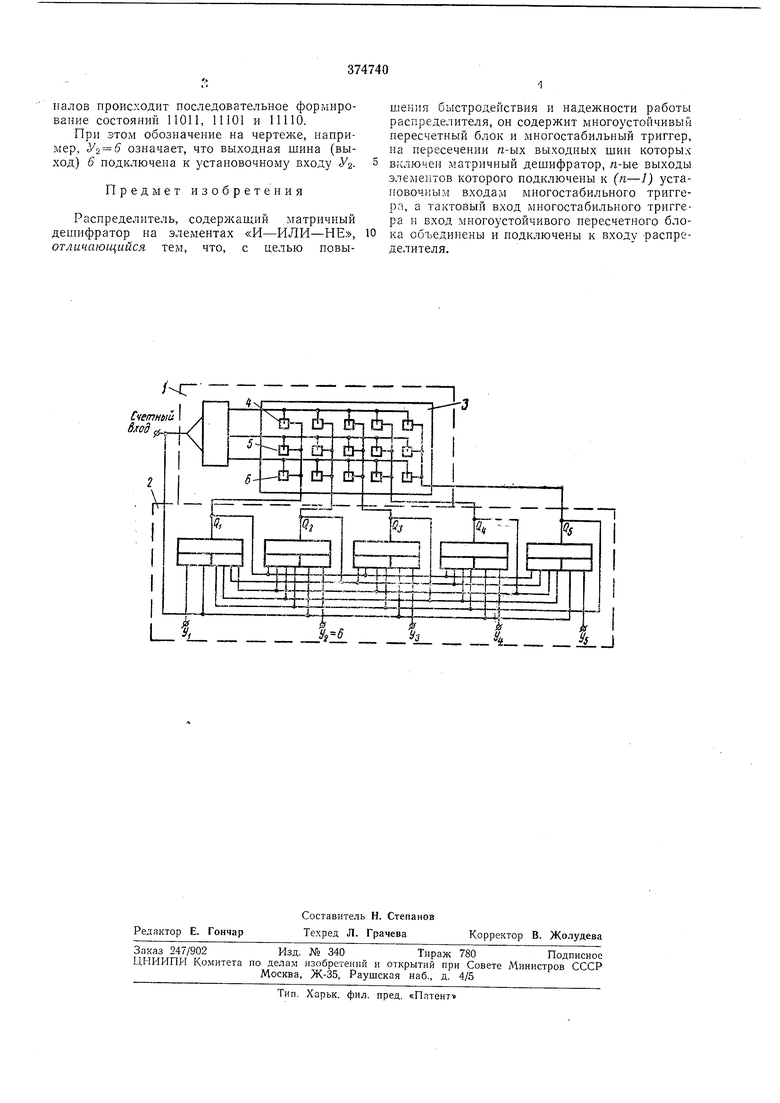

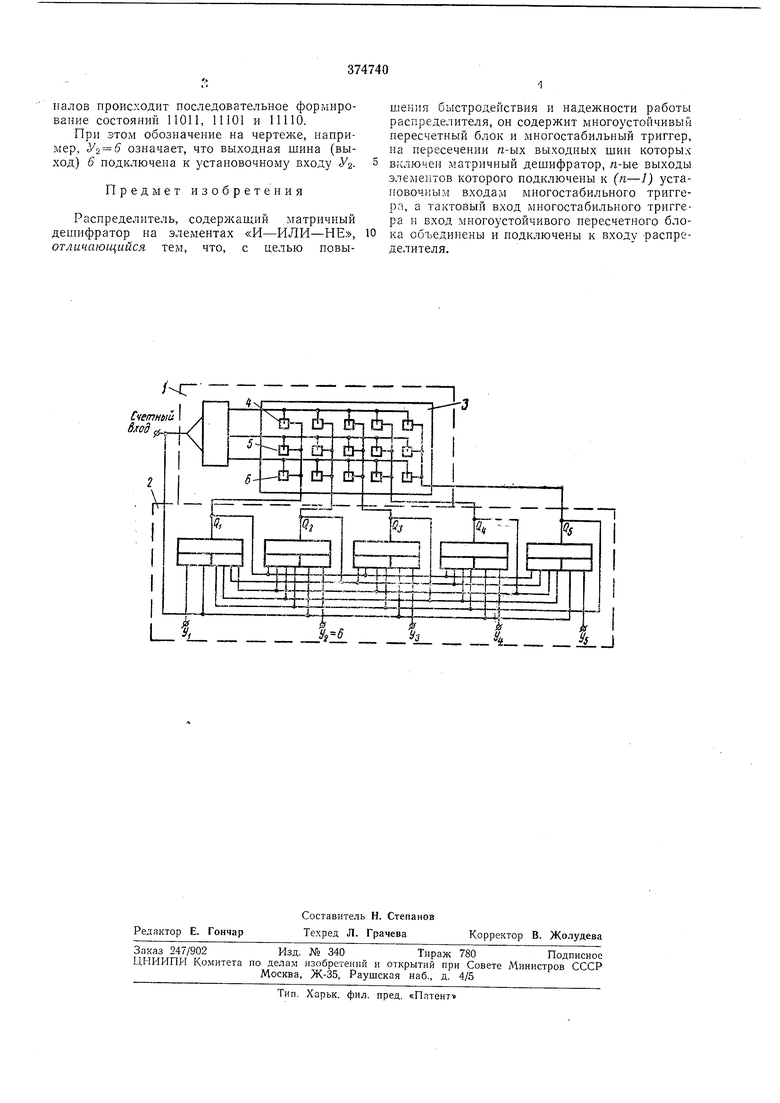

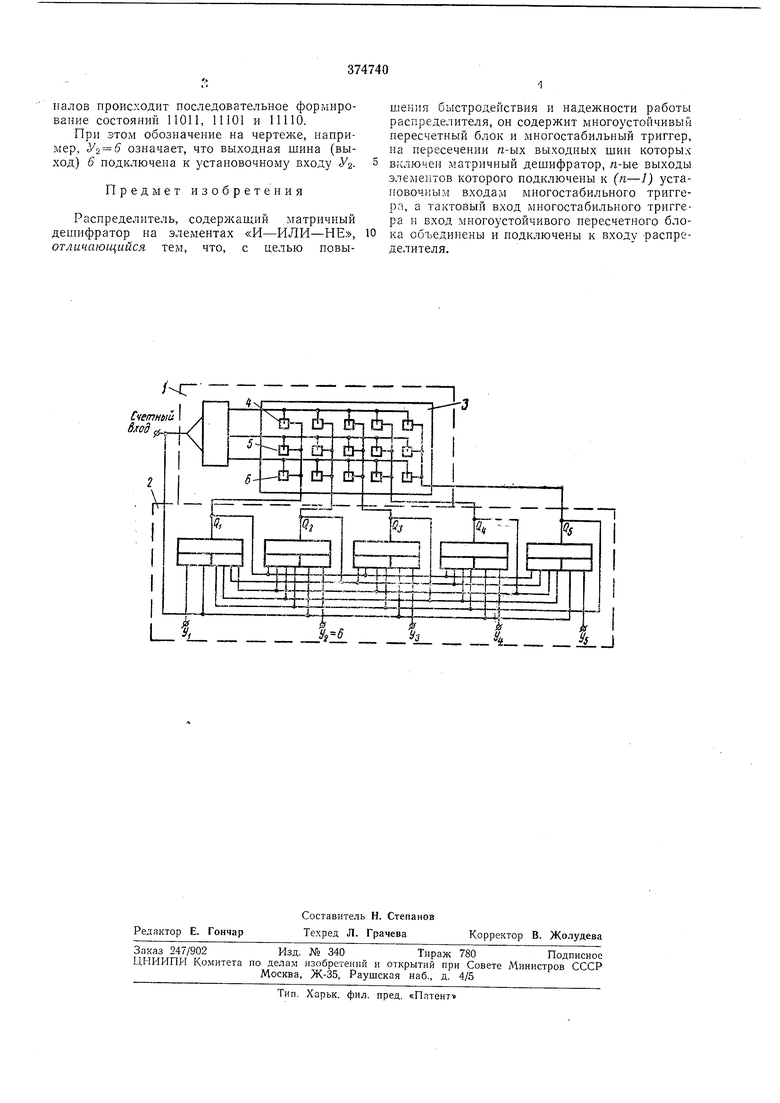

На чертеже приведена функциональная блок-схема предлагаемого устройства.

Работа устройства заключается в следуюш;ем. В исходном положении миогоустойчивый пересчетный блок 7 находится в состоянии, соответствуюш,ем коду 011, и многостабильный триггер 2 (в рассматриваемом случае - пятистабильный) находится в состоянии, когда на

выходах , последнего зафиксирован код 01111 и ,в матричном дешифраторе 3 только на выходе 4 его элементов будет высокий уровень «1.

5 С приходом первого переключающего сигнала на переключающий и одновременно счетный вход состояние иа выходах Qi-Qs .не изменяется, так как на всех установочных входах многоста бильного триггера 2 0 будет «О.

После окончания переключающего сигнала многоустойчивый пересчетный блок / переключается в другое состояние, соответствующее коду 101, и высокий уровень «1 появится па

5 выходе 5.

После окончания второго переключающего сигнала многоустойчивый пересчетный блок / переключается в другое состояние, соответствующее коду ПО, и высокий уровень появится на выходе 6. На установочный вход УЗ поступает сигнал, подготавливающий многостабильный триггер 2 к переключению в следующее состояние.

Переключение осуществляется в момент

5 Tf действия третьего по счету переключающего сигнала, с приходом которого на выходе Q2 формируется «О, и многоустойчивый триггер 2 переключается в следующее состояние, соответствующее коду 10111.

По мере поступления переключающих сигналов происходит последовательное формирование состояний 11011, 11101 и НПО.

При этом обозначение на чертеже, например, У2 означает, что выходная шина (выход) 6 подключена к установочному входу У Предмет изобретения

Распределитель, содержащий матричный дешифратор на элементах «И-ИЛИ-НЕ, отличающийся тем, что, с целью повышения быстродействия и надежности работы распределителя, он содержит многоустойчивый пересчетный блок и многостабильный триггер, на пересечении п-ых выходных шин которых включен матричный дешифратор, /г-ые выходы элементов которого подключены к (п-1) установочным входам многостабильного триггера, а тактовый вход многостабильного триггера и вход многоустойчивого нересчетного блока объединены и подключены к входу распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель | 1983 |

|

SU1130901A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1298910A1 |

| Многоустойчивая пересчетная схема по любому основанию | 1980 |

|

SU961158A1 |

| Матричный коммутатор | 1981 |

|

SU1005308A1 |

| Устройство для определения максимальных путей в графах | 1980 |

|

SU947869A1 |

| Устройство для программного управления | 1980 |

|

SU911468A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Пересчетное устройство с предвари-ТЕльНОй уСТАНОВКОй КОдА | 1979 |

|

SU824444A1 |

Авторы

Даты

1973-01-01—Публикация