(54) МАТРИЧНЫЙ КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1982 |

|

SU1173543A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для индикации работы транспортно-закладочной установки | 1980 |

|

SU909164A1 |

| Каскадный коммутатор | 1985 |

|

SU1322451A1 |

| Каскадный коммутатор | 1989 |

|

SU1608792A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Процессор для умножения вектора на матрицу размером S @ N | 1990 |

|

SU1751780A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для цифровой индикации | 1986 |

|

SU1336094A1 |

1 Изобретение относится к автоматике

и Может быть, использовано в аппаратуре контроля и управления для коммутации сигналов датчиков.

Известен многоканальный коммутатор, содержащий пересчетное устройство с дешифратором tl 1

Недостаток - отсутствие избирательности опроса.

Известен также матричный коммутатор, содержащий пересчетные устройства, входы которых соединены с соответст вуюшими входами дешифратора, выходы последних соединены между собой через коммутирующие элементы по матричной схеме 2 ) Недостаток устройства - низкое быстродействие.

Цель изобретения - увеличение бьгст родействия.

Для достижения цели в матричный коммутатор, содержащий пересчетные устройства, выходы которых соединены с соответствующими входами дещифраторов.

выходы последних соединены между собой через коммутирующие элемент по матричной схеме, введены блок управления предустановки, логические устройства предустазювкн и стробирования, при этом выходы блока управления предустановки соединены со входами логических устройств предустановки, выходы которых соединены со входами соответствующих пересчетных устройств, щина тактовых

10 импульсов подключена через соответствующие логические устройства ст робирования к соответствующим входам соответствующих дешифраторов 1i ко входу первого пересчетного устройства, выход ко15торого соединен с сслугветствукшшм нхо дом второго пересчетного устройства.

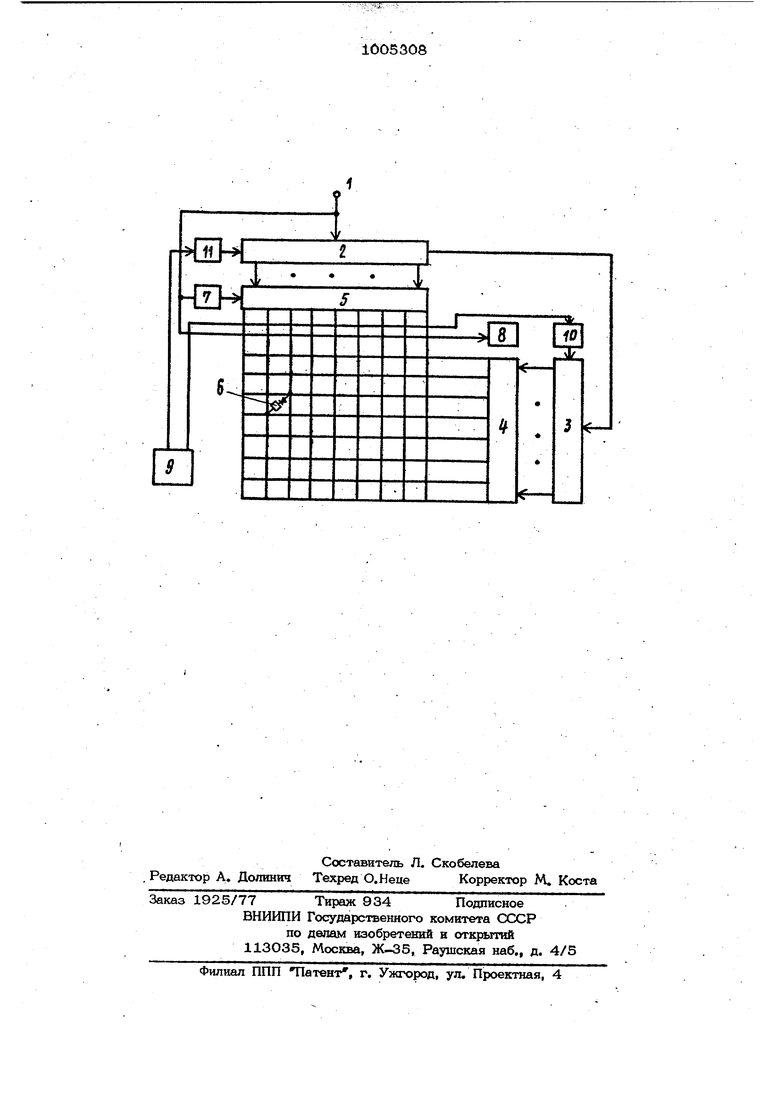

На чертеже изображено предлагаемое устройство.

Устройство содержит шину 1 такто20 вых импульсов (ТИ), пересчетные устройства 2 и 3, дешифраторы 4 и 5, матричное коммутирующее устройство 6, логические устройства стробирования 7 и 8, блок & управления предустановки, лопгческие устройства предустановки 1О и 11. Шина тактовых импульсов 1 через пе вое пересчетное устройство 2, счетный .вход второго пересчетного устройства 3 дешифратор 4 соединена с матричным коммутирующим устройством 6. Шина тактовых импульсов 1 через логическое устройство стробирования 7, дешифратор соединена с матричным коммутирующим устройством 6. Вьосоды блока управлени предустановки 9 соединены параллельно через первое и второе логические устройства предустановки 1О, 11 с пересчетными устройствами 2 и 3. Шина тактовых импульсов 1 через логическое устройство 8 стробирования соединена с дешифратором .4. Устройство работает следующим образом. С шины тактовых импульсов 1 сигнал поступает на счетный вход первого пере счетного устройства 2 и на входы логических устройств стробирования 7 и 8, с выходов которых сигналы поступают н соответствующие входы дещифраторов 5 и 4, на которые также поступают сиг налы с пересчетньЕС устройств 2 и 3; сигнал переполнения с первого пересчет- кого устройства 2 поступает на второе пересчетное устройство 3. Сигналы с бл ка управления предустановкой 9. поступают через логическое устройство предустановки 10 на пересчетаые устройст|ва 2 и 3. Сигналы с выходов дешифраторов 4 и 5 поступают- на матричное коммутирующее устройство 6. Блок управления предустановкой 9 представлен в виде преобразователя десятичного кода номера канала в двоичный и преобразователь напряжения от , О до +4,5 В. Логические устройства предустанонки 10 и 11 представляют «собой логический элемент отрицания НЕ, выходы которых соединены со входами уст. 1 соответствующих триггеров пересчетных устройств 2 и 3. Логические устройства стробирования 7 и 8 представл5аот собой логический элемент отрицания НЕ, выходы которого соединен с входами дещифраторов 5 и 4. Пересчетные устройства 2 и 3 представля ют собой ряд счетных триггеров с установочными входами О и J,, выход .предыдущего счетчика соединен со счетньц/ входом последующего. Дешифраторы 4 и 5 представляют собой набор логическт1х элементов И и НЕ. Входы логических элементов И соединены с соответствующими выходами пересчетных устройств или с выходами логических элементов НЕ, а также с выходом логического устройства стробирования. Входы логического элемента НЕ соединены с соответствующим выходом пересчетного устройства, а вькоды - с соответствующими входами И. С выхода логического элемента И сигнал поступает на коммутирующее устройство, которое представляет собой набор реле, которые соединяют столбцы шин дешифратора с строками шин дешифратора 5 по матричной схеме. Использование предлагаемого коммутатора по сравнению с известным, обеспечивает следующие преимущества: возможность выбора коммутирующего устройства за счет предустановки; за счет связи входа тактовых импульсов со стробирующими входами дешифраторов вдвое увеличивается количество кoм yтируемых устройств без увеличения емкости счетчиков и дешифраторов, т.е. появляется возможность варьировать избирательностью опроса и, кроме того, сокращается время опроса. Формула изобретения Матричный коммутатор, содержащий пересчетные устройства, выходы которых соединены с соответствующими входами дешифраторов, выходы последних соединены между собой через коммутирующие . элементы по матричной схеме, отличающийся тем, что, с целью увеличения быстродействия, в- него введены блок управления предустановки, логические устройства предустановки и стробирования, при этом вь1Ходы 6iioKa управления предустановки соединены с входа,ми логических устройств-предустановки, выходы которых соединены с входами соответствующих пересчетных устройств, шина тактовых импульсов подключена через соответствующие логические уст ройства стробирования к соответствующим входам соответствующих дешифраторов и к входу первого пересчетного устройства, выход которого соединен с соответствующим входам второго пересчетного устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 610302, кл. Н 03 К 17/ОО, 17.О6.76. 2.Авторское свидетельство СССР № 227381, кл. Н 03 К 17/00, 17.07.1967 (прототип).

Авторы

Даты

1983-03-15—Публикация

1981-05-04—Подача