Изобретение опносится к области вычислительной техники и предназначено для использования в системах сбора и обработки учетных данных, решения -статистических задач и т. п.

Известны цифровые вычислительные устройства для обработки учетных данных, содержащие соединенные -последовательно входной блок, -блок памяти текущих данных, процессор, соде|ржащий входные регистры текущих и итоговых данных и операционный блок, блок памяти итоговых данных и выходной блок, причем выходы -блоков памяти текущих и итоговых данных соединены с входами соответствующих входных регистров 1процассо-ра.

Такие устрой-ства не позволяют минимизировать время обращения к блокам памяти текущих итоговых данных, что сужает их функциональные возможности.

Предложенное устройство содержит регистр одноадресного сдвига, вход и выход которого -соединены соответственно с выходом и входом блока -памяти текущих -данных, а операционный блок содержит схему сравнения приз-HaiKOB, вентиль, арифметический узел и схему задания операции, -причем -выходы адресно-а-ссоциативных разрядов входных регистр-ов соединены с входами схем задания операции и сравнения признаков, выходы -котарых соединены с входами арифметического узла непосредственно и через вентиль, второй вход которого соединен с выходами информационных разрядов входного регастра текущих данных, а выходы информационных разрядов входного регистра итоговых данных соединены с третьим входом арифметического узла, выход -которого соедине-н с входом блока намяти итоговых данных.

Это позволяет ра-сширить функциональные возможности устройства.

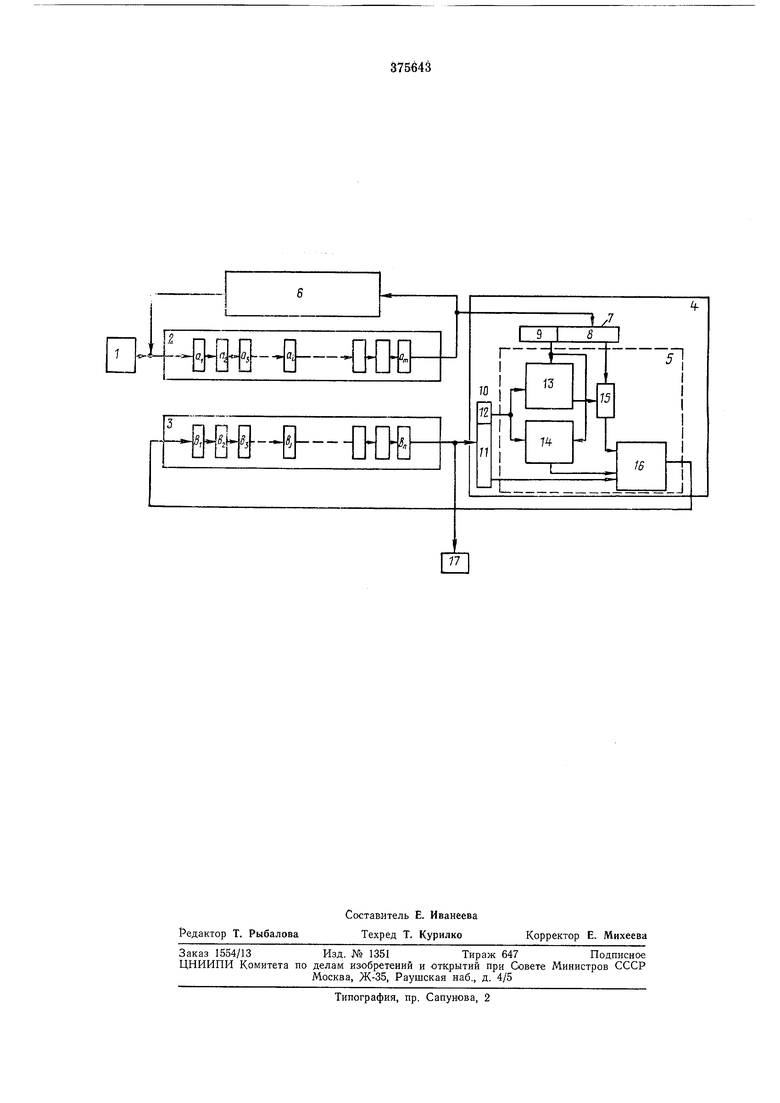

На чертеже показана функциональная схема устройства.

Устройство содержит входной бл-ок 1, блокп 2 и 5 памяти текущих и итоговых данных, процессор 4, операци-онный блок 5, регистр 6 одноадресного сдвига, входной регистр 7 текущих данных с информационными 8 и адресно-ассоциативными 9 разрядами, входной регистр 10 итоговых данных с информационными 11 и адресно-а-ссоциативными 12 разрядами, схему 13 сравнения признаков, схему 14 задания операции, вентиль 15, арифметический узел 16 и выходной блок 17.

Устрой-ство работает следующим образом.

Инф-ормация об объекте поступает в устр-ойство через входной блок 1, в котором происходит кодирование данных (трансляция с кодов канала связи на внутренний язык устройства), а также вы-борка из входного елова :раЗ|рядов, используемых ори обработке информации и разделение выделенной части на информационную и ассоциативно-адр.есную. Из входного блока информация об объекте лоступает в блок памяти текущих данных и запи-сывается в его свободные ячейки.

Блок 2 памяти текущих данных организован по Принципу динамической ламяти. Поэтому во входной регистр 7 текущих данных за полиый цикл работы блока ламяти последовательно поступают ;все текущие данные, с ячеек Аналогично выполнен блок 3 памяти итоговых данных. За полный цикл его работы на входной :регист:р итоговых данных последовательно поступают все слюва, хра.нящиеся в ячейках 6 -ЬпПо Огнощению к входному блоку 1 блОК памяти текущих данных является памятью, магазинного тила, что позволяет заполнять ячейки памяти блока текущих данных без использования специальных средств управления для Поиска занесенного лоследним СЛОва в массиве. Последовательно с блоком памяти текущих данных включен регистр 6 одноадресного сдвига, что позволяет через полный цикл работы блока 2 расположить слова в его ячейках со сдвигом на одну адресную ячейку. ТаКИМ образом, л)ри поступлении новых слов из входного блока в фиксированные моменты времени с интервалом, равеым времени полного цикла, слово из Входного блока пОСтупает в свободную ячейку. Слова, записанные в ячейках блоков 2 и 3 одновременно поступают во входные регистры 7 п 10 процессора 4.

АоСОциативно-адресные части слов из ассоциатив но-адресных разрядов 9 и 12 поступают в схему 13 сравнения признаков, определяющую отнощенйе слова, поступившего из блока текущих данных, к тому классу слов, которые упорядоченно отображаются в соответ-. ствующее слово из блока итоговых данных. При сов.паденни определенных разрядов ассоциативно-адреоных частей двух слов вентиль 15 открывается, и информационная часть елова из блока текущих данных поступает в арифметический узел 16. Одновременно со сравнением ассоциативно-адресных частей слов схемой сравнения признаков, анализируется ассоциативцо-адресные части слов схемой задания операции (сложение ил-и вычитание), и сигнал со схемы 14 дает команду в арифметический узел на выполнение одной из выбранных операций. Если вентиль 15 открыт, то в арифметическом узле 16 происходит изменение содержимого информационных разрядов ячейки поступившей на обработку в 1опе;рационный блок 5. Когда ассоциативноад1ресные части слов не совпадают, вентиль

15 остается закрытым, на второй вход арифметического узла 16 информация не поступает, и инф0|рмационная часть слова из блОКа ИТОГОВЫХ данных проходит через опер-ационный блок 5 без изменения.

Вследствие того, что в каждом цикле ра.боты блоков 2 и 3 слова блока 2 оказываются сдвинутыми относительно слов в блоке 3 (благодаря. И1епользованию регистра 6 одноадресного сдвига), на входные регистры процессора в каждый., т акт сдвига поступают новые пары слов из блоков 2 и 3, в результате чего через К Циклов 0.бращен1ия к блокам 2 и 3, где К. число ячеек памяти в блоке большего объема, все слова из одного блока оказываются совместно обработанными со всеми словами из другого блока.

Информация., х ранящаяся в блоке итоговых данных, выбирается выходным блоком 17 в соответствии с их ассоциативно-адресньми признаками и печатается в виде таблиц отчетных документов. Этот блок выполняет также функции сопряжения блока итоговых данных с устройствами вывода (электронные пульты отображения информации, печатающие устройства, перфораторы И т. д.).

Предмет изобретения

Цифровое вцчислительное устройство для обработки учетных данных, содержащее соединенные последовательно входнОй блок, блока памяти текущих данных, процессор, содержащий входные регистры текущих и итоговых данных и операционный блок, блок памяти итоговых данных и выходной блок, причем выходы блоков памяти- текущих и итоговых данных соединены с входами соответствующих входных регистрОв процессора, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно регистр одноадресного сдвига, вход и выход которого соединены соответственно с выходом и входом блока памяти- текущих данных, а операционный блок содержит схему сравнения признаков, вентиль, арифметический узел и схему задания операции, причем выходы адресно-ассоциативных разрядОВ входны-х регистров соединены с входами схем задания Операции и сравнения признаков, выходы которых соединены с входами арифметического узла непосредстеенно и через вентиль, второй вход которого соединен с в.ыходами информационных разрядов входного регистра текущих данных, а выходы информационных разрядов входного регистра итоговых данных соединены.с Т1ретьим входом арифмбтичесКОго узла, выход которого соединен с входом блока памяти итоговых данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки отчетных данных | 1983 |

|

SU1151984A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для матричной обработки данных | 1980 |

|

SU792260A1 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

Авторы

Даты

1973-01-01—Публикация