1

Изобретение относится к области автоматики и вычислительной техники.

Известно частотно-импульсное множительное устройство 1, содержащее счетчики импульсов, триггеры, элементы И и ИЛИ и дешифратор.

Однако оно имеет пониженную точность вычислений и органиченный диапазон изменения входных частотно-импульсных сигналов.

Известно также частотно-импульсное множительно-делительное устройство 2, содержащее элементы И и ИЛР1, триггеры, элементы задержки, регистр и два счетчика импульсов, счетный вход первого из которых подключен к выходу первого элемента И, соединенного первым входом с первыми входами второго и третьего элементов И и входом частоты делителя, а вторым входом - с вторым входом второго элемента И и выходом первого триггера, подключенного установочным входом к входам первых трех элементов задержки, входу обнуления регистра и выходу четвертого элемента И, соединенного первым входом с первым входом пятого элемента И н входом запуска устройства, а вторым входом - с входо.м частоты первого сомножителя н первым входом шестого элемента И, второй вход которого подключен к первому выходу второго триггера. Второй выход второго триггера связан с вторым входом пятого элемента И, а установочный вход - с выходом седьмого элемента И, подключенного нервым входом к выходу шестого элемента

И, а вторым входом - к выходу третьего триггера, соединенного счетным входом с выходом первого элемента задержки. Вход частоты второго сомножителя подключен к третьему входу пятого элемента И, соединенного выходом с вычитающим входом второго счетчика импульсов, и нервому входу восьмого элемента И, соединенного вторым входом с выходом четвертого триггера и вторым входом третьего элемента И, подключенного

выходом к первому установочному входу пятого триггера, выход которого соединен с третьим входом второго элемента И, подключенного выходом через четвертый элемент задержки к счетному входу четвертого триггера. Выходы второго и третьего элементов задержки соединены соответственно с выходом обнуления нервого счетчика импульсов и первыми входами элементов И переписи первой группы, связанных вторыми входами с

поразрядными выходамн первого счетчика нмпульсов, а выходами через регистр - с первыми входами элементов И нереписи второй грунпы, вторые входы которых подключены к выходу второго счетчика импульсов,

а выходы - к поразрядным входам второго

счетчика импульсов, причем, выход элемента ИЛИ соедипен с выходом устройства.

Недостатком прототипа является ограниченный диапазон изменения входных частот.

Цель изобретения - расширение диапазона изменения входных частот.

Это достигается тем, что в частотно-импульсное множительно-делительиое устройство дополнительно введены элементы И и ИЛИ, триггер, инвертор, реверсивный счетчик и дешифратор, соединенный входами с выходами первого счетчика импульсов, а выходом - с первыми входами первых двух дополнительных элементов И п входом ннвертора, выход которого подключен к первому входу третьего дополнительного элемента И, соединенного вторым входом с выходом второго счетчика импульсов и вторым входом первого дополнительного элемента И, подключенного выходом к вычитаюш,е.му входу реверсивного счетчика. Поразрядиые выходы счетчика соединены с входами дополнительного элемента ИЛИ, подключенного выходом к третьему входу первого дополнительного элемента И, а суммируюш,ий вход - с выходом четвертого дополнительного элемента И, первый вход которого подключен к выходу восьмого основного элемента И я первому входу пятого дополнительного элемента И. Вторые входы четвертого и пятого дополнительных элементов И соединены с соответствующими выходами дополнительного триггера, подключенного установочным входом к первому установочному входу пятого основного триггера, соединенного вторым установочным входом с выходом второго дополнительного элемента И, второй вход которого подключен к выходу четвертого основного элемента И. Выходы первого, третьего и пятого дополнительных элементов И соединены с соответствующими входами основного элемента ИЛИ.

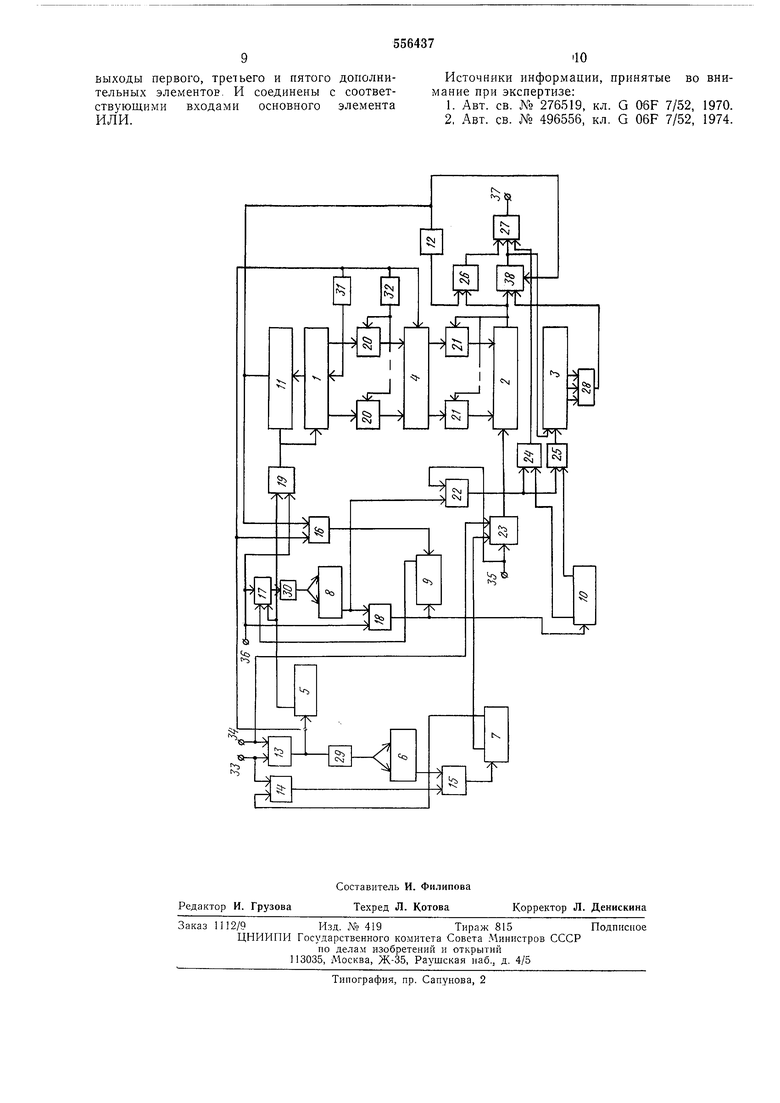

На чертеже представлена блок-схема устройства.

Устройство содержит счетчики 1, 2 импульсов, реверсивный счетчик 3 импульсов, регистр 4 памяти, триггеры 5-10, дешифратор 11, инвертор 12, элементы И 13-19, элементы И 20 переписи первой группы, элементы И 21 переписи второй группы, элементы И 22-26, элементы ИЛИ 27, 28, элементы задержки 29-32, клеммы подачи частоты первого сомножителя 33, сигнала запуска 34, подачи частоты второго сомножителя 35 и частоты делителя 36, выходную клемму 37 и элемент И 38.

Работает устройство в двух режимах.

В первом режиме погрешность умножения определяется в основном погрешностью отношения частоты первого сомножителя FI к частоте делителя FZ. Нри этом количество импульсов «1 частоты FZ, накапливаемое в счетчике 1 в течение периода частоты FI, больше минимально допустимого количества импульсов л.

которое определяется задан1миидоп

ПОЙ допустимой погрешностью.

Во втором режиме работы погрешность мпожительно-делительной операции не за

висит уже от отношения частот -- и опf

ределяется лишь отношением частоты , FZ к частоте Fa.

В данном режиме работы количество им пульсов «1 меньше л,

миндопНервый режим работы оиределяется отсутствием сигнала на выходе дешифратора 11, а второй режим - наличием сигнала.

Множительно-делительиое устройство работает следующим образом.

Входные сигналы первой последовательности с частотой следования FI, характеризующие один из сомножителей, подаются на клемму 33, сигналы второй последовательности с частотой следования Fa, характеризующей другой сомножитель, - на клемму 35. Сигналы третьей последовательности с частотой следования FZ, характеризующие делитель, поступают на клемму 36. Далее сигналы последовательности с частотой FI подаются на входы элементов И 13, 14, сиппалы с частотой FS - на входы элементов И 22, 23, сигиалы с частотой FZ - на входы элементов И 17 и 19.

В исходном состоянии счетчики 1, 2, 3, регистр 4 иамяти и триггеры, обнулены. В момент ti на клемму 34 подается сигнал разрешения. При этом первый после момента ti импульс, подаваемый на клемму 33, проходит через элемент И 13 и переводит триггер 5 в единичиое состояние. В результате открывается элемент И 19 и на вход счетчика 1 начинают проходить сигиалы делителя с частотой FZ (периодом TZ), которые накапливаются в счетчике до момента поступления следующего входного сигнала на клемму 33. Очевидно, что частота FZ должна быть больше частоты FI в несколько раз.

Количество импульсов с частотой FZ, поступивших в течение периода Ti последовательности импульсов с частотой FI на вход счетчика I, определяется как

TI -t

С поступлением на клемму 33 следующего (второго после подачи сигнала разрешения) импульса информация, накопления в счетчике 1, передается через элементы И 20 переписи первой группы в регистр 4 памяти, где запоминается, а счетчик обнуляется. Необходимый временной сдвиг между моментами передачи информации и обнулением счетчика осуществляется с помощью элементов задержки 31, 32. Далее процесс повторяется. С приходом каждого последующего импульса из последовательности с частотой следования FI он обнуляет регистр 4 памяти и передает накопленную в счетчике информацию в регистр памяти.

Необходимая задержка в подаче сигналов на вход счетчика 2 в данном режиме осуществляется с помощью схемы, состоящей из триггеров 6, 7, элементов И 14, 15 и элемента задержки 29. После подачи сигнала разрешения на клемму 34 в момент времени, первый после момента t, сигнал из ИМПУЛЬСНОЙ последовательности с частотой FI проходит на выходы элементов И 13, 14. При этом с выхода элемента И 13 он поступает через элемент задержки 29 на счетный вход триггера 6, переводя его из нулевого в единичное состояние. Очевидно, что при этом сигнал с выхода элемента И 14 не проходит на выход элемента И 15, так как отпирающий сигнал с тпиггера б подается на его вход с задержкой за счет элемента 29. При поступлении следующего сигнала на клемму 33 сигнал с выхода элемента И 14 проходит на выход элемента И 15. переводя триггер 7 в единичное состояние. В результате открывается элемент И 23 и на вход счетчика 2 начинают подаваться импульсы с частотой следования F. С переводом триггера 7 в единичное состояние элемент И 14 запирается для сигналов, подаваемых на клемму 33. Для получения информации в результате в течение первого периода частоты р2 в данном режиме СЛУЖИТ схема, состоящая из элементов И 17. 18. 22, триггеров 8, 9 и элемента задержки 30. После подачи сигнала разрещения на клемму 34, прохождения импульса с клеммы 33 через элемент И 13 и перевода триггера 5 в единичное состояние на выход элемента И 17 проходит сигнал последовательности с частотой FZОдновременно ИМПУЛЬС с клеммы 36 подается на вход элемента И 18. С выхода элемента И 17 сигнал через элемент задержки 30 поступает на счетный вход триггера 8, переводя его в единичное состояние. При этом открывается элемент И 22 и на его выход проходят сигналы с клеммы 35.

Указанные сигналы через открытый элемент И 24 и далее через элемент ИЛИ 27 подаются на выходную клемму 37 устройства, образуя первые сигналы результата. При поступлении следующего сигнала с клеммы 36 он проходит через элемент И 18 и триггеры 9, 10 устанавливаются в единичное состояние, а в случае подачи сигнала на счетный вход триггера 8, последний переводится в нулевое состояние. При этом запираются элементы И 17, 18, 22, 24 и открывается элемент И 15. В результате выдача импульсов с клеммы 35 прекращается, что необходимо для нормального функционирования устройства.

Сигналы пересчета с выхода счетчика 2 подаются через элемент И 26 и далее через элемент ИЛИ 27 иа выходную клемму 37, образуя равномерную иоследовательиость импульсов, характеризующую результат, я также на управляющие входы элементов И 21 переписи второй группы. D -сзультате этого информация, запомненная в реriTcfpe 4 памяти, периодически передается через элементы И 21 в счетчик 2, образуя его исходиую уставку. В зависимости от величикы исходной уставки на выходе счетчика 2 устанавливается вполне определенная частота. При этом каждый последующий ИМПУЛЬС частоты осуществляет периодический сброс старой информации в регистре 4 и запись новой информации. При этом период последовательности импульсов на выходе счетчика 2 определяется выражением

Ti

-т -т вых - 3

г.,

или В частотном представлении F -ZlA

вых - г

Таким образом, на выходе устройства в первом режиме имеет место результат множительно-делительной операции с равномерным расипеделением выходных сигналов.

При увеличении значения частоты входных сигиалов (например, FI) и по достижении неравенства 1.„инчоп момент tz на выходе дещифратора И появляется высокий уровень напряжения, чем определяется второй режим работы множительно-делительного устройства. Элемент И 16 открывается, элемент И 26 закрывается и подается высокий уровень напряжения иа один из входов элементов И 25, 38.

Первый же сигнал с выхода элемента И 13

после момента U проходит через элемент И 16 и переводит триггер 9 в нулевое состояние. Это приводит к отпиранию элемента И 17. Далее сигнал с клеммы 36 подается через элемент И 17 и переводит триггер 8 в едииичпое состояние. При этом открываются элементы И 18. 22 и через элемент И 22 и далее чепез элемент И 25 на суммирующий вход реверсивного счетчика 3 начинают проходить сигналы с клеммы 35 ИМПУЛЬСНОЙ последовательности с частотой F.. Указанные импульсы суммируются в счетчике 3. ИМПУЛЬСЫ на вход реверсивного счетчика поступают до момента подачи следующего сигнала с клеммы 36, который проходит через элемент И 18 на вход

триггера 9, переводя его в единичное состояние, и далее устанавливает триггер 8 в иулевое состояние, заиирая таким образом элементы И 18, 22. Далее описанный процесс периодически повторяется с поступлением

каждого последующего импульса частоты F. Следует отметить, что с поступлением первого же импульса на.вход реверсивного счетчика 3 на выходе элемента ИЛИ 28, входы которого связаиы с разрядными выходами счетчика 3, вырабатывается высокий уровень напряжения, в результате чего отпирается элемент И 38 для сигналов с выхода счетчика 2. Указаииые сигналы с выхода счетчика 2 пролг. на вход э.тсмеитя И 38 и далее на вычитающий вход счетчика 3 и через элемент

ИЛИ 27 на выход устройства. При этом сигналы проходят на выход устройства до момента обнзления счетчика 3. В момент обнуления указанного счетчика на выходе элемента ИЛИ 28 исчезает высокий уровень напряжения п элемент И 38 запирается. Далее описанный процесс периодически повторяется. Причем количество импульсов, записанное в течение одного цикла в реверсивный счетчик 3, определяется выражением

TZ

счз - 3

и представляет собой фактически коэффициент умножения частоты F.

Таким образом, предложенное устройство обеспечивает существенное расширение диапазона входных частот, так как позволяет повысить верхний предел частоты Р и понизить нижний предел частот РЧ и F. Это обусловлено тем, что в первом режиме, который

реализуется при ,

погрешность

множительно-делительной операции опредеP

Поэтоляется в основном отношением

му здесь накладываются ограничения на увеличения верхнего FI и уменьшение нижнего предела Р-г, и РзВо втором режиме () погрешность умножения не зависит от погрешности

Я, f, и определяется отношением частот -- .

2РЗ

Причем это отношение тем меньше, чем больше значение частоты я и меньше значение 2. В результате в предложенном устройстве обеспечивается существенное расширение диапазона изменения входных частот без уменьшения точности.

Формула изобретения

Частотно-импульсное множительно-делительное устройство, содержащее элементы И ИЛИ, триггеры, элементы задержки, регистр и два счетчика импульсов, счетный вход первого из которых подключен к выходу первого элемента И, соединенного первым входом с первыми входами второго и третьего элементов И и входом частоты делителя, а вторым входом - с вторым входом второго элемента И и выходом первого триггера, подключенного з становочным входом к входам первых трех элементов задержки, входу обнуления регистра и выходу четвертого элемента И, соединенного первым входом с первым входом пятого элемента И и входом запуска устройства, а вторым входом - с входом частоты первого сомножителя и первым входом iiecToro элемента И, второй вход которого подключен к первому выходу второго триггера, соединенного вторым выходом с вторым, входом пятого элемента И, а зстановочным входом - с выходом седьмого элемента И, подклЕоченного первым входом к выходу шестого элемента И, а вторым входом - к выходу третьего триггера, соединенного счетны.м входом с выходом первого элемента задержки, причем вход частоты второго сомножителя подключен к третьему входу пятого

элемента И, соединенного выходом с вычитающим входом второго счетчика импульсов, и первому входу восьмого элемента И, соединенного вторым входом с выходом четвертого триггера и вторым входом третьего элемента

И, подключенного выходом к первому установочному входу пятого триггера, выход которого соединен с третьим входом второго элемента И, подключенного выходом через четвертый элемент задержки к счетному входу

четвертого триггера, а выходы второго и третьего элементов задержки соединены соответственно с входом обнуления первого счетчик импзльсов и первыми входами элементов И переписи первой группы, подключенных вторыми входами к поразрядным выходам первого счетчика импульсов, а выходами соединенных через регистр с первыми входами элементов И переписи второй группы, вторые входы которых подключены к выходу второго

счетчика импульса, а выходы - к поразрядным входам второго счетчика импульсов, причем выход элемента ИЛИ соединен с выходом устройства, отличающееся тем, что, с целью расширения диапазона изменения

входных частот, в него дополнительно введены элементы И и ИЛИ, триггер, инвертор, реверсивный счетчик и дешифратор, соединенный входами с выходами первого счетчика импульсов, а выходом - с первыми входами первых двух дополнительных элементов И и входом инвертора, выход которого подключен к первому входу третьего дополнительного элемента И, соединенного вторым входом с выходом второго Счетчика импульсов и вторым входом первого дополнительного элемента И, подключенного выходом к вычитающему входу реверсивного счетчика, поразрядные выходы которого соединены с входами дополнительного элемента ИЛИ,

подключенного выходом к третьему входу первого дополнительного элемента И, а суммирующий вход соединен с выходом четвертого дополнительного элемента И, первый вход которого подключен к выходу восьмого

основного элемента И и первому входу пятого дополнительного элемента И, причем вторые входы четвертого и пятого дополнительных элементов И соединены с соответствующими выходами дополнительного триггера,

подключенного установочным входом к первому установочному входу пятого основного триггера, соединенного вторым установочным входом с выходом второго дополнительного элемента И, второй вход которого подключен

к выходу четвертого основного элемента И, а

выходы первого, третьего и пятого дополнительных элементов. И соединены с соответствующими входами основного элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. 276519, кл. G 06F 7/52, 1970.

2,Авт. св. № 496556, кл. G 06F 7/52, 1974.

Авторы

Даты

1977-04-30—Публикация

1975-09-15—Подача