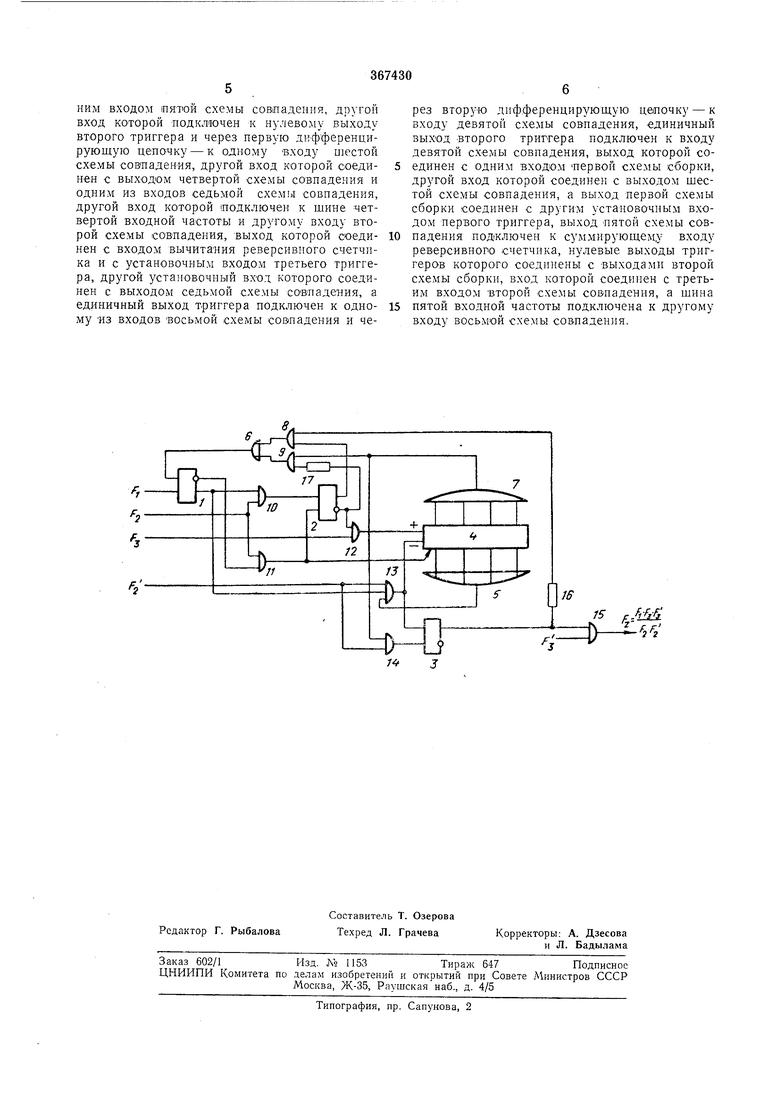

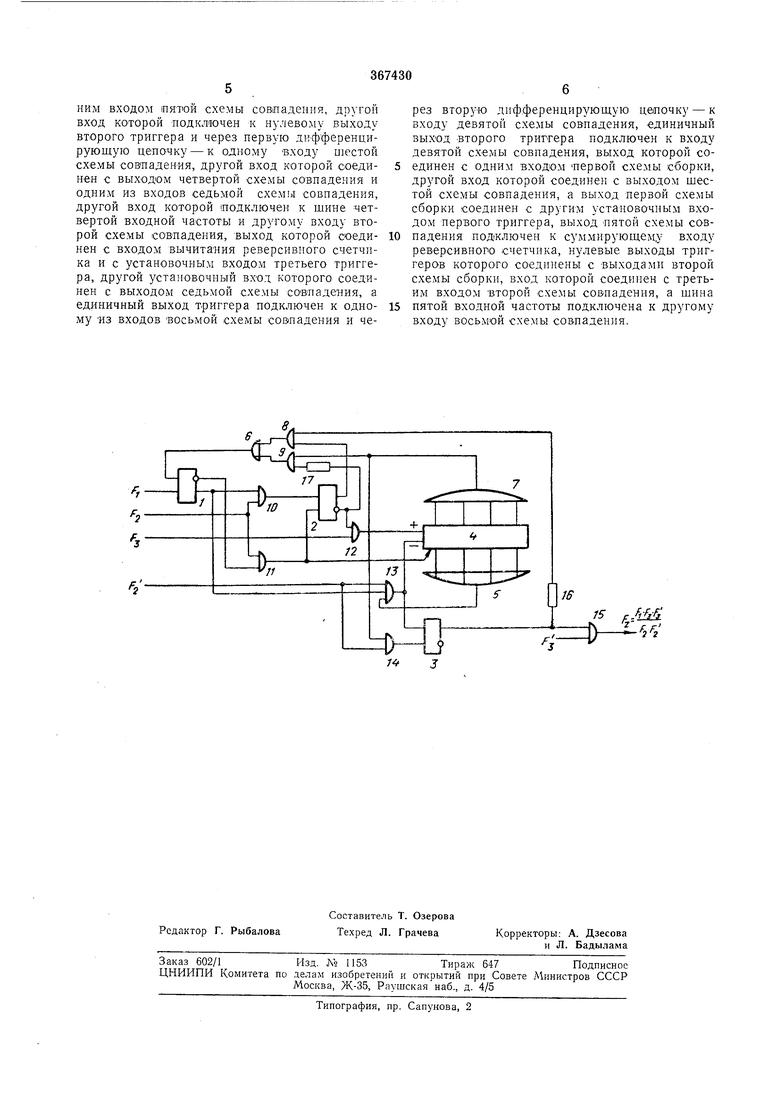

Изобретение относится к области вычислительной техники и может быть использовано для выполнения множительно-делительных операций над переменными, представленными частотой повтарения импульсов как в качестве автоноМНого узла, так и в качестве составной части замкнутых частотно-импульсных моделей. Известно частотно-импульсное множительно-делительное устройство, содержащее два триггера и импульсно-потенциальные схемы совпадения, реализующее зависимость вида р . р --- . В известном устройстве при поFступлении импульса частоты FI триггер устанавливается в единичное состояние, открывая схему совпадения и импульсы частоты F формируют на выходе триггера строб длительностью т: -, за время которого на выход РЛ устройства Проходят импульсы -частоты F. Однако такое устройство не обеспечивает получения множительно-делительных операций «ад числоМ входных переменных больше трех, что ограничивает его функциональные ВОЗМ.ОЖНОСТИ (например, получение кубической или квадратичной зависимостей). Цель изобретения-построение частотноимпульсното множительно-делительного устРойства разомкнутого типа с расщ-иренными функциональными возможностями, реализующего зависим-ость вида 7 j Это достигается -подключением входов реверсивнюго счетчика к выходам схем совпадения, выходы реверсивного счетчика соединены с входами схем сборки -и совпадения, -потенциалы на выходе которых управляют прохождением частоты на вход триггера, управляющего прохождением частоты на выход устройства. На чертеже показана схема устройства. Устройство содержит триггеры /, 2, 3 реверсивный счетчик 4, схемы 5, 6 сборки, схемы совпадения 7-15 и дефференцирующие цепочки 16, 17. Шина входной частоты fi подключена к установочному входу триггера 1, единичным выходом соединенного с входами схем 10 и 13 совпадения. Выход схемы 10 связан с входом установки единицы триггера 2, а второй вход- с шиной входной частоты FZ и входом схемы // совпадения, другим входом соединенной с нулевым выходом триггера /. Выход схемы П совпадения подключен к входу установки нуля триггера 2 и шяне установки нуля реверсивного счетчика 4, суммирующий вход которого соединен с выходом схемы 12 совпадеНия, одним входом подключенной к шние входной частоты F, а другим - к нулевому выходу триггера 2 и через дифференцирующую цеиочку /7 к входу схемы 9 совпадения. 5 Вычитающий вход реверсивного счетчика соединен с входом установки единицы триггера 3 и выходом схемы 13, вход которой связан с выходом схемы 5 сборки, входами подключенной к единичным выходам триггеров ре- 10 версивного счетчика. Нулевые выходы триггеров реверсивного счетчика соединены с входа.ми схемы 7 совпадения, выход которой связан с входом схем 9 и 14. Другой вход схемы 14 связан с шитеой входной частоты F и вхо- 15 дом схемы 13, а выход схемы 14 совиадения соединен с входом установки нуля триггера 3. Выход устройства подключен к выходу схемы 15, один из входов которой соединен с шиной входной частоты F,, а другой - с единичным 20 выходом триггера 3 и через дифференцирующую цепочку 16 с входом схемы 8, второй вход которой подключен к единичному выходу триггера 2. Выходы схем 8, 9 соединены с входамИ схемы 6, вьТходом связанной с вхо- 25 дом установки нуля триггера. /. Работу устройства рассмотрим с момента прихода импульса частоты р2 считая, что триггер 1 находится в нулевом состоянии, тогда импульс частоты / 2/минуя открытую схе- 30 му 11 совпадения устанавлищает в нулевое сост-ояние реверсивный счетчик и триггер 2. Пришедщие позже импульсы частоты FS, через отк рытую схему 2 поступают на суммирующий вход реверсивного счетчика и к моменту 35 прихода каждого импульса частоты F в реверсивном счетчике запоминается число С приходом импульса частоты f, триггер / ° устанавливается в единичное состо яние. Он запрещает прохождение импульсов частоты FZ на вход установки нуля триггера 2 и реверсивного счетчика и разрещает прохожде- 45 ние импульсов частоты F, через открытую схему 10 совпадения «а вход установки единицы триггера 2, с -приходом которого схема 12 совпадения закрывается и на суммирующий вход реверсивного счетчика импульсы частоты Fa 50 не подаются. Таким образом, на суммиру ощий вход поступает число импульсов NI - . Кроме того, триггер / разрешает про-хождение импульсов частоты Fz на вычитающий вход 55 реверсивного счетчика и вход, установки единицы триггера 3 в случае, если реверсивный счетчик находится не в -нулевом состоянии, что фиксируется схемойi5 сборки. С приходом //1-го импульса частоты Fz на 60 вычнтающий вход, реверсивный счетчик занимает нулевое положение и следующий импульс частоты Fs проходит через открытую схему 14 совпадения на вход установки нуля триггера 3. Таким об1разом, на выходе тригге- 65 ра 5 формируется прямоугольный имлульс длительностью , л .Д- -А-. В течение которого на выход устройства постунают импульсы частоты Рз. На выход уст1ройства за время Т - поступает N -.. F..F, импульсов, а среднее значение частотно-им Ульснои последовательности на выходе оиреДеляется выражением Fi-FfFs F.F Импульс, сформированный дифференцирующей цепочкой 16, от заднего фронта прямоугольного имиульса длительностью TI при единичном состоянии триггера 2 устанавливает триггер / в нулевое состояние. Если частота Р2 Рз и формирование строба на выходе триггера 3 зажанчивается раньще, чем триггер принимает единичное состояние, триггер 1 возвращается в нулевое состояние импульсом от фронта триггера 2 при условии, что код реверсивного счетчика равен нулю, В предлагаемом устройстве Fz ограничивается снизу тем условием, чтобы к приводу следующего импульса FI закончилось формирование строба длительностью TI N - . Как видно из работы устройства, имлульсы частоты Fz (Поступают на вход устройства непосредственно после прихода импульса частоты fa независимо от момента прихода частоты F. Предмет изобретения Частотно - импульсное множительно - делительное устройство, содержащее первый триггер, один установочный вход которого соеди„е„ входной частоты, единич . которого подключен к одному из одов первой я второй схем совпадения, а нулевой выход соединен с одним входом третьей, схемы совпадения; второй триггер, каждый установочный вход которого соединен соответственно с выходом первой и третьей схем совпадения, другие входы жоторых объединены и подключены к щине второй входной частоты; реверсивный счетчик, щина установки нуля которого соединена с выходом третьей схемы совпадения, а нулевые выходы триггеров этого счетчика подключены к входам четвертой схемы совпадения, отличающееся тем, что, с целью расширения области применения устройства, оно содержит пятую, шестую, седьмую, восьмую и девятую схемы совпадения, третий триггер, две схемы и две дифференцирующие цепочки, причем шина третьей входной частоты соединена с одним входом 1ПЯТОЙ схемы совпадения, другой вход которой подключен к нулевому выходу второго триггера и через первую дигфференцирующую цепочку - к одному входу шестой схемы совпадения, другой вход которой соединен с выходом четвертой схемы совпадения и одним из входов седьмой схемы совпадения, другой вход которой подключен к шине четвертой входной частоты и другому входу второй схемы совпадения, выход которой соединен с входом вычитания реверсивного счетчика и с установочным входом третьего триггера, другой установочный вход, которого соединен с выходом седьмой схел1ы совпадения, а единичный выход триггера подключен к одному ИЗ входов ВОСЬМОЙ схемы сов-падения и через вторую дифференцирующую цепочку - к входу девятой схемы совпадения, единичный выход Второго триггера подключен к входу девятой схемы совпадения, выход которой соединен с одним входом первой схемы сборки, другой вход которой соединен с выходом шестой схемы совпадения, а выход первой схемы сборки соединен с другим установочным входом первого триггера, выход пятой схемы совпадения подключен к суммирующему входу реверсивного счетчика, нулевые выходы триггеров которого соединены с выходами второй схемы сборки, вход которой соединен с третьим входом второй схемы совпадения, а шина пятой входной частоты подключена к другому входу восьмой схемы совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО-^ | 1973 |

|

SU375651A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU424188A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| ОДТЕНТНО-ТЕХНН-Г- :^':и|БИБЛИОТЕКА | 1970 |

|

SU287404A1 |

| Частотно-импульсное множительноделительное устройство | 1977 |

|

SU605213A1 |

| Частотно-импульсное множительноделительное устройство | 1975 |

|

SU596944A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| Частно-импульсное множительно-делительное устройство | 1978 |

|

SU763913A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ и ДЕЛЕНИЯ ЧАСТОТНО- ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU333564A1 |

| Умножитель частоты следования импульсов | 1973 |

|

SU450186A2 |

/5- pfiMi

i-r

г- f t-ji-j

Авторы

Даты

1973-01-01—Публикация