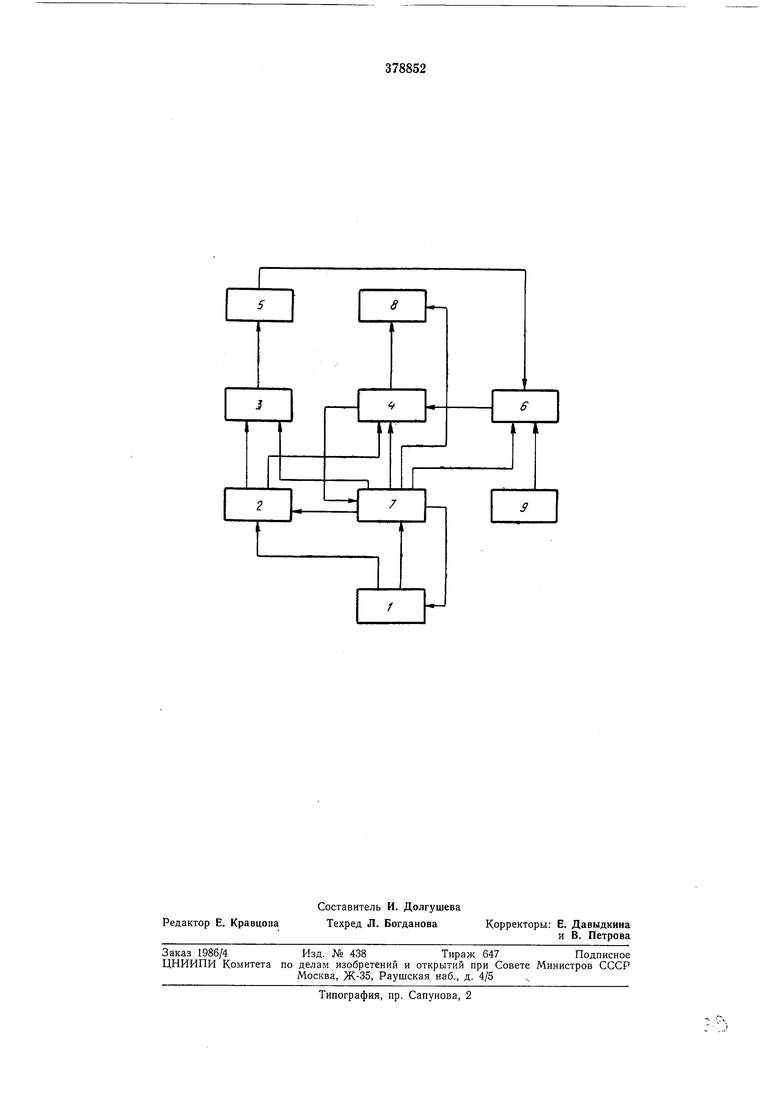

Изобретение касается вычислительной техники. Известно устройство для автоматического нахождения неисправностей в электронных схемах, содержащее регистр ввода, регистр инструкций, регистр командных усилителей, сравнивающее устройство. Однако такое устройство не позволяет контролировать величины параметров логических элементов относительно заданных допусков. Целью изобретения является расширение функциональных возможностей устройства. Для этого предложенное устройство дополнительно содержит преобразователь, блок эталонов и компаратор-преобразователь, второй выход регистра задания соединен со входом преобразователя-коммутатора, выход которого соединен со входом анализируемой схемы, выход анализируемой схемы соединен со входом компаратора-преобразователя, второй вход которой соединен с выходом блока эталонов, а выход - со входом блока сравнения, второй вход преобразователя и третий вход компаратора-преобразователя соединены с соответствующими выходами блока управления. На чертеже приведена блок-схема предложенного устройства. Устройство .содержит блок /, регистр 2 задания, преобразователь 3, блок 4 сравнения, анализируемую схему 5, компаратор-прео браизователь 6, блок 7 управления, блок 8 индикации и блок 9 эталонов. Блок ввода / предназначен для введения информации, необходимой для анализа схем. Регистр 2 задания предназначен для хранения и выдачи на преобразователь 3 и блок 4 сравнения необходимой информации в дискретной форме для анализа схем. Преобразователь 3 предназначен для преобразования информации, поступающей с регистра 2 задания в дискретной форме и выдачи ее в виде сигналов в аналоговой форме на анализируемую схему, а также для коммутации входов анализирземого устройства, Блок 4 сравнения предназначен для сравнения сигналов в дискретной форме, поступающих с компаратора-преобразователя (в результате анализа схемы) и регистра 2 задания, а также выдачи результата сравнения в блок 7 управления и блок 8 индикации. Компаратор-преобразователь 6 предназначен для анализа параметров сигналов в аналоговой форме, поступающнх от схемы ЭЦВ.Н, путем сравнения их с эталонами верхних и нижних пределов параметров, поступающих с блока 9 эталонов, а также преобразования сигналов аналоговой формы, поступающих в результате анализа схемы, в сигналы дискретной формы, выдаваемые в блок 4 сравнения. Блок 7 управления вырабатывает уп3равляющие сигналы и синхронизирует работу всего устройства в зависимости от сигналов, поступающих на него с блока 1 ввода и блока 4 сравнения. Блок 8 индикации предназначей для индикации результата сравнения. Блок 9 эталонов предназначен для формирования верхних и нижних пределов параметров в аналоговой форме в соответствии с требованиями, предъявляемыми к параметрам анализируемой схемы 5, и выдачи их в блокЮ компаратора-преобразователя 6. Регистр 2 задания соединен с блоком / ввода, преобразователем 3 и блоком 4 сравнения. Блок 4 сравнения связан с блоком 5 ивдикации и компаратором-преобразователем 6.15 Компаратор-преобразователь 6 своим входами подключен к контактам анализируемой схемы 5. Блок 7 управления связан с блоком / ввода, регистром 2 задания, преобразователем 3, блоком 4 сравнения, компаратором-преобразо-20 вателем 6, блоком 8 индикации. Это позволяет достигнуть логичес;:ой гибкости, возможности контроля параметров логических схем по заданным пределам и ввести программируемый переход в режим само-25 контроля. Программа проверки схемы, в качестве носителя которой выбрана перфолента, начинается с кода «начало программы. Каждая программа состоит из подпрограмм по /г+130 строке, где п - максимальное количество контактов анализируемой схемы. Номер строки каждой подпрограммы соответствует номеру контакта анализируемой схемы, а информация, записанная в одной стро-35 ке, соответствует коду того сигнала с определенными параметрами, который необходимо подать на один контакт либо получить с одного контакта анализируемой схемы. Незадействованные контакты кодируются кодом «выклю-40 чено. В ковце последней подпрограммы записывается код «конец проверки. Информация одной подпрограммы считывается блоком 1 ввода с перфоленты в регистр 2 задания. В каждом разряде регистра 2 за-45 дания формируется кодовая информация, задающая сигнал с необходимыми параметрами no каждому контакту анализируемой схемы 5. Содержимое регистра 2 задания по команде из блока 7 управления, вырабатываемой по50 концу считывания подпрограммы, преобразуется в аналоговую форму и коммутируется на анализируемую схему 5 преобразователемкоммутатором 3 одновременно на все контакты. Эта же информация с регистра 2 задания55 поступает в блок 4 сравнения. Блок 7 управления осуществляет последовательный опрос анализируемой схемы 5 по всем контактам. Сигнал от контакта в аналоговой форме поступает в компаратор-преобразователь б 60 и анализируется по величине сравнения с эта 4 лонами верхнего и нижнего пределов анализируемого параметра. Результат анализа преобразуется в дискретную форму и по команДе блока 7 управления подается на блок г сравнения, где сравнивается с сигналами. поступающими с регистра 2 задания. Результат сравнения подается в блок 7 управления и блок 8 индикации. Если анализируемая схема по данной подпрограмме работает нормально, то блок 7 управления вырабатывает сигнал для считывания следующей подпрограммы, и цикл работы повторяется, По окончании всей программы проверки блок 7 управления вырабатывает сигнал о годности анализируемой схемы 5, который поступает в блок 8 индикации и высвечивает табло «Годен. В случае несоответствия логического функционирования либо заданных параметров проверяемой схемы 5 в соответствии с программой, блок 7 управления вырабатывает сигнал. останавливающий дальнейшую проверку схемы. Этот сигнал поступает в блок 8 индикации, который высвечивает табло «Брак, а также указывает адрес неисправности анализируемой схемы. Это позволяет включить в устройство самоконтроль, задаваемый специальной программой. При необходимости дальнейшая проверка анализируемой схемы осуществляется ручным запуском устройства, Предмет изобретения Устройство для контроля схем цифровых вычислительных машин, содержащее анализируемую схему, блок ввода, выход которого соединен со входом регистра задания и блока управления, второй вход которого соединен с выходом блока сравнения, второй выход блока сравнения соединен со входом блока индикации, выходы блока управления соединены соответственно со входами регистра задания, блока ввода, блока сравнения и блока индикации, выход регистра задания соединен со вторым входом блока сравнения, отличающееся тем, что, с целью расширения функциональных возможностей, оно дополнительно содержит нреобразователь, блок эталонов и компаратор-преобразователь, второй выход регистра задания соединен со входом преобразователя-коммутатора, выход которого соединен со входом анализируемой схемы, выход анализируемой схемы соединен со входом компаратора-нреобразователя, второй вход которой соединен с выходом блока эталонов, а выход - со входом блока сравнения, второй вход преобразователя и третий вход компаратора-преобразователя соединены с соответствующими выхода.ми блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1977 |

|

SU693384A2 |

| Устройство контроля электромагнитных параметров гибкого магнитного диска | 1988 |

|

SU1578627A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

Даты

1973-01-01—Публикация