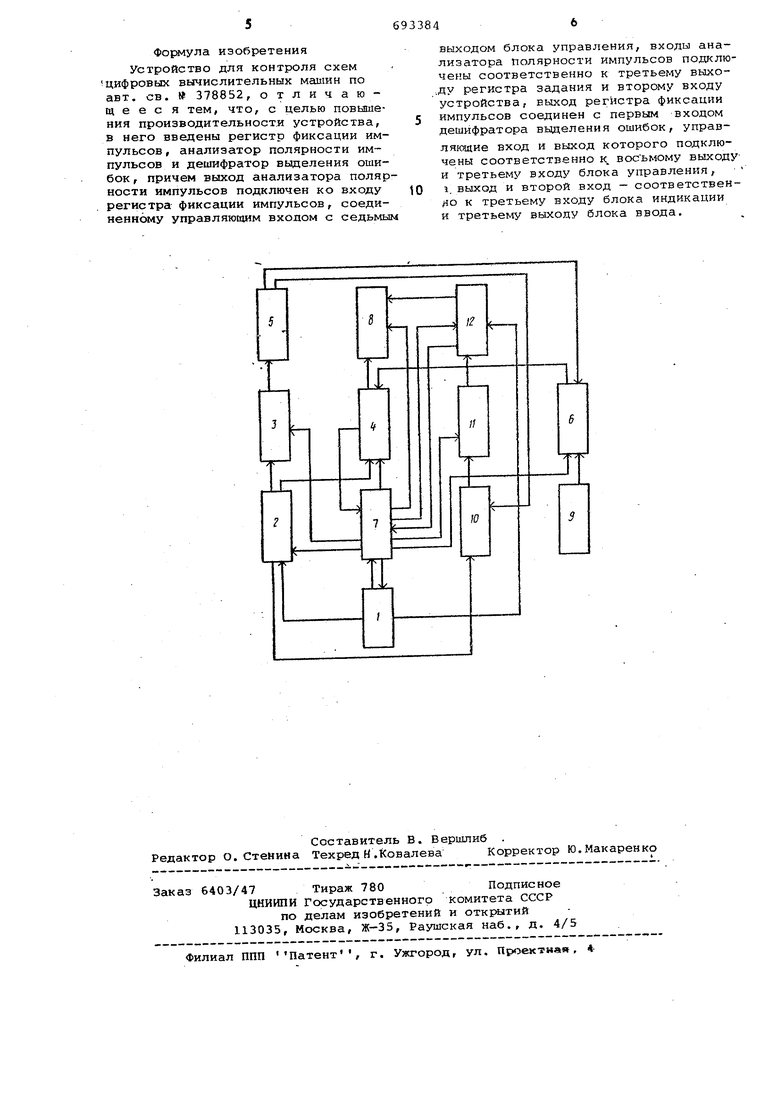

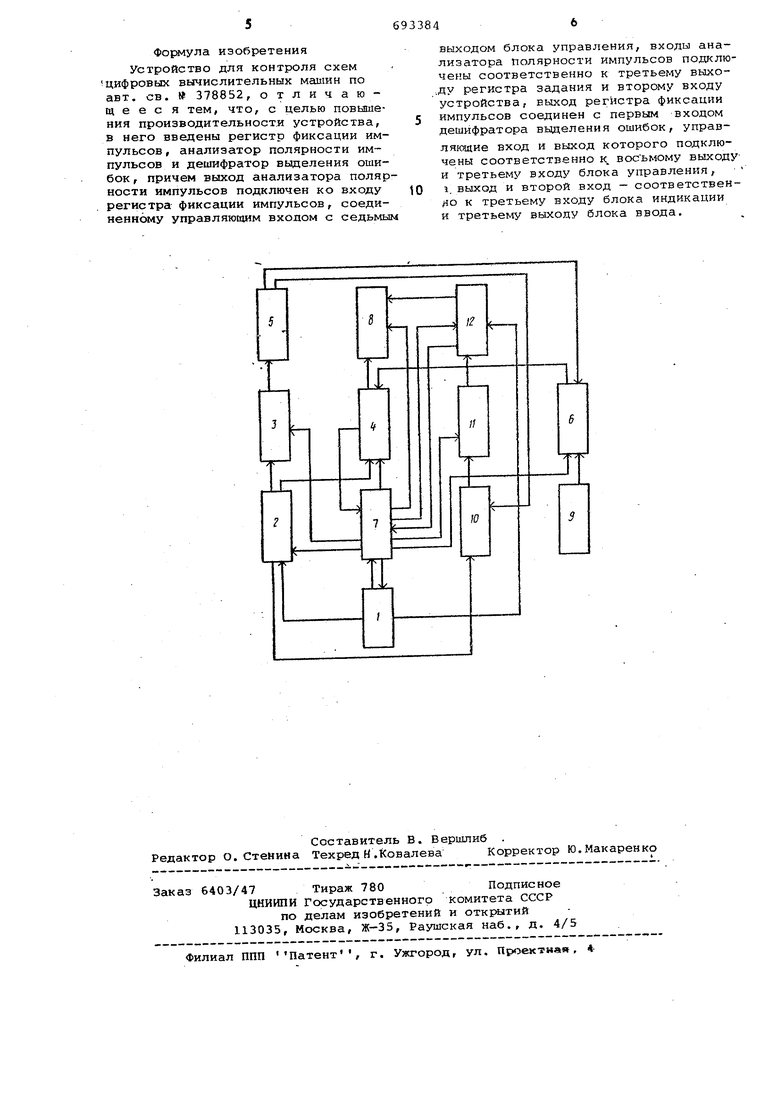

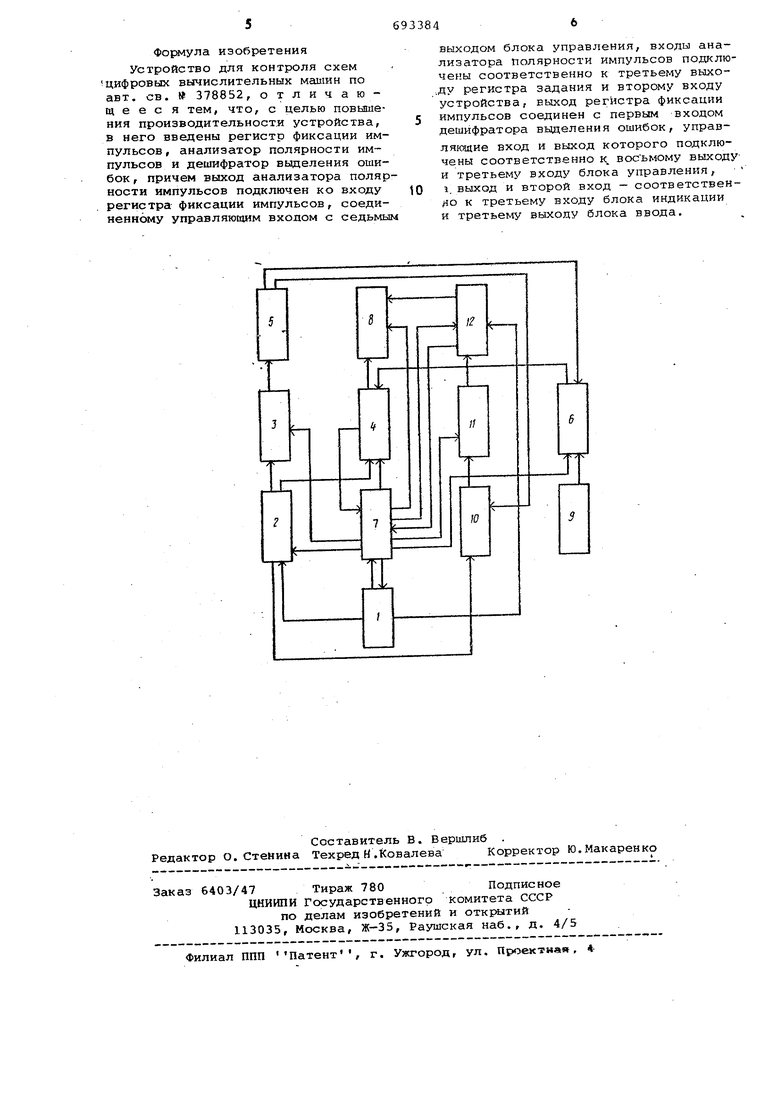

Это достигается тем, что в устройртво для контроля схем цифровых вы- .числительных мэшин по авт. св. 378852 введены регистр фиксации импульсов, анализатор полярности импульсов и дешифратор выделения ошибок причем выход анализатора полярности Ймпульйов Подключен ко входу регистра фиксации импул сов, соединенному управляющим входом с седьмым выходом 6лЬка У11равления, входы анализатора полярности импульсов подключены соот llraTBlkWo к третьему въкоду регистра задания и второму.входу устройства, выход регистра фиксации импульсов со динен с первым входом дешифраторавыд .ления ошибок,управляющие вход и выхо которого подключены соответственно к восьмому выходу и третьему входу блока управления, а выход и второй вход - соответственно к третьему вхо ду блока индикации и третьему выходу блока ввода. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит блок ввода 1, регистр 2 задания, преобразователь 3, блок 4 сравнения, контролируемую схему Ь, компаратор 6, блок 7 управления, блок 8 индикации, блок 9.эталонов, анализатор 10 поляр ности импульсов, регистр И фиксации импульсов и дешифратор 12 выделения ошибок.. Блок 1 ввода предназначен для вве дения информации, необходимЬй дЛя анализа-схемы. Регистр 2 задания ГЙредназначён для хранёния и выдачи на преобразователь 3, блок 4 и анализатор 10 необходимой информации S дискретной форме. Преобразователь 3 пр дНа значен для преобразования ин формации поступающей с регистра 2 г задания в дискретной форме и выдачи ее в виде сигналов в аналоговой форме .на контролируетлую схему 5, а такж для коммутации входов анализируемого устройства. Блок 4 сравнения предназначен для сравнения сигналов в дискретной форме, поступающих 6 компаратора б и регистра 2 задания, а.также выдачи реэультат а сравнения в блок 7 управления и блок 8 индикации. Компаратор 6 предназначен для ана лиза параметров сигналов в аналоговой , поступа1ющих от контролируемой схемы, путем сравнения их с эталон вtpxних и нижних пределов поступающих с блока 9 эталонов, а также преобразования сигналов аналог вой формы, поступающих в результате анализа схемы 5, в сигналы дискретной формы, вьиаваемые в блок 4 сравнения,, . Блок 7 управления вырабатЙсваГет уп равляющие сигналы и синхронизирует. работу всего устройства в зависимое ти от сигналов,поступающих на него с блока 1 ввода, блока 4 сравнения и дешифратора 12 вьщеления ошибок. Блок 8 индикации предназначен для индикации результата сравнения. Блок 9 эталонов предназначен для формирования верхних и нижних пределов параметров в аналоговой форМе в соответствии с требованиями, предъявлявшими к параметрам схемы 5 и выдачи их в блок компаратора 6.. Анализатор 10 полярности импульсов в соответствии с сигналами регистра 2 задания и импульсами, приходящими с схемы 5, вырабатывает импульсы одной полярности, поступающие на регистр 11 фиксации импульсов, который перед приходом ожидаемых импульсов со схемы 5 устанавливается в .нулевое состояние сигналом с блока 7 управления, а затем принимает импульсы с выходов схемы 5 и хранит эту информацию до последующего сброса. . Дешифратор 12 по разрешению, формируемому в блока 1 ввода, и временному такту, приходящему с блока 7 управления, опрашивает состояние нужного вь1хода регистра 11 фиксации им-пульсов. Результат сравнения поступает в блок 7 управления и в блок 8 иидикации. ч Устройство работает следующим образом. Программа с программоносителя ввОдит.ся в блок. 1 ввода и далее информации поступает в регистр 2 задания и. в бло1 7 управления. Выходная информация с регистра 2 задания через преобразователь 3 подается на контролируемую схему 5. Сигналы с выходов cxeNttJ 5 поступают на компаратор 6. Сюда же поступает эталонный сигнал с блока 9 эталонов. Выходная информация . компаратора 6 передается .в блок 4 сравнения. Результат сравнения выводится в блок 8 индикации. Выходной сигнал с регистра 2 задания вводится на один из входов анализа,тора 10 и определяет -полярность приходящего с контролируемой схемы 5 импульса. Импульс с выхода этого блока фиксируется в регистре 11 фиксации импульсов, В случае отсутствия записи ймпульса в ожидаемом разряде регистра 11 в дешифраторе 12 происходит выделение обнаруженной ошибки и вьздача координаты ошибки в блок 8 индикации . Таким образом, устройство позволяет исключить ручные операции при контроле схем формирователей импульсов , генераторов.серий импульсов, составляющих около 20% всех контролируемых схем U3M, что повьоиает проиэ водительность устройства, . Формула изобретения Устройство для контроля схем цифровых вьмислительных машин по авт. св. 378852, отличающееся тем, что, с целью повышения производительности устройства, .в него введены регистр фиксации импульсов, анализатор пблярности импульсов и дешифратор вьвделения ошибок, причем выход анализатора полярности импульсов подключен ко входу регистра фиксации импульсов, соединеннсмчу управляющим входом с седьмым

выходом блока управления, входы анализатора полярности импульсов подключены соответственно к третьему выходу регистра задания и второму входу устройства, выход perificTpa фиксации импульсов соединен с первым входом дешифратора вьеделения ошибок, управляющие вход и выход которого подключены соответственно к;, восьмому выходуи третьему входу блока управления, э. выход и второй вход - соответствен 10 к третьему входу блока индикации и третьему выходу блока ввода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU796860A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Генератор кодового слова | 1989 |

|

SU1755269A1 |

| Устройство для обучения операторов | 1987 |

|

SU1564675A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

Авторы

Даты

1979-10-25—Публикация

1977-06-21—Подача