Изобретение откосится к вычислительной технике и может быть использовано во всех отраслях народного хозяйства для поиска неисправностей п логических схемах, построенных на дискретных элементах, полуироводникавых гибридных и интегральных . Известны устройства для программного тестового контроля логических схем, содержащие блоки входных сигналов, эталонных выходных сигналов, сравнения, ввода данных, коммутании, индикацин неисправностей, управления 1, 2. Недостатки известных аналогов сводятся к малой глубине поиска места неисправностей, что определяется ограниченными диагностическими возможностями тестовых программ. Наиболее близким решением к даиному изобретению является устройство для контроля логических схем, содержащее электромеханический щун, подключенный к контролиргуемым схемам, блок ввода, выходы которого соединены соответственно с первыми входамн первого регистра задания и блока управления, второй вход которого соединен с выходом первой схемы логического сравнения, а выходы блока управления соединены со входаМН коммутатора-формирователя, блока индикации, блока ввода, первого комиаратораформирователя и вторым входом нервого регистра задаНИЯ, выход которого соединен с первым входом первой схемы логического сравнення н через коммутатор-формирователь с контролнруемыми схемами, нодключеннымн к первому входу первого комиаратора-формирователя, выход и второй вход которого соед1 нены соответственно со вторым входом нервой схемы логического сравнения и выходом блока задания эталонных сигналов 3. Диагиостг1ка неисправностей в этом устройстве производится путем сравнення Д1 скретных сигналов, поступающих с выхода компаратора-формирователя с сигналами, поступающими с регистра задания. Результат сравнення нодается в блок управления и в блок индикации. Если блок сравнения выдает сигнал несоответствия, то в блоке индикации на табло высвечивается наднись «Не годен и адрес неисправного элемента. Ввиду несовершенства методов н алгоритмов в существующих устройствах не удается локалнзовать место неисиравностн до отдельного съемного элемента. Поэтому существующие устройства диагностики позволяют выделить и отобразнть вмеето конкрет юго ненсиравного элемента ЛИШЬ группу подозреваемых элементов. Поиск конкретного иеисиравного элемента в дальнейшем выполняется оператором вручную по ирннципнальиым схемам н таблнцам

неисправностей с применением донолннтельлого оборудования.

Целью настоящего изобретения является повышение достоверности контроля ненснравностей, а также новышение быстродейетвия устройства.

Поставленная цель достигается тем. что в устройство вводятся второй регнстр задания, переключатель, вторая схема логического сравпенпя и второй комнаратор-формирователь, входы которого подключены к электромехаинческому щуну п к выходам блока задання эталонных сигналов н блока уиравлеиня, а выходы-к первому входу второй схемы логического сравнения, второй вход которой соединен с выходом второго регнстра задания, входы которого нодключены соответственно к выходам блока ввода, блока унравления, входы которого соедпнены соответственно с выходо.м второй схемы логического еравнення и иерскл 0чателем.

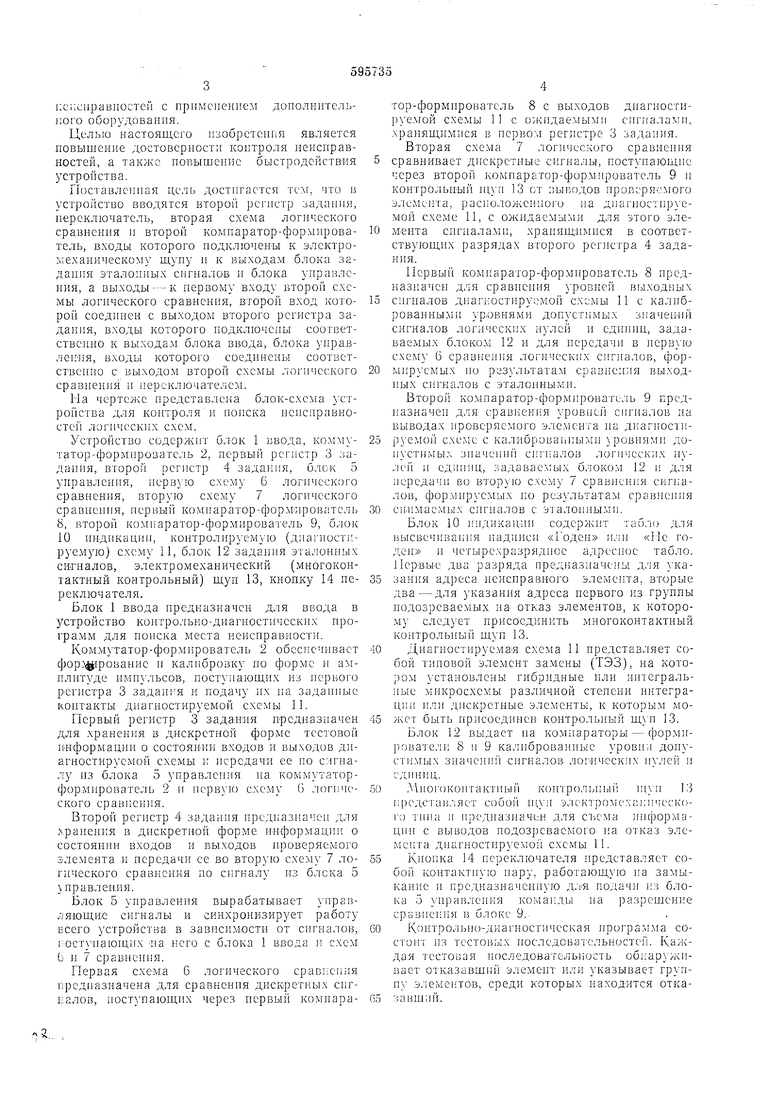

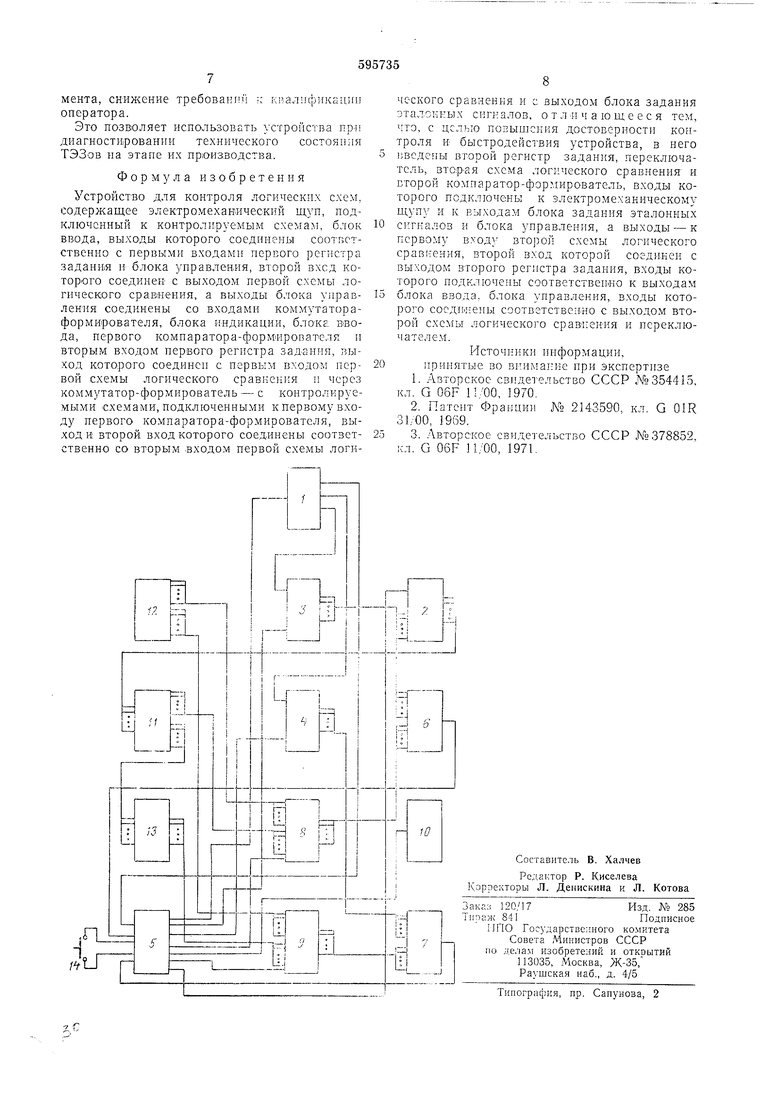

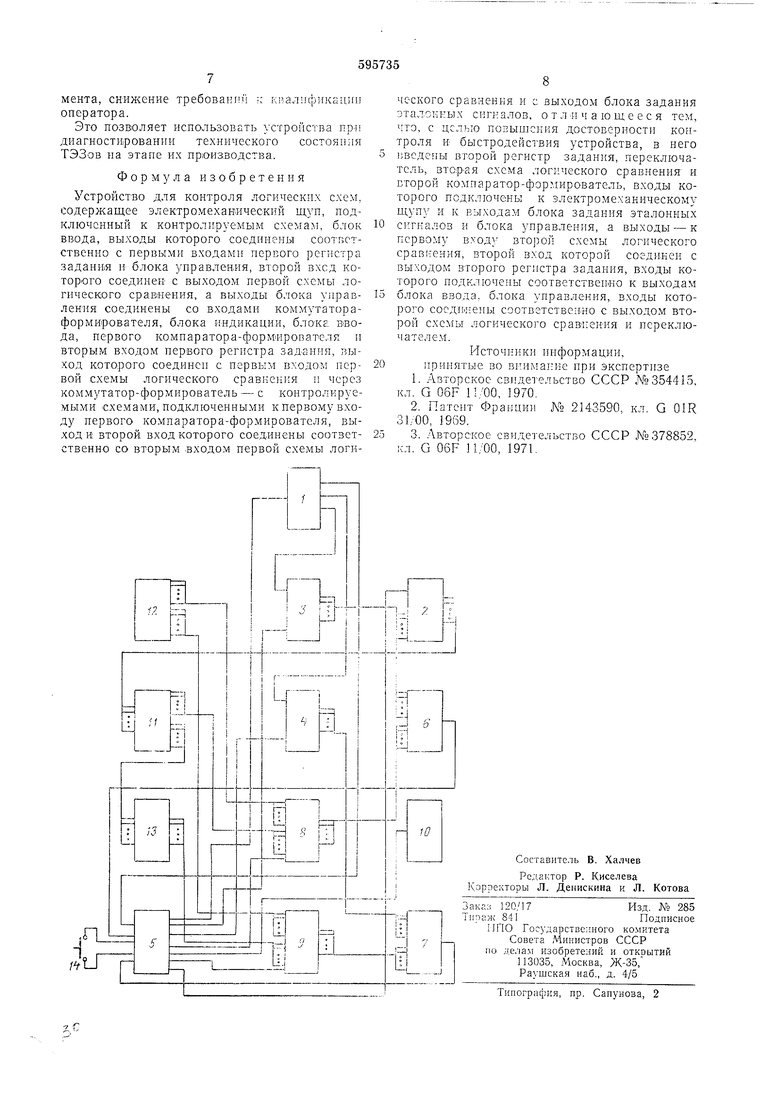

Ыа чертеже представлена блок-схема устройства для контроля н поиска неисправностей логических схем.

Устройство содержит блок 1 ввода, комм -татор-формпрователь 2, первый регистр 3 задапия, второй регистр 4 задапня, блок 5 управлення, нсрвую схему 6 логического сравпенпя, вторую схему 7 логического сравпеимя, первьп комнаратор-форм:прователь 8, второй компаратор-формирователь 9, блок 10 индпкацпп, контролируемую (диагиостнруемую) схему И, блок 12 задапия эталоппых сигналов, электромеханнческий (многоконтактный контрольный) щуп 13, кнопку 14 переключателя.

Блок 1 ввода нредназначен для ввода в З стройство контрольно-дпагпоетпческнх программ для поиска места неисправности.

Коммутатор-формирователь 2 обеспечнвает фор: фовапне п калибровку ио форме и амплптуде пмпульеов, поетуиающпх из иервого Регистра 3 задания н нодачу их па задаииые контакты диагностируемой схемы 11.

Первый регнетр 3 задания нредназиачен для хранения в дпскрстпой форме тестовой 1и-1формации о состоянИИ входов и выходов диагностируемой схемы и исрсдачН ее но сигналу из блока 5 управлепия на коммутаторформнрователь 2 и первую схему 6 логического сравнения.

Второй регпетр 4 задания нредназпачеп для хранения в дпскретпой форме ппформации о состоянии входов н выходов нроверяег1Юго элемента и передачи ее во вторую ехему 7 логического сравнения но сигналу из блска 5 нравленпя.

Блок 5 уиравления вырабатывает управляющие сигналы и синхронизирует работу всего устройства в зависимости от сигналов, гюстуиающих На него с блока 1 ввода и схем 6 и 7 сравпеиия.

Первая схема 6 логического сравпеиия предпазначена для сравнения дискретных сигналов, иоступающпх через первый колтнаратор-формпрователь 8 с выходов дпагностируемой схемы 11 с о кидаемыми сигналами, хранящимися в первом регистре 3 задания.

Вторая схема 7 логического сравнеиия сравнивает дискретные сигналы, поступающпе через второй компаратор-формирователь 9 и контрольный П1,уи 13 от )дов проверяемого элемеита, расноложенпо1о па диагпостпр емой схеме И, с ожндаемы.ми для этого элем ента сигналами, хранящимися в соответствующих разрядах второго регнстра 4 задания.

Первый комнаратор-формнрователь 8 иредпазначеп для сравнеппя ровней выходных

сигналов диагностнруемой схемы 11 с калиброванными ур,овнями допустимых зиачепчи сигналов логичееких нулей п сдпииц, задаваемых блоком 12 п для передачи в первую схему 6 сраБиеиня логических сигналов, формируемых ио результатам еравнения выходных сигналов с эталонными.

Второй компаратор-формирователь 9 предназначен для сравнен1 Я уровней сигиалов на выводах ироверяемого элемента на д ;аг11остир е.мой схеме с калнброва11пымн уровнями до 1устимых зиачеиий сигналов логичееких п сЛей н единиц, задаваелгых блоком 12 и для иередачи во вторук; схему 7 cpaBHCHJiJi сигиалов, формнруемых но результатам еравнеиия

си.нмаемых сигналов с эталонными.

Блок 10 1;идикацнп содержит тггбло для 15ысвечнваиия надписи «Годен илн «lie го;1,ен п четырехразрядное адресное табло. ПерВЫе два разряда предпазпачены д.чя указапня адреса пеисправпого элемепта, вторые два - для указання адреса нервого нз группы подозреваемых иа отказ элементов, к которому следует присоединить многоконтактный контрольный щуп 13.

Дпагпостируел1ая схема 11 представляет собой типовой элемент замены (ТЭЗ), на котором установлены гибридные плн интегральные мнкросхемы различной степени интеграции или диекретпые элементы, к которым может быть присоедипен контрольный щуп 13.

Блок 12 выдает па компараторы-формирователи 8 и 9 калпброваииые уровпи допустимых зиаче11Н1 1 сигналов логических in ieii п едишщ.

Миогокоитактиый коитролыпл niyn 13 и|зедетавляет собой Пуи .leFsTpoMexainiiiecKoго типа и и гедпаз 1ачен для ст/ома innpopMaцпп с выводов подоз1)сваемого па отказ элемента диагпостпруемо схемы 11.

Киопка 14 переключателя предетавляет еобой контактную пару, работающую на замыкаиие н предназначенную длЯ нодачи из блока 5 уирав.теиия команды иа 5азрешен1:е сравпения в блоке 9.Контрольпо-дпагностичеекая нрограмма соСТ01Г1 из тестовых последовательностей. Каждая тестовая Г1оследовательность обиаружпвает отказавшпй элемеПТ или указывает группу элементов, среди которых находится отказавший.

Тестовая последователъность включает информацию об уровнях сигналов на входах и выходах диагностируемой схемы, о распределении контактов на входные и выходные, о допустимых уровнях калиброванных сигналов и об адресе проверяемого элемента. Если последовательность позволяет указать лишь груину подозреваемых элементов, то в программу включаются адреса подозреваемых на отказ элементов , расположенные в определенном порядке, а также информация о логических состояниях на их выводах.

Устройство работает следующим образом.

Из блока 1 ввода информация о логических состояниях входов и выходов диагностируемой схемы 11 записывается в первый регистр 3 задания. В коммутатор-формирователь 2 через блок 5 управления записывается информация о разделении контактов диагностируемой схемы 11 на входные и выходные, а также об уровнях сигналов, выдаваемых на вход схемы. В FicpBbm компаратор-формирователь 8 через блок 5 управления заииеываетея информация о выборе эталонов верхнего п аижпего пределов анализируемого параметра.

Если тестовая последовательность позволяет локализовать неисправность до элемента, в блок 10 индикации записывается помер выявляемого неисправного элемента. Если же тестовая последовательность позволяет выявить только группу элементов, один пз которых является неисправным, то в блок 10 индикации записываются номера подозреваемых на отказ элементов в порядке, в котором следует производить их проверку, а во второй регистр 4 задания заипсывается информация о логических состояниях выводов этих элементов в том же иорядке.

Во второй комиаратор-форм.прователь 9 через блок 5 управления записывается информация о выборе эталонов верхпего п нижнего пределов анализируемого параметра.

Содержание первого регистра 3 задания по команде из блока 5 управления, вырабатываемой по еигналу из блока 1 ввода, формируется в виде сигиалов, калиброваииых по форме и амплитуде, п коммутируется коммутаторомформирователем 2 одновременно па все контакты диагиостпруемой схемы 11. Эта же информация с первого регистра 3 задания поступЯет на первую схему 6 логического сравнения.

Выходные сигналы диагностируемой схемы иостуиают в первый кoмпapaтop-фop iпpoвaтель 8 для сравнепня с калиброванными уровнями допустимых значений нулей п единиц. При этом схема вырабатывает сигнал, разрешающий еравнение в блоке 6, еели реальныс ешпалы лежат в пределах, определени1ых эталонными зиачениями из блока 12.

Логические сигиалы, сформированные но форме и амплитуде, по команде из блска 5 поступают на первую схему 6 логического сравнения, где сравниваются с сигналами, пост}Ч1ающимп с первого регистоа 3 за.ання.

Результат срав} снпя заводится в блок 5 управления. Если д:.1аг1 остпруемая схема по данно тестовой последовательностп работает нормально, блок 5 управлення вырабатывает

сигнал для счптывання следующей тестовой последовательностп. Цикл повторяетея до обнаружения неисправного элемента пли до окончания программы. В конце программы блок 5 }правленпя по спгналу пз блока 1 BiBOда выдает в блок 10 иидикацпи команду на высвечивание табло «Годен.

В случае выдачи первой схемой 6 логпчеекого сравнения сигнала несовпадення, блок о управления вырабатывает сигнал, по которому в первых двух разрядах блока 10 ипдпкацип высвечивается адрес зепсиравного элемента, если теетовая иоеледовательность позволяет его выявить. Высвечпван1 е адреса иеиснравного элемента означает конец нроверкн.

Если диагностическая способность тестовой последовательности недостаточна для указанпя адреса конкретного отказавшего элемента, 10 во вгорых ,-i, разрядах блока 10 пндикацг;П rio команде пз блока 5 хчфавленпя высвечивается адрес первого из групны нодозрсвае. на отказ з.чементов. Оператор iipHсоединяет контрольный щуп 13 к указанному элементу, и, убедившись в правильности иодключенпя, пажатпом на кнопку 14 переключателя, осуществляет подачу из блока 5 управлен 1я команды на разрешение сравнения в блоке 9 выходных спгналов проверяемого элемента с эталонны Ml значениями уровней логпческ1гх пулей п едннкц.

Блок 5 праплсн.1;я вырабатывает так;1-:е комапду на передачу результатов апалгза пз второго компаратора-формирователя 9 п частп содержимого второго pei-петра 4 задашш, отпосяще 1ся к провсряе. злсменту. па вторую ехему 7 логического сраш.сппя. Результат сравнения передается в блок 5 управления.

Еелп проверяемый элеме)1т пегеправен, то блок 5 управления вырабатывает команду на высвечивапие в первых двух разрядах блока 10 пндпкацпп адреса этого элемс1гга. а uj вторых двух разрядах происходит гашсппс адрееа этого же эле гепта. Проверка )ia этом закопчеНа.

Еелп проверяемы) элсмегы исправен, то блок 5 управления вырабатывает комапду. по которой во вторых двух разрядах блока 10

пндпкацпн высвечпваетея адрес следуклдего элемепта, к котором необходимо 1р1 еосдиппть коптрольпый щуп 13. Цпкл повторяетея до тех пор, пока lic будет o6n,py;-i;en отказагпшй элемепт пз гру|;пы подозре15ас: 1ых па отказ.

Такпм образом, предлагаемое уетр.;йство для коптроля логических cxeN обеспечивает поиек меета 11епсправпоетп до отдельного еъемпого элемепта, еокраще: Г1е времени fia

локализацию копкрет1юго отказавшего эле

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Система для контроля и диагностики цифровых узлов | 1980 |

|

SU911531A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| ПРОГРАММНО-АППАРАТНЫЙ СТЕНД ДЛЯ ДИАГНОСТИКИ ЦИФРОВЫХ И МИКРОПРОЦЕССОРНЫХ БЛОКОВ | 2006 |

|

RU2324967C1 |

| Устройство для диагностики логических узлов | 1980 |

|

SU892445A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЛЕКС КОНТРОЛЯ И ДИАГНОСТИКИ (ВАРИАНТЫ) | 2003 |

|

RU2257604C2 |

Авторы

Даты

1978-02-28—Публикация

1976-01-05—Подача