1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля запомииающих матриц на тонких магнитных цилиндрических пленках, содержащее блок формирователей разрядных токов, выход которого подключен к блоку коммутации разрядных обмоток матрицы, а вход - к блоку унравления, блок формирователей числовых токов, одни выход которого подключен к первому входу блока коммутации числовых входов матрицы, и усилитель воспроизведения.

Недостатком известного устройства является однотактная проверка запоминающих элементов матрицы, что сиижает надежность работы устройства и точность контроля.

Описываемое устройство отличается от известного тем, что оно содержит блок анализа результатов многотактиой проверки запоминающих элемеитов матрицы, первый вход которого подключен к выходу усилителя воснроизведення, второй вход - к другому выходу блока формирователей числовых токов, установочный вход - к блоку управления, а выход- ко второму входу блока ком у1утацни числовых входов матрицы.

Это позволяет повысить надежность устройства и точность контроля.

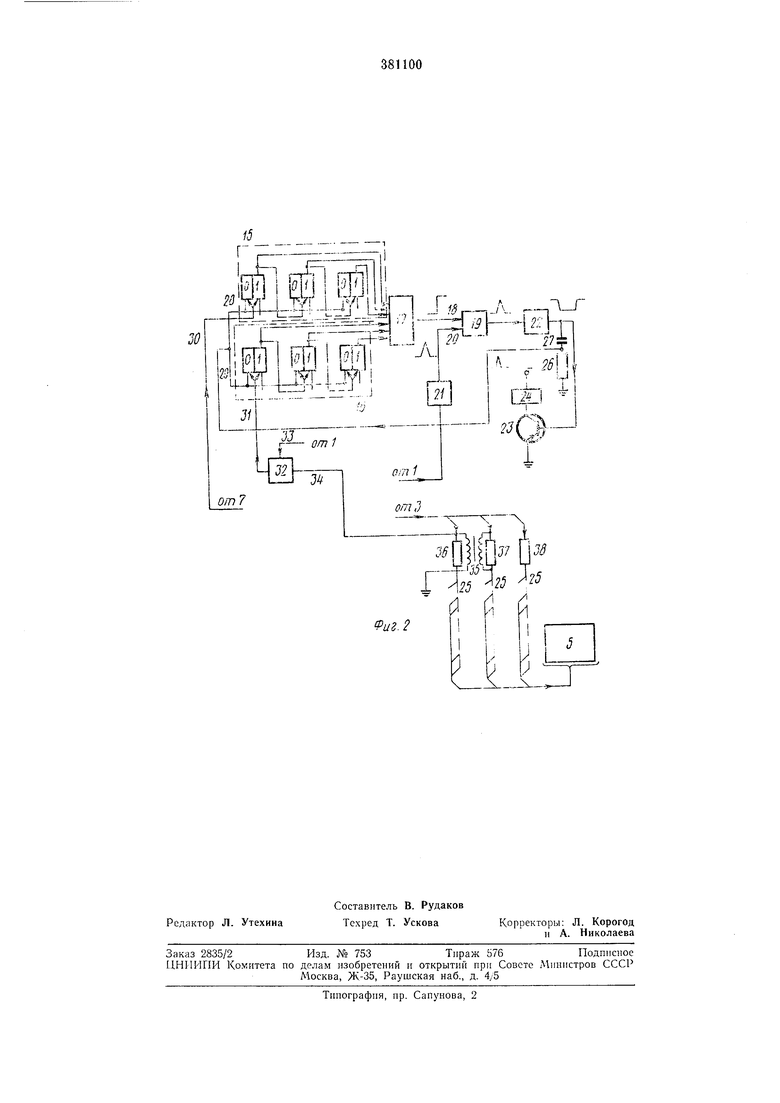

На фиг. 1 изображена блок-схема устройства для контроля запоминающих матриц на

тонких магнитных цилиндрических пленках, а на фиг. 2 - вариант схемы блока аналнза результатов многотактной проверки запоминающих элементов матрицы.

Устройство содержит блок унравлення /, блок формнрователей разрядных токов 2, блок формирователей числовых токов 3, блок коммутации числовых входов матрицы 4, нроверяемую матрицу 5, блок коммутацнн разрядных об.моток 6, уснлитель воснроизведення (УВ) 7 и блок 8 анализа результатов миоготактной нроверкн запоминающих элеме 1тов матрицы.

Нри этом первый вход 9 блока 8 подключен

к выходу УВ 7, второй вход 10 - к одному нз выходов блока формирователей числовых токов 3, установочный вход // - к блоку управления У, а выход 12 - к одному из входов 13 блока коммутации числовых входов матрнцы

4, другой вход 14 которого подсоединен к блоку 3 .

Блок анализа результатов многотактной проверки запоминающих элементов матрнцы содержит двоичные счетчики 15 и 16, выходы

которых подключены к схеме сравнения 17. Выход последней подключен к одному из входов 18 схемы «И 19, другой вход 20 которой подключеи к схеме задержки 21, а выход - к одиовибратору 22. Выход одновибратора 22

подключен к ключу на транзнсторе 23, в коллектор.ную цепь которого включена шагового искателя (ШИ) 24. Контакты 25 ШИ включены в цепи числовых входов матрицы 5. Выход одновибратора 22 подключен через дифференцирующую цепочку, состоящую из резистора 26 и конденсатора 27, к установочным входам 28 и 29 счетчиков 15 и 16 соответственно.

Счетный вход 30 счетчика 15 подключен к выходу УВ 7, а счетный вход 31 счетчика 16 - к выходу схемы «И 32, один из входов 33 которой подсоединен к блоку управления 1, а другой 34 - к трансформатору 35, подключенному к одному из выходов блока 3. На выходах блока 3 включены резисторы 36-38.

Устройство работает следующим образом.

После выборки адреса с запоминающей ячейки с каждым тактом обращения считывается импульс, который усиливается УВ 7, имеющим регулируемый порог срабатывания. Усиленный и формированный сигнал с выхода УВ 7 поступает на счетный вход 30 счетчика 15. Одновременно со вторичной обмотки трансформатора 35, возбужденного током /сч, поступает импульс на вход 34 схемы «И 32. На другой вход 33 этой схемы подается импульс от блока управления /. Таким образом, если данный адрес выбран, то с выхода схемы «И 32 в такте «чтение поступает имнульс на вход 31 счетчика 16. Выход схемы сравнения 17 управляет потенциальным входом 18 схемы «И 19. На другой вход 20 этой схемы блока управления поступает задержанный на время т схемой задержки 21 имнульс. Если состояния счетчиков 15 и 16 одинаковы, что означает наличие считанного импульса на выходе УВ 7 в каждом такте считывания, то па выходе схемы «Н 19 появляется имнульс, запускающий одновибратор 22. Если же состояния счетчиков 15 и 16 не совпадают, что означает отсутствие импульсов на выходе УВ 7 в каком-либо такте чтения, то запуска одновибратора 22 не происходит. Отрицательный перенад с выхода одновибратора 22 подается на базу транзистора 23. Транзистор открывается, обмотка ШИ 24 обтекается током и нроисходит сдвиг ротора ШИ 24 на другую ламель. Наличие одновибратора 22 позволяет установить необходимую частоту срабатывания ШИ 24. После сдвига ротора ШИ 24 на новую ламель (адрес) происходит автоматическая установка в «О счетчиков 15 и 16, после чего цикл проверки повторяется. Импульс устаповки в «О вырабатывается па заднем фронте перепада па выходе одповибратора 22.

Нредмет изобретения

Устройство для контроля запоминающих матриц на топких магпитпых цилипдрических пленках, содержащее блок формирователей разрядных токов, выход которого нодключен к блоку коммутации разрядных обмоток матрицы, а вход - к блоку управления, блок формирователей числовых токов, один выход которого подключен к первому входу блока коммутации числовых входов матрицы, усилитель воспроизведения, отличающееся тем, что,

с целью повышепия надежности устройства и точности ко1ггроля, оно содержит блок анализа результатов многотактной проверки запомпнаюпитх элементов матрицы, первый вход которого подключеп к выходу усилителя воспроизведения, второй вход - к другому выходу блока формирователей числовых токов, установочный вход-к блоку управления, а выход-ко второму входу блока коммутации числовых входов матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СТЕРЖНЕЙ, ПОКРЫТЫХ ФЕРРОМАГНИТНОЙ ПЛЕНКОЙ | 1973 |

|

SU385320A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ЦИЛИНДРИЧЕСКИХ МАГНИТНЫХ ПЛЕНКАХ | 1968 |

|

SU231224A1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Цифровое устройство для управления вентильным преобразователем | 1981 |

|

SU1080243A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

| Устройство для подавления помех | 1988 |

|

SU1628193A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU314233A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

Д. --.4 5

Jm Й i FFl

14 1 ж wi

i:fct±r-i--L:;y dfT - -i-- - -1 . i ..-L7i-...J , rir- - - I-VVJ

I i№ |J i 5i

J/

IJ

л

/7 ,

17

0/777

Г

- - I

Л

U , 4 i

РЛТ / i/T/J

.n||. nri/ % J

.V

Авторы

Даты

1973-01-01—Публикация